Programmierbare Logik

Prozessor liebt FPGA

Fortsetzung des Artikels von Teil 3

Lösungen zum Erstellen von kundenspezifischer Peripherie

Software-Entwickler genießen schon lange die Vorzüge von Entwicklungsplattformen, die von den Prozessorherstellern bereitgestellt werden. Nun helfen Targeted-Design-Plattformen den FPGA-Entwicklern mit ähnlichen Vorteilen. Diese Plattformmethode machte es den Entwicklern einfach, kundenspezifische Peripherie für Embedded- Systeme durch Kombinieren von Silizium, Entwicklungswerkzeugen, wichtiger IP und erweiterbaren Evaluation- Boards zu entwickeln. Targeted- Referenzdesigns vereinen alle diese Elemente und ergeben damit den geeigneten Startpunkt, von dem aus die Entwickler sehr schnell kundenspezifische Systeme generieren können. Die Spartan-6-LXT-Familie enthält eingebaute PCI-Express-Schnittstellen zusammen mit den Ressourcen, die Funktionen zum Generieren von CPUEntlastungs- Hardware für zeitkritische Verarbeitungsaufgaben und kundenspezifische Hardware-Beschleuniger für rechenintensive Funktionen benötigen.

Diese Bausteine enthalten verlustleistungsarme GTP-Transceiver und einen in Silizium integrierten PCIExpress- Funktionsblock, um damit eine Lane (×1) von Gen-1-Schnittstellen zu liefern. Der Endpunkt-Funktionsblock „befreit“ rund 7000 Logikzellen, die sonst für die Implementierung eines Soft-IP-Funktionsblocks benötigt würden. Xilinx hat die Kompatibilität der Spartan-6-LXT-FPGAs mit den elektrischen Anforderungen und Kompatibilitätsbedingungen der V1.1-Basisspezifikation in Compliance-Workshops verifiziert, die von der PCI-SIG veranstaltet wurden, der Organisation, die diese Spezifikation erstellt und betreut. Als ein Ergebnis der Erfüllung dieser strengen Testprozeduren wurden die Spartan-6-LXT-FPGAs und das dazugehörige Evaluierungs-Board SP605 in die Liste der PCI-Express- Integratoren aufgenommen [2].

Entwicklungswerkzeuge

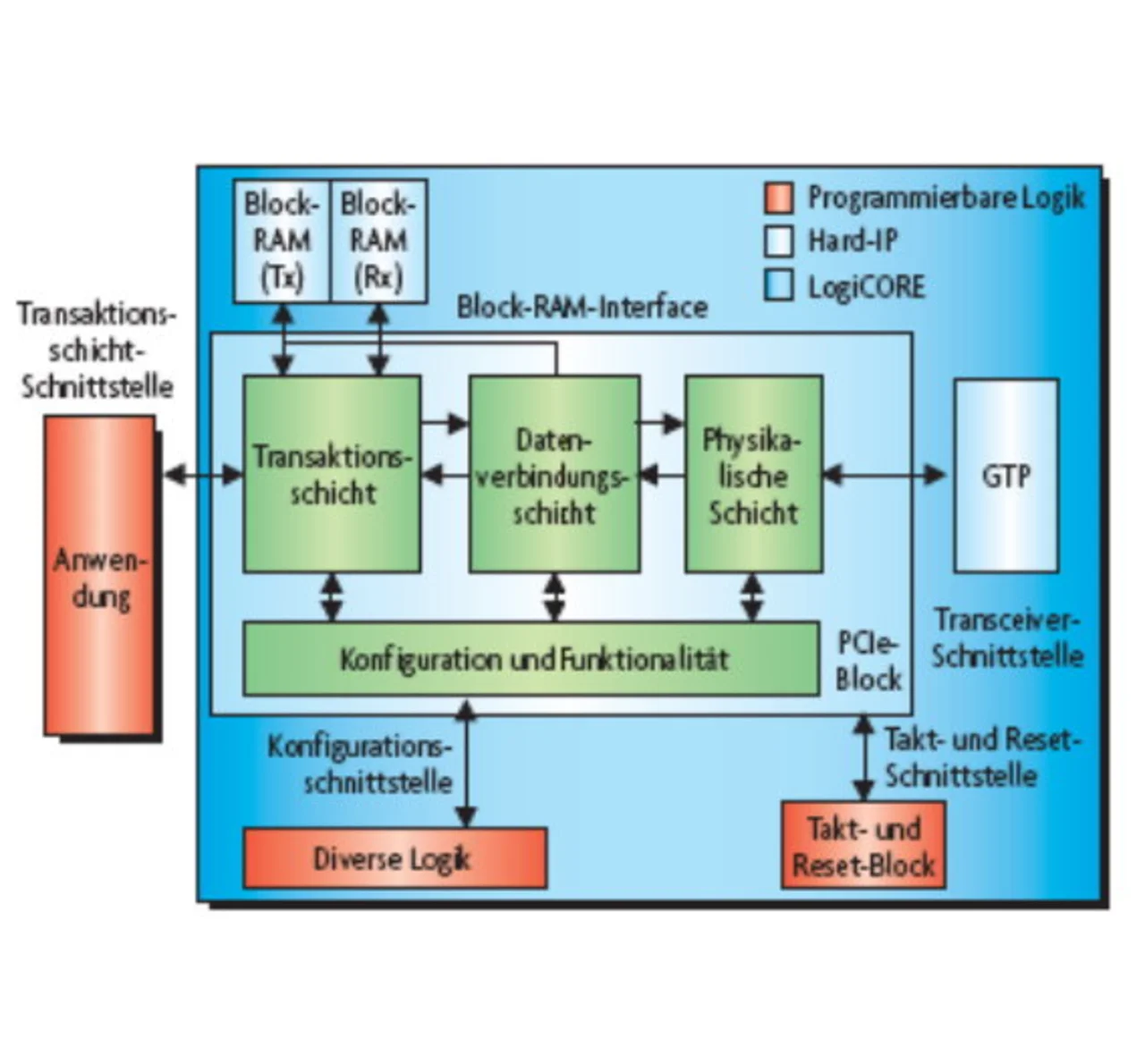

Spartan-6-FPGAs werden von der ISE-Design-Tool-Suite unterstützt, die die Aufgabe des Entwicklers durch die automatische Erzeugung von kundenspezifischer LogiCORE-IP zur Konfiguration der PCI-Express-Endpunkt- Schnittstelle vereinfacht. Der CORE-Generator bietet eine grafische Bedienoberfläche (GUI), um die Entwickler durch den Prozess des Einstellens der Schlüsselparameter des Endpunkts zu führen, einschließlich der konfigurierbaren Parameter der GTP-Transceiver und des PCIExpress- Endpunkt-Funktionsblocks, Block-RAM für die benötigten Puffer und der Takt-Ressourcen. Es enthält ebenfalls die Schnittstelle mit dem applikationsspezifischen Teil des PCI-Express-Endpunkt-Designs (Bild 2).

Das Entwicklungswerkzeug „Chip- Scope Pro Serial I/O“ bietet die Möglichkeit, die Leistungsfähigkeit der Verbindung zu evaluieren und die EQEinstellungen des GTP-Transceivers einzustellen und fein zu justieren. Um die Systementwicklung zu vereinfachen, liefert Xilinx das Evaluierungs- Board SP605, das einen PCIExpress- Steckverbinder beinhaltet, der es einfach macht, die Fähigkeiten des FPGA innerhalb einer Standard-PCPlattform zu überprüfen und dann mit der eigenen Entwicklung zu beginnen. Um es zu vereinfachen, das Evaluierungs- Board mit speziellen Steckverbindern oder zusätzlichen Schaltungen zu erweitern, enthält das SP605 einen FPGA-Mezzanine-Card-Steckverbinder (FMC), um Tochterkarten von Xilinx und Drittanbietern aufzunehmen.

Jobangebote+ passend zum Thema

- Prozessor liebt FPGA

- Kombination von Prozessor und FPGA erhöht Flexibilität

- Integration ist der Schlüssel

- Lösungen zum Erstellen von kundenspezifischer Peripherie

- Targeted-Referenz-Designs