Wenn durch abgekündigte Halbleiterprozesse Lieferengpässe entstehen:

ASIC redesignen

Fortsetzung des Artikels von Teil 3

Redesign eines Mixed-Signal-ASIC

Die größte Herausforderung beim Redesign ist die Neuauflage eines Mixed-Signal-ASIC. Unter einem solchen ASIC versteht man einen kundenspezifischen integrierten Schaltkreis, der sowohl digitale als auch analoge Komponenten beinhaltet. Mixed-Signal-ASICs finden oft Anwendung bei industriellen Messaufgaben. Neben der empfindlichen analogen Signalvorverarbeitung von kleinsten Sensorsignalen sind Baugruppen zur Analog-Digital-Wandlung und zur digitalen Weiterverarbeitung bzw. Speicherung der Messwerte gemeinsam auf einem Chip integriert.

Während digitale ASICs technologieunabhängig entworfen werden und erst mit dem Schritt der Synthese auf eine bestimmte Halbleitertechnologie festgelegt werden, ist dies bei analogen bzw. Mixed-Signal-ASICs nicht möglich. Die elektrischen Eigenschaften eines solchen ASIC werden maßgeblich von den elektrischen Eigenschaften der einzelnen integrierten Bauelemente (MOS-Transistoren, Bipolar-Transistoren, Dioden, Widerstände, Kapazitäten…) bestimmt. Diese Bauelemente-Eigenschaften jedoch sind in großem Maße abhängig von der verwendeten Halbleitertechnologie. So kann eine analoge Schaltung bei gleicher Dimensionierung in zwei unterschiedlichen Halbleitertechnologien unterschiedliche elektrische Eigenschaften aufweisen. Dies kann so weit gehen, dass die Schaltung in einer Technologie die geforderten elektrischen Parameter erfüllt, in einer anderen Technologie dagegen die Anforderungen nicht erreichbar sind.

Beim Redesign eines analogen bzw. Mixed-Signal-ASIC kommt man beim Übergang auf eine neue Halbleitertechnologie oft um eine Umdimensionierung der analogen Baugruppen nicht herum. Auf welche Art und Weise lassen sich nun die Aufwände reduzieren?

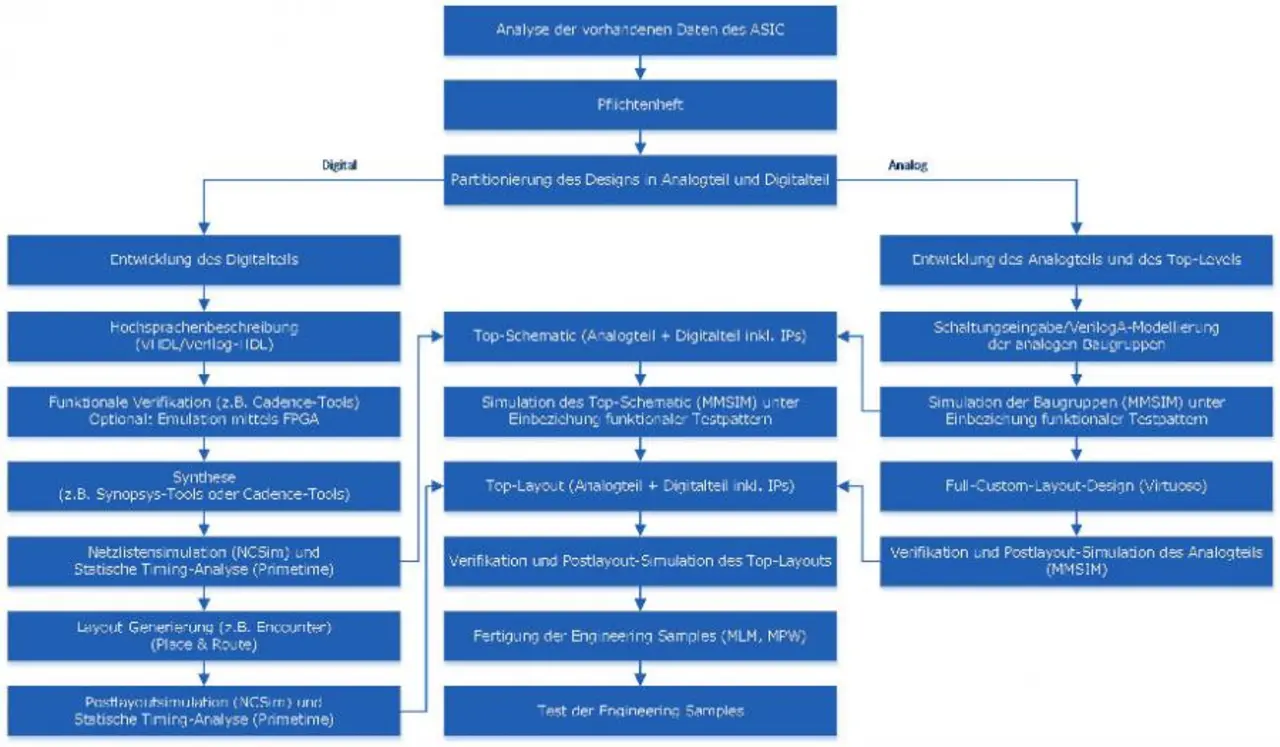

Zunächst wird wieder ein Pflichtenheft erstellt, welches die Grundlage für die zu erreichenden Eigenschaften und technischen Parameter bildet. Dabei wird eine Aufteilung in Analogteil und Digitalteil vorgenommen. Im Rahmen der Pflichtenhefterstellung wird auch die Halbleitertechnologie festgelegt. Sie orientiert sich an den geforderten Parametern der analogen Schaltungen, da diese in größerem Maße von der Halbleitertechnologie abhängen als die Parameter der digitalen Schaltungen. Außerdem wird geprüft, ob sogenannte IPs (Intellectual Properties) in der entsprechenden Technologie eingesetzt werden können. Dies können technologieunabhängige Soft-IPs für den Digitalteil (z.B. Microcontroller, SPI, I²C, UART, RAM) bzw. sogenannte Hard-IPs (z.B. Bandgap-Referenz, Operationsverstärker, AD-Wandler, Power-On-Reset) für den Analogteil sein.

Diese IPs reduzieren zum einen das Entwurfsrisiko, da es sich um bereits praktisch erprobte Schaltungen handelt; zum anderen reduzieren sie auch oft die Entwicklungskosten, da es z.B. wesentlich aufwändiger ist, einen hochauflösenden A/D-Wandler in einer neuen Halbleitertechnologie selbst zu entwerfen, als auf eine bereits im Silizium vorhandene A/D-Wandler-Zelle zurückzugreifen. Ergänzt wird dieses Portfolio durch eigene Hard-IPs in verschiedenen Halbleitertechnologien, welche im Laufe der Jahre durch die Entwicklung vieler Mixed-Signal-ASICs entstanden sind. Analoge Schaltungsteile, die nicht in der Zieltechnologie existieren, müssen per Hand neu entworfen werden. Entsprechende Entwurfswerkzeuge unterstützen die Umsetzung von analogen Schaltungen von einer Technologie in eine andere.

Weiterhin ist für ein Redesign eines Mixed-Signal-ASIC von Bedeutung, ob und in welchem Umfang Speicher (RAM, ROM, OTP, EEPROM, Flash) im Digitalteil verwendet werden. Während viele Halbleiterhersteller RAM in vielen verschiedenen Varianten (Adressbreite, Datenbreite) mittels Memory Compiler generieren können, liegen nichtflüchtige Speicher oft nur als vorgefertigte Zellen mit fest definierter Speichergröße und -organisation vor. Hier muss geprüft werden, ob die im Original-ASIC benötigten Speicher in der neuen Technologie verfügbar sind bzw. ob sie sich durch andere geeignete Speicher ersetzen lassen. So kann z.B. ein EEPROM durch eine Kombination von RAM und OTP ersetzt werden. Während der Programmentwicklung wird das RAM zur Überprüfung der Software-Eigenschaften verwendet. Ist die Programmentwicklung abgeschlossen, wird das Programm einmalig fest in den OTP-Speicher geschrieben und beim Start des ASIC in das RAM geladen. Dies sichert einen schnellen Speicherzugriff, da RAM im Allgemeinen viel schneller als OTP bzw. EEPROM ist – bei gleichzeitiger Unveränderlichkeit des gespeicherten Programms. Das Konzept des neuen ASIC orientiert sich dabei natürlich immer am Original-ASIC.

Beim Entwurf eines Mixed-Signal-ASIC gibt es – je nach vorhandener Entwurfsumgebung bzw. Firmenphilosophie – die Varianten Digital-On-Top und Analog-On-Top. Diese beiden Begriffe bezeichnen die Art und Weise, wie letztlich die oberste ASIC-Hierarchieebene (Top Level) entworfen wird. Bei Digital-On-Top werden in erster Linie digitale Entwurfswerkzeuge verwendet. Analoge Schaltungen werden dabei als Hard-IPs behandelt und in der Gesamtsimulation durch entsprechende Verhaltensmodelle berücksichtigt. Für die Layout-Generierung werden die Analogzellen als sogenannte Abstracts eingebunden. Das heißt, an entsprechenden Stellen im Layout wird Platz für die notwendigen Analogzellen reserviert. Diese Stellen werden nach erfolgtem Place & Route des Digitalteils mit dem Feinlayout der Analogzellen gefüllt und diese an den Digitalteil angeschlossen.

Beim Analog-On-Top-Ablauf werden beim Entwurf des Top Level in erster Linie analoge Entwurfswerkzeuge eingesetzt. Hier wird der Digitalteil als IP behandelt, welcher in Form eines Verhaltensmodells oder als Netzliste eingebunden wird. Das Gesamtlayout wird hier z.B. mit dem Tool Virtuoso entworfen, welches auch den Layoutentwurf auf der untersten Bauelementeebene (mit sogannnten „primitive devices“, also Transistoren, Widerstände, Kapaziäten, Induktivitäten…) erlaubt. Letzterer ist der im MAZeT bevorzugte Weg für den Entwurf und das Redesign von Mixed-Signal-ASICs. Eine abschließende Verifizierung (Layout vs. Schematic) sichert in beiden Fällen die Richtigkeit des Top-Layouts im Vergleich zum Top-Schematic.

Sind alle Voraussetzungen für ein Redesign erfüllt, dann folgt die Entwicklung. Der Digitalteil wird gemäß dem digitalen Entwurfsablauf (Bild 4, Verzweigung Digital), der Analogteil entsprechend dem Entwurfsablauf für analoge Schaltungen (Bild 4, Verzweigung Analog) realisiert. Nach dem Zusammenfügen beider Teile (Top Level) – gemeinsam mit dem sogenannten Pad-Ring (die Anschlüsse des ASIC) – erfolgt eine abschließende Verifikation des kompletten Chips. Im Ergebnis entsteht der GDS2-Datensatz, welcher die Grundlage für die Fertigung des Maskensatzes beim Halbleiterhersteller und der Engineering Samples ist.

Nach dem Aufbau der Engineering Samples im Gehäuse werden diese unter Verwendung des originalen Testprogramms und der originalen Test Patterns getestet. Parallel dazu testet der Kunde das neue ASIC funktional in seiner Applikation. Sind die ursprünglichen Test Patterns und/oder das Testprogramm nicht mehr vorhanden, wird beides auf der Grundlage der Dokumentation des Original-ASIC neu entwickelt. Der Nachweis, dass das neue ASIC das gleiche Verhalten wie das Original-ASIC zeigt, erfolgt letztlich in der Anwenderschaltung des Kunden. Aber auch hier kann MAZeT entsprechende Unterstützung geben. Auf Kundenwunsch wird eine Inbetriebnahme-Leiterplatte entwickelt, welche das Original-ASIC und das neue ASIC beinhaltet und ein vergleichendes Testen der elektrischen Funktionen ermöglicht.

Jobangebote+ passend zum Thema

- ASIC redesignen

- Realisierungswege für ein Redesign

- Maskenprogrammierbare bzw. Standard-Zell-Technologie

- Redesign eines Mixed-Signal-ASIC

- Redesign-Beispiel eines Mixed-Signal-ASIC