Wenn durch abgekündigte Halbleiterprozesse Lieferengpässe entstehen:

ASIC redesignen

Fortsetzung des Artikels von Teil 2

Maskenprogrammierbare bzw. Standard-Zell-Technologie

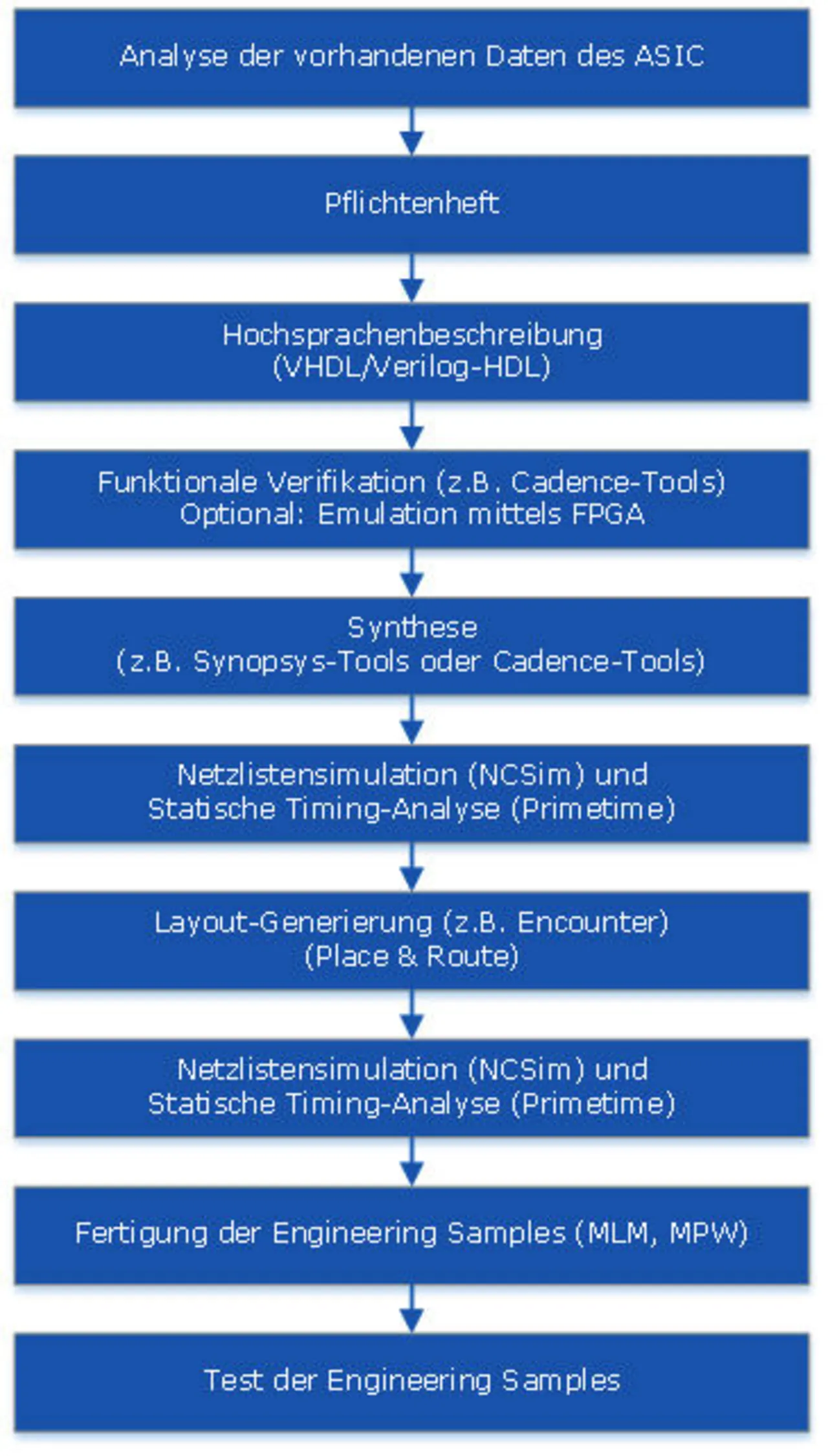

Bild 2 zeigt den Entwurfsablauf für ein digitales ASIC. Dieser Ablauf kommt ebenso beim Redesign eines digitalen ASIC zur Anwendung. Der entscheidende Unterschied zwischen Neuentwurf und Redesign besteht darin, dass beim Redesign bereits auf eine mehr oder weniger umfangreiche Datenbasis zurückgegriffen werden kann.

Am Beginn der Entwicklung steht die Analyse des vorhandenen Datenbestandes. Darauf aufbauend wird ein Pflichtenheft erarbeitet, welches die Grundlage für das RTL-Modell (Register Transfer Level) des ASIC ist. Je nach vorhandenem Datenbestand des Original-ASIC werden an dieser Stelle auch bereits vorhandene Hochsprachenmodule eingebunden. Liegen die originalen Module in einer anderen Hochsprache als VHDL oder Verilog-HDL vor (z.B. ABEL), werden diese in VHDL oder Verilog-HDL umgesetzt. Die funktionale Verifikation des RTL-Modells erfolgt per Netzlistensimulation unter Verwendung eventuell vorhandener Test Patterns bzw. Testumgebung.

Eine Emulation per FPGA beschleunigt die Verifikation. Man erreicht damit eine höhere Testabdeckung, weil mehr Testfälle ausgeführt werden können. Mittels Synthese wird aus dem RTL-Modell eine nun technologiebezogene Netzliste erzeugt. Diese wird wiederum mittels Simulation und statischer Timing-Analyse geprüft. Diese Netzliste bildet den Ausgangspunkt für die Layout-Generierung, welche oft vom Halbleiterhersteller selbst ausgeführt wird. Die Extraktion und Verifikation der Postlayout-Netzliste aus dem Layout sichert die Richtigkeit und die Übereinstimmung des Layout mit dem ursprünglichen Modell. Wurden alle Prüfschritte erfolgreich durchlaufen, wird die Fertigung der Engineering Samples freigegeben.

Nach dem Aufbau der Chips im Gehäuse und dem Test der Engineering Samples mit dem ursprünglichen Testprogramm und den zugehörigen originalen Test Patterns sowie der funktionellen Erprobung der Engineering Samples in der Kundenapplikation kann die Freigabe zur Serienproduktion erfolgen.

ASIC-Redesign mittels Ersetzung durch ein CPLD/FPGA

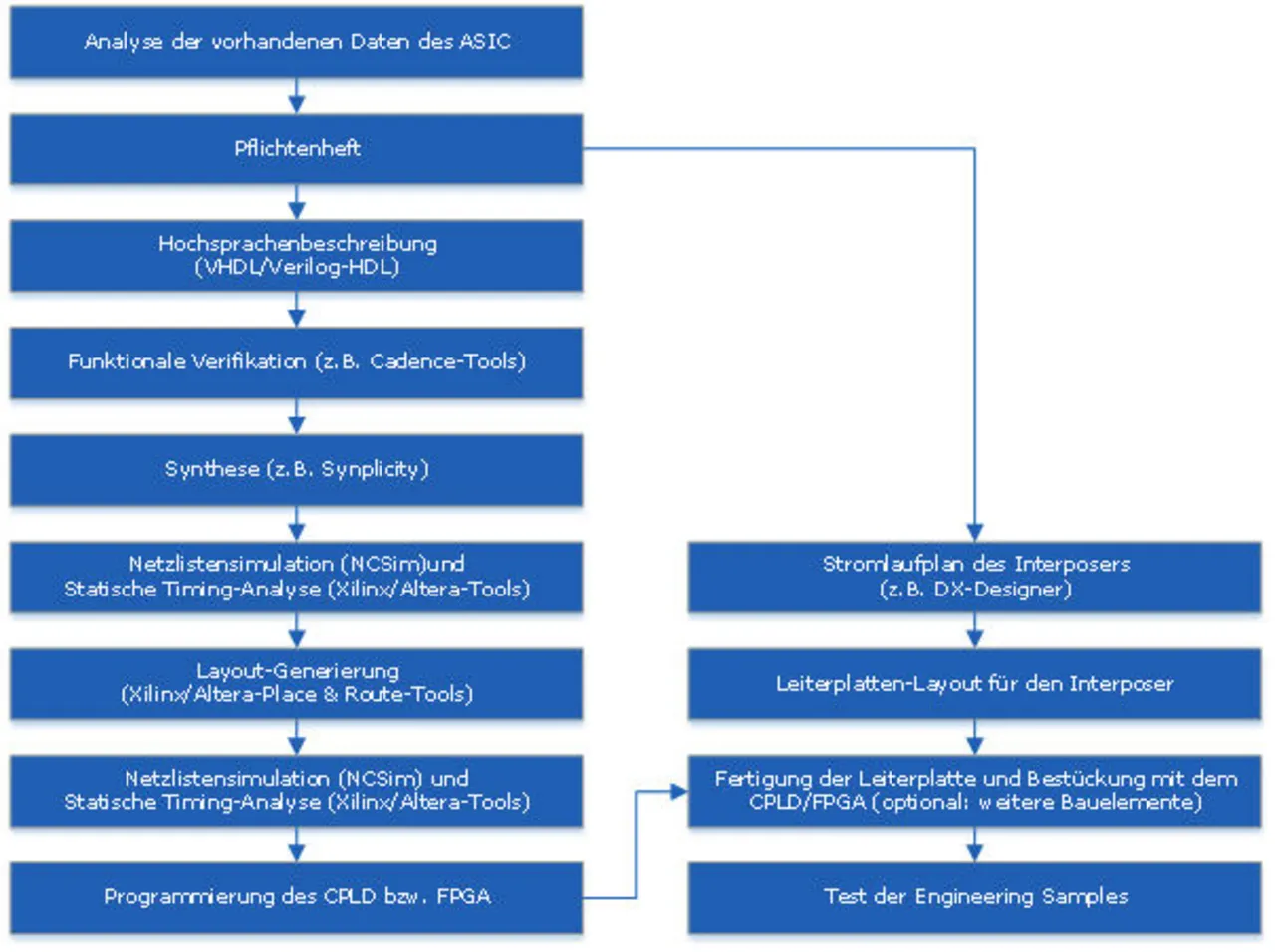

Wenn die Voraussetzungen für einen Entwurf in einer Gate-Array- oder Standard-Zell-Technologie nicht gegeben sind, dann besteht die Möglichkeit, die Funktionen des ASIC mittels CPLD oder FPGA nachzubilden. Der Entwurfsablauf (Bild 3) ist dabei ähnlich dem, der auch beim Redesign eines maskenprogrammierbaren ASIC angewendet wird. Jedoch sind hier die Entwurfswerkzeuge mehr auf die Hersteller der CPLDs bzw. FPGAs ausgerichtet. Das heißt, der Hersteller der programmierbaren Bausteine liefert auch die entsprechenden Entwurfswerkzeuge für die Simulation und die Programmierung.

Da sich Gehäuse und Anschlussschema eines solchen programmierbaren Bauelementes im Allgemeinen von dem des Original-ASIC unterscheiden und man hier auch nicht die freie Wahl hat, wird ein Leiterplattenträger (Interposer) zur Umsetzung des Anschlussbildes auf das Anschlussbild des Original-ASIC entworfen und gefertigt. Der Chip wird dann mittels COB-Technik (Chip on Board) montiert und angeschlossen. Eine lichtundurchlässige Vergussmasse schützt den Chip vor mechanischen Beschädigungen und vor ungewollter Beeinflussung der elektrischen Funktionen durch Umgebungslicht. Das Anschlussbild des Leiterplattenträgers entspricht dann dem des Original-ASIC, sodass das neue ASIC ohne Neuentwurf der Applikationsleiterplatte eingesetzt werden kann.

Jobangebote+ passend zum Thema

- ASIC redesignen

- Realisierungswege für ein Redesign

- Maskenprogrammierbare bzw. Standard-Zell-Technologie

- Redesign eines Mixed-Signal-ASIC

- Redesign-Beispiel eines Mixed-Signal-ASIC