Wenn durch abgekündigte Halbleiterprozesse Lieferengpässe entstehen:

ASIC redesignen

Fortsetzung des Artikels von Teil 1

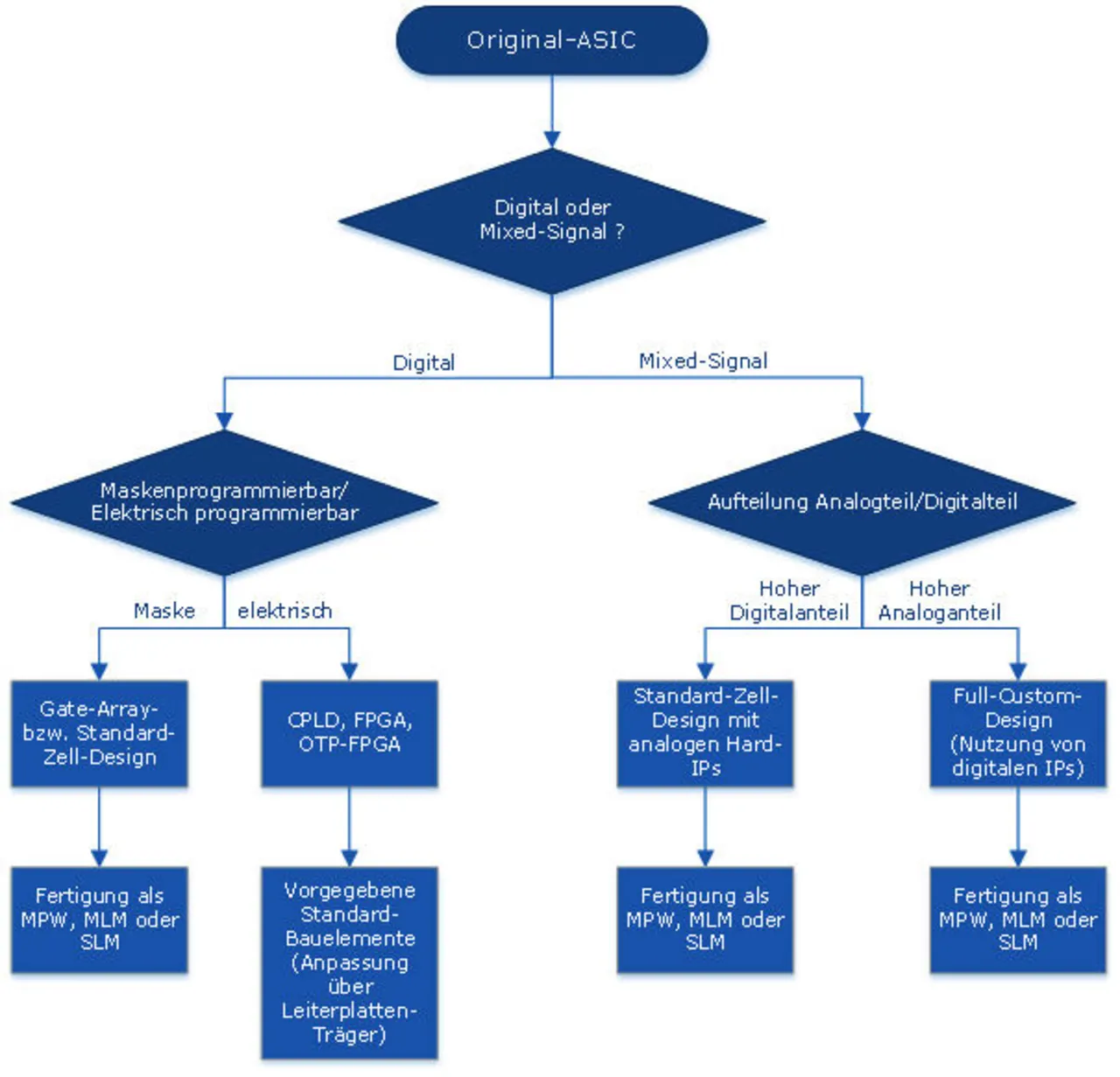

Realisierungswege für ein Redesign

Der Weg zur Wiederbelebung eines ASIC hängt von vielen Faktoren ab: Grundsätzlich kann man aber zwischen dem Redesign eines rein digitalen ASIC und dem eines sogenannten Mixed-Signal-ASIC unterscheiden. Ein Mixed-Signal-ASIC beinhaltet neben digitalen Baugruppen auch einen mehr oder weniger großen Analogteil. Während digitale Schaltkreise heute mit Hochsprachen (z.B. Verilog, VHDL) beschrieben werden, herrscht bei der Entwicklung analoger bzw. analog/digitaler Schaltkreise der Entwurf auf Schaltplan-Ebene (Schematic) vor.

Damit ergeben sich auch unterschiedliche Wege beim Redesign solcher ASICs. Bild 1 zeigt eine Übersicht über die möglichen Vorgehensweisen, die im Folgenden näher erklärt werden.

Redesign eines digitalen ASIC

Für das Redesign eines digitalen ASIC bieten sich zwei Wege an:

- Umsetzung auf ein maskenprogrammierbares Gate Array bzw. ein Standard-Zell-Design

- Umsetzung auf einen programmierbaren Logikbaustein

Ein vorhandenes Digitaldesign kann bei entsprechender Bearbeitung auf eine beliebige maskenprogrammierbare ASIC-Technologie oder ein Standard-Zell-Design umgesetzt werden. Dieses Verfahren bietet sich an, wenn die jährlich benötigte Stückzahl 5000 überschreitet bzw. wenn die Anschlusskompatibilität zum Original-ASIC unbedingt erforderlich ist.

Die Umsetzung auf eine Gate-Array-Technologie hat dabei gegenüber dem Standard-Zell-Entwurf den Vorteil, dass hier nur die Metall-Masken entworfen werden müssen, die NRE-Kosten (Non-Recurring Engineering) also geringer sind. Gate-Array-Technologien weisen ein Optimum zwischen NRE-Kosten und Serienpreis für kleine Stückzahlen auf. Dafür ist man bezüglich der Realisierung der logischen Funktionen auf vorgefertigte Master angewiesen, die in bestimmten Größenabstufungen vom Halbleiterhersteller angeboten werden. Im ungünstigen Fall kann es dabei dazu kommen, dass ein vorhandenes Design gerade nicht mehr in den kleineren Master passt und der nächst größere Master ausgewählt werden muss, dessen Chipfläche und damit auch der Serienpreis aber wesentlich größer sind.

Diesen Nachteil umgeht man mit einem Standard-Zell-Design, welches allerdings größere NRE-Kosten aufweist, da hier alle benötigten technologischen Ebenen (und damit Masken) entworfen und gefertigt werden müssen (Single-Layer Mask Service oder SLM). Dafür kann das ASIC dann auf minimale Chipfläche und damit geringen Serienpreis optimiert werden. Dieser Weg bietet sich also bei hohen jährlichen Stückzahlen an. Zur Kostenreduzierung bei der Herstellung des Maskensatzes für die Engineering Samples bieten viele Halbleiterhersteller den Multi-Layer Mask Service (MLM) an. Dabei werden mehrere technologische Ebenen auf jeweils eine physische Maske projiziert und die Maskenanzahl und damit der Preis für den Maskensatz reduziert.

Sehr kleine Stückzahlen (<100) lassen sich mit dem sogenannten MPW-Service fertigen. Hier werden vom Halbleiterhersteller mehrere Kundenprojekte auf einem gemeinsamen Silizium-Wafer platziert. Man teilt sich also sowohl die Wafer-Kosten als auch die Fertigungskosten. Viele Halbleiterhersteller bieten MPW-Services zum Pauschalpreis an.

Vor allem bei geringen Stückzahlen kann es jedoch sinnvoll sein, das vorhandene Digitaldesign auf einem programmierbaren Logikbaustein zu realisieren. Hier kommen dann Standard-Bauelemente wie CPLDs (Complex Programmable Logic Device), nichtflüchtige FPGAs oder OTP-FPGAs (One-Time Programmable) zur Anwendung. Im Allgemeinen wird mit dieser Methode jedoch keine Anschlusskompatibilität zum Originalbauelement zu erreichen sein. Der Nachteil wären entsprechende Folgekosten für die Anpassung der Leiterplatten beim Kunden.

Abhilfe schafft hier ein sogenannter Interposer (auch Redistribution Layer oder Zwischenverdrahtungsträger). Dabei wird das Anschlussbild des Logikbausteins mittels eines Leiterplattenträgers (z.B. FR4) auf das Anschlussbild des Original-ASIC umgesetzt. Dieser Träger ermöglicht außerdem die Integration weiterer Schaltungskomponenten wie z.B. Stützkondensatoren oder Ferrit-Beads. Welcher Weg letztlich der am besten geeignete ist, wird gemeinsam mit dem Kunden abgestimmt.

Jobangebote+ passend zum Thema

- ASIC redesignen

- Realisierungswege für ein Redesign

- Maskenprogrammierbare bzw. Standard-Zell-Technologie

- Redesign eines Mixed-Signal-ASIC

- Redesign-Beispiel eines Mixed-Signal-ASIC