Taktverteilung

Additiven Jitter verstehen, messen und minimieren

Fortsetzung des Artikels von Teil 1

Was beeinflusst das Jitter-Verhalten?

Welche Faktoren beeinflussen die Jitter-Verhalten, wenn ein Puffer zu einem Taktbaum hinzugefügt wird? Auch beim Lesen von Datenblättern spielt dies eine wichtige Rolle. Die Beurteilung des Jitter-Verhaltens durch den Hersteller beeinflusst die Zahl im Datenblatt. So zeigen zwei Puffer mit ähnlichem Verhalten sehr unterschiedliche Jitter-Spezifikationen, wenn ein Anbieter eine langsamere Anstiegsgeschwindigkeit (Slew Rate) verwendet als der andere.

Jobangebote+ passend zum Thema

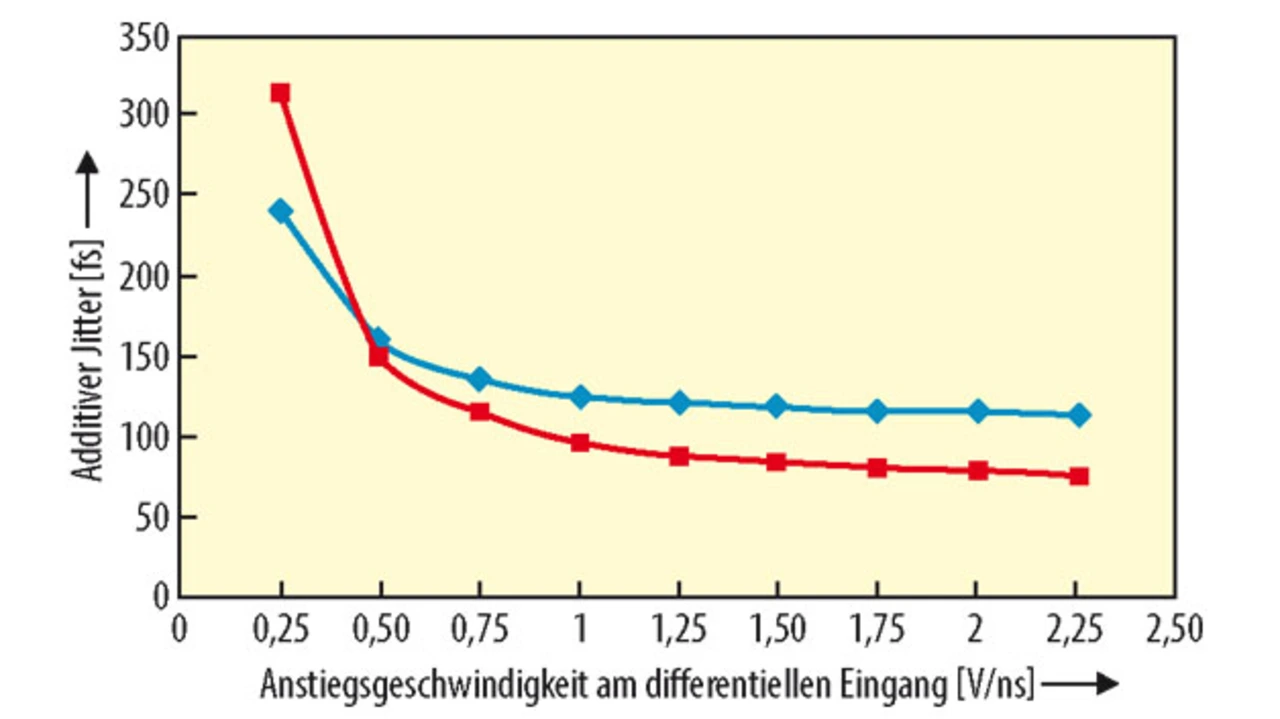

Bild 1 zeigt den additiven Jitter zweier verschiedener Taktpuffer über der Anstiegsgeschwindigkeit am Eingang. In beiden Fällen nimmt der Wert ab, wenn die Anstiegsgeschwindigkeit zunimmt. Die rote Kurve zeigt einen geringeren additiven Jitter. Allerdings ist der zugehörige Puffer empfindlicher und erreicht bei geringer Anstiegsrate schlechtere Werte, z.B. bei niederfrequenten Sinus-Signalen oder CMOS-Takten. Die Grafik zeigt, wie wichtig es ist, den additiven Phasen-Jitter mit der Anstiegsrate und dem in der Anwendung verwendeten Wert zu vergleichen.

Bandbreite, über die integriert wird

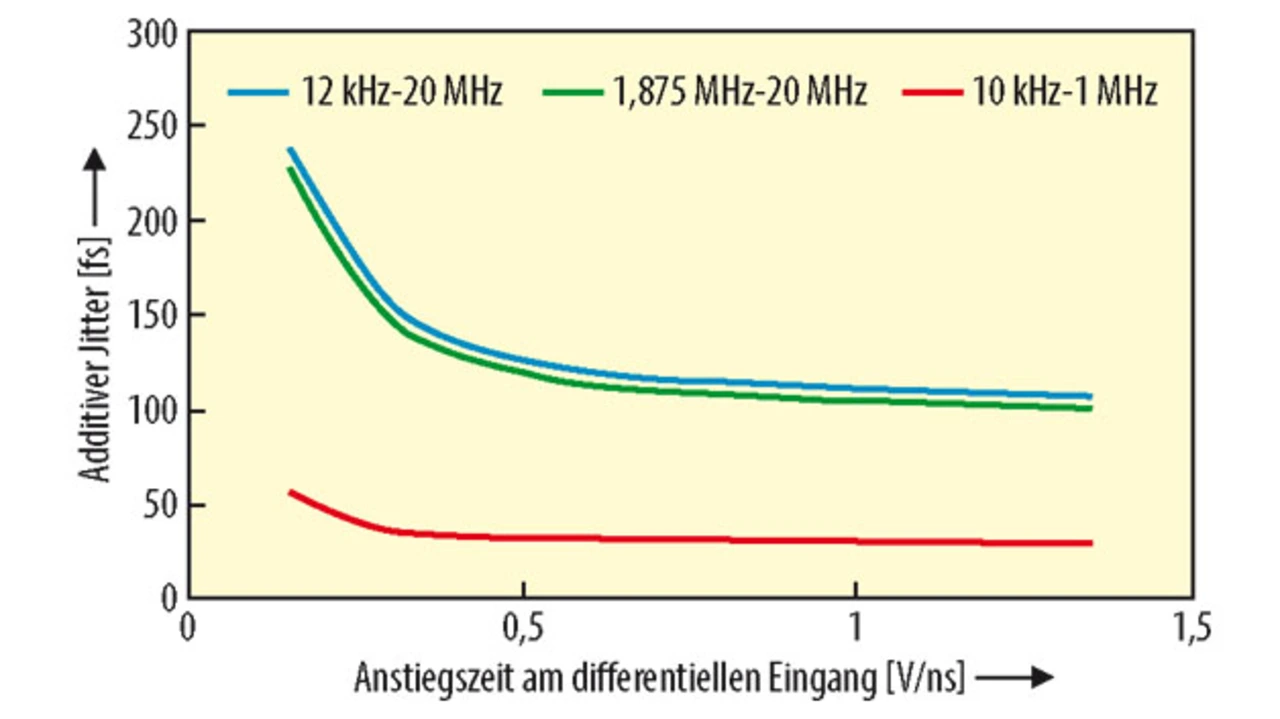

Die Bandbreitenvorgabe, über die integriert wird, um den Jitter zu berechnen, nimmt ebenfalls Einfluss auf das gemessene Jitter-Verhalten. Die Bandbreite, die von Interesse ist, hängt von der Anwendung ab. Bei Zweifeln sollte man immer die gleiche Bandbreite verwenden, wenn man Vergleiche vornimmt. Gängige Werte für die Bandbreite bei der digitalen Datenkommunikation liegen zwischen 12 kHz und 20 MHz. Wie bei den meisten Filtern führt eine engere Bandbreite zu einem geringeren und damit besseren Jitter-Wert.

Bild 2 zeigt die Ergebnisse mit 156,50 MHz Eingangsfrequenz und drei Integrationsbereichen: 12 kHz bis 20 MHz, 1,875 MHz bis 20 MHz und 10 kHz bis 1 MHz. Die Grafik zeigt, dass optimale Ergebnisse mit 0,6 V/ns oder schnelleren Anstiegsraten erreicht werden. Sie liefert auch ein Beispiel, wie weit der additive Jitter aufgrund der Bandbreite abweichen kann.

Ausgangsfrequenz

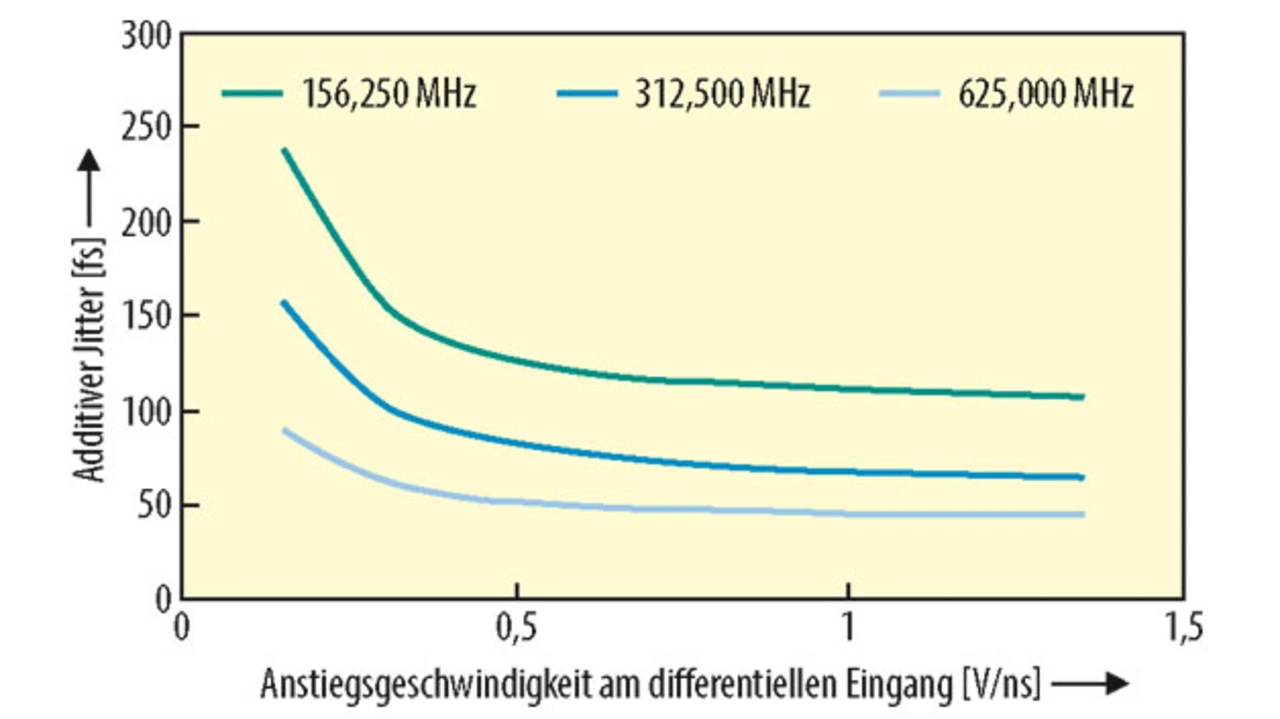

Die Ausgangsfrequenz hat erheblichen Einfluss auf den additiven Jitter. Höhere Frequenzen führen meist zu einem besseren Jitter-Verhalten. Wenn die Frequenz bekannt ist, hilft ein Blick ins Datenblatt, um den entsprechenden Wert nahe dieser Frequenz zu finden.

Bild 3 zeigt den additiven Phasen-Jitter ein und desselben Taktpuffers bei drei verschiedenen Ausgangsfrequenzen. Der Jitter ist bei höheren Ausgangsfrequenzen um den Faktor 20 log (f1/f2) geringer bzw. bei doppelter Frequenz um 6 dB geringer. Während die integrierte Phasenrauschleistung konstant ist, ist der Phasen-Jitter geringer, da dieser aus dem 1/f-Fachen des integrierten Phasenrauschens abgeleitet ist. Die Ausgangsfrequenz sollte beim Vergleich von Bausteinen über das Datenblatt ebenfalls berücksichtigt werden.

Versorgungsspannung

Die Versorgungsspannung kann den additiven Jitter ebenfalls beeinflussen, da viele Taktpuffer bei verschiedenen Spannungen wie 1,8 V, 2,5 V oder 3,3 V arbeiten. Bei der hier verwendeten Puffer-Baureihe gab es nur sehr geringe Jitter-Abweichungen. Am Besten ist es, den Hersteller des Taktpuffers zu kontaktieren oder, soweit die entsprechende Ausrüstung vorhanden ist, das Jitter-Verhalten selbst zu charakterisieren.

Die Bilder 1 bis 3 zeigen, wie sich das Phasenrauschen durch eine höhere Anstiegsgeschwindigkeit am Eingang optimieren lässt. Der Eingang eines Taktpuffers schaltet bei einer Spannung, die idealerweise konstant ist, in der Realität aber innerhalb eines schmalen Bereichs davon abweicht. Aufgrund dieser Abweichungen beim Schalten ändert sich auch der Flankenzeitpunkt, was zu mehr Jitter führt. Eine schnellere Anstiegsrate verkürzt also auch die Zeit, in welcher sich die Spannung am Eingang in diesem Zustand befindet, und minimiert den Einfluss auf das System, was dessen Verhalten optimiert.

- Additiven Jitter verstehen, messen und minimieren

- Was beeinflusst das Jitter-Verhalten?

- Fazit und Empfehlung