Datenwandler

ADCs richtig takten

Fortsetzung des Artikels von Teil 1

Auswirkungen des Jitters

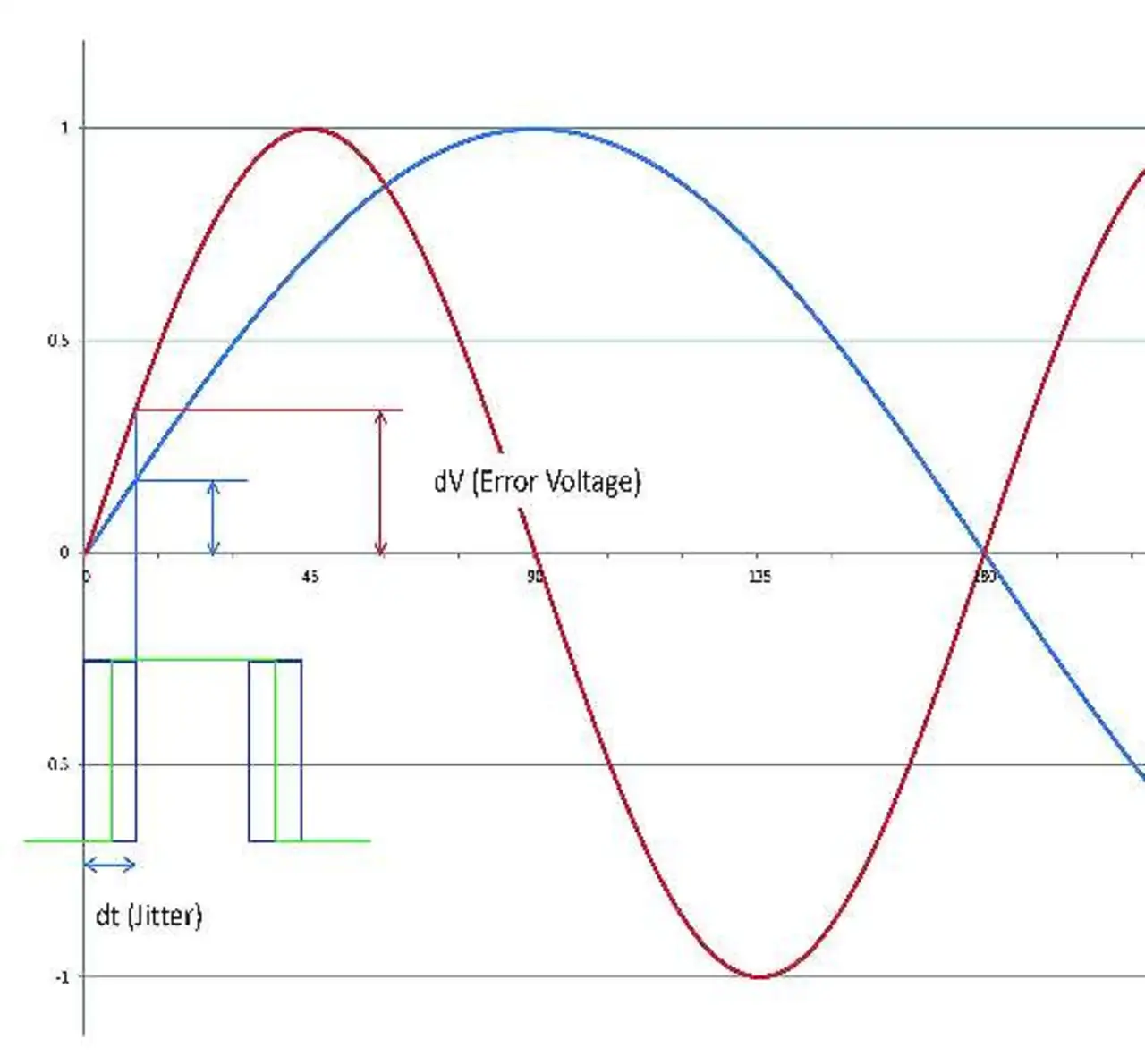

Je schneller und steiler die zu messenden Signale sind, umso mehr geht ein Jitter in den Fehler der Wandlung ein (siehe Bild 5). Dort sind bei gleichem Taktsignal zwei verschiedene Eingangssignalformen dargestellt: sin(x) in blau und sin(2x) in rot. Bei gleichem Jitter (dt) wird der Betrag der Fehlerspannung (dV) bei höherer Frequenz des Signals größer.

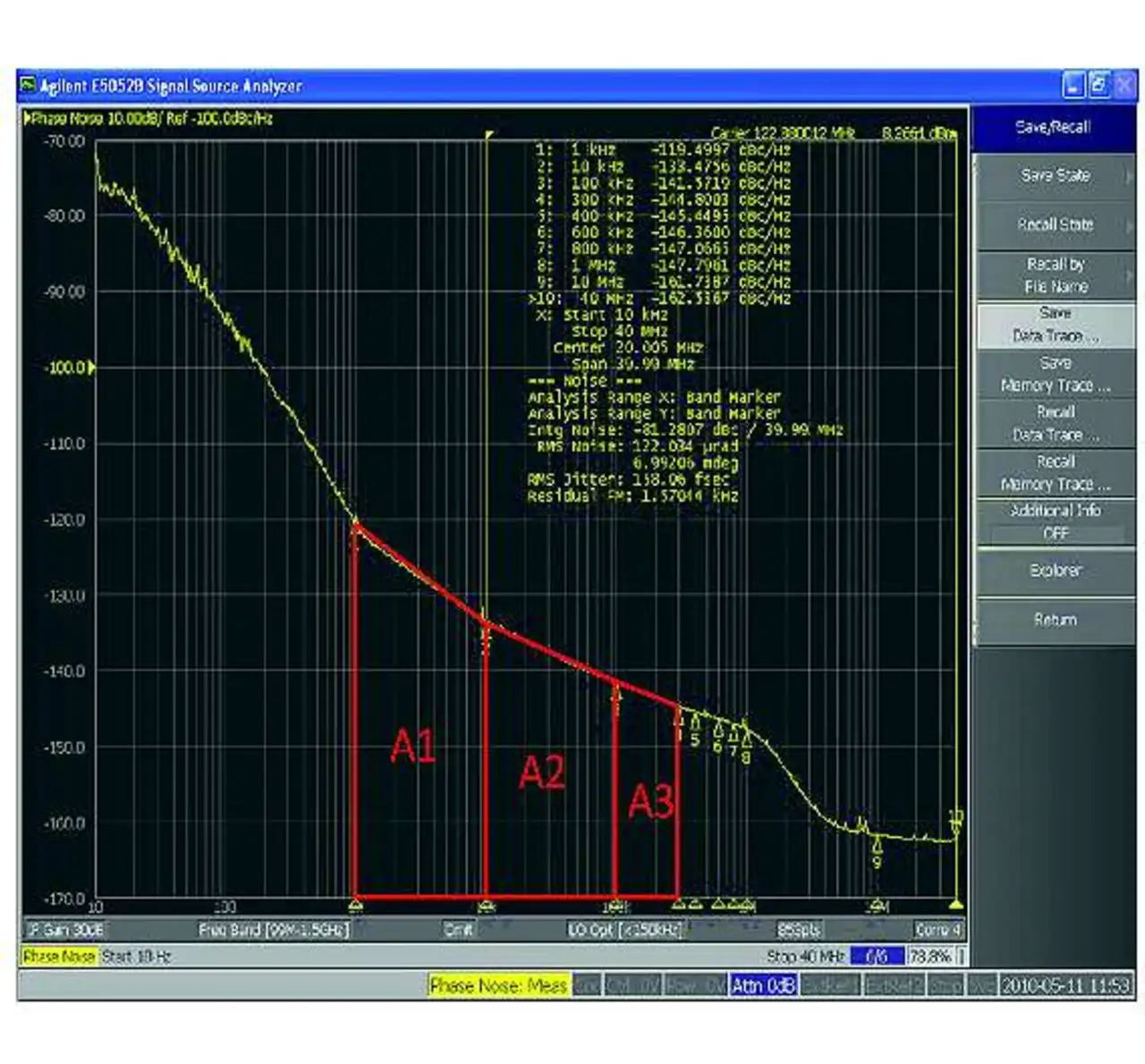

In Datenblättern von Takterzeugern wie PLLs (Phase-locked Loop) oder DDS-Bausteinen findet man häufig die Angabe des Phasenrauschens. Um das Phasenrauschen (dBc/Hz) in die Zeitdomäne Jitter (in Sekunden) umzurechnen, muss man schrittweise integrieren. Hierzu wird jeweils ein Abschnitt der typischerweise logarithmisch aufgetragenen Frequenz betrachtet.

Jobangebote+ passend zum Thema

Die Fläche wird mit Hilfe der Formel für die Flächenberechnung des Trapezes ermittelt.

Anschließend lassen sich die verschiedenen Abschnitte aufaddieren. Diesen Wert kann man anschließend in Jitter umrechnen. Der Term fOSC sei hierbei die Frequenz, mit welcher der Wandler betrieben wird (Taktfrequenz).

Bild 6 zeigt ein Diagramm des Signalanalysators »E5052B« von Agilent für eine Frequenz von 122,88 MHz und einen Bereich von 40 MHz.

An dieser Abbildung kann man anhand der tabellarischen Auflistung der Messpunkte recht einfach mithilfe der Gleichungen (4) und (5) das Phasenrauschen in Jitter umrechnen.

Bei modernen Messgeräten, wie dem hier verwendeten, lässt sich der Jitter für den betrachteten Bereich auch direkt am Plot ablesen (in diesem Beispiel 158 fs). Um das Phasenrauschen zu minimieren, muss als erstes die richtige Gate-Struktur gewählt werden. In Tabelle 1 sind einige Strukturen im Vergleich zu sehen.

| Gate-Typ | Jitter |

|---|---|

| FPGA |

33 ps bis 50 ps |

| 74LS00 |

4,94 ps |

| 74HCT00 | 2,20 ps |

| 74ACT00 | 0,99 ps |

| MC100EL16 (PECL) | 0,70 ps |

| AD951x, AD952x Clock Generator | 0,18 ps bis 0,24 ps |

| ADCLK94x/95x Clockbuffer | 0,05 ps bis 0.075 ps |

Tabelle 1: Gate-Strukturen und der zugehörige Jitter (beim FPGA sind die Laufzeitunterschiede nicht berücksichtigt, die durch internes Routing oder Eingangsstrukturen verursacht werden)

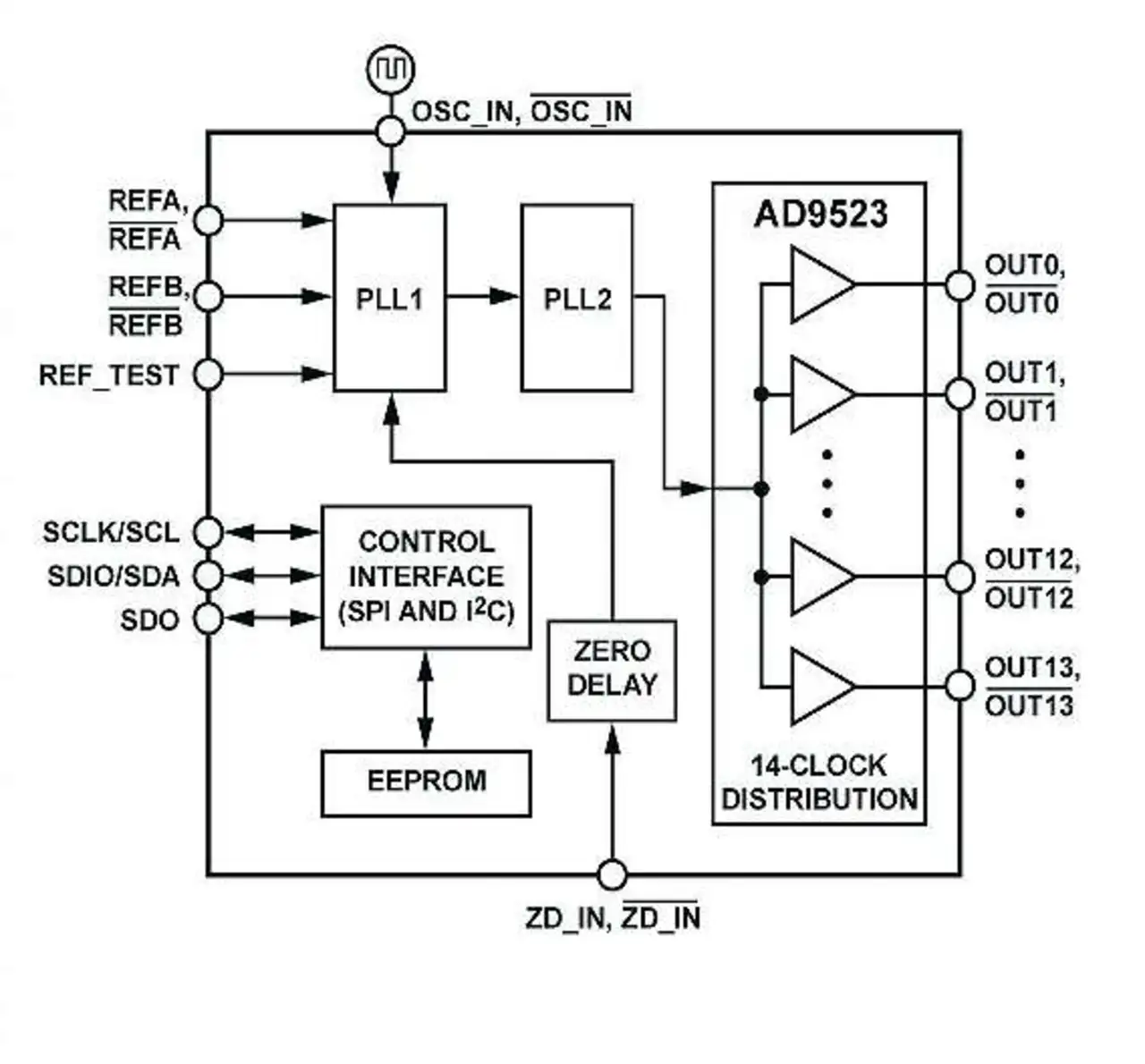

Ein FPGA, der häufig zum Auslesen schneller Wandler eingesetzt wird, eignet sich nicht, um den Takt zu erzeugen. Eine sehr gute, flexible und günstige Variante ist die Verwendung der Takterzeugungsbausteine der Familie »AD952x«, die einen Jitter von 240 fs und weniger erzeugen (Bild 7). Sie verfügen über zwei kaskadierte Phase-locked-Loops (PLLs), zwei Referenzeingänge und benötigen einen externen VCXO (spannungsgesteuerter Quarzoszillator).

Es gibt verschiedene Möglichkeiten, um das Phasenrauschen einer Takterzeugung zu reduzieren. Die günstigste Variante nutzt einen Frequenzteiler. Dies setzt eine Taktquelle mit einer hohen Ausgangsfrequenz voraus. Der Vorteil des Frequenzteilers ist der günstige Preis und die Möglichkeit, Teiler mit mehreren Ausgängen einzusetzen. Um die bestmögliche Leistung zu erreichen, sollte ein Bandpassfilter zwischen Takterzeugung und Teiler eingefügt werden.

Bei dem Einsatz eines Teilers ist zu beachten, dass sich der Jitter der einzelnen Bauteile, wenn diese statistisch unabhängig sind, mit der pythagoreischen oder geometrischen Summe (Wurzel aus der Summe der Quadrate) erhöht. Fünfprozentige LC-Bandpassfilter reduzieren den Jitter noch weiter als die Lösung mit Frequenzteilern. Der Nachteil dieser Lösung ist die Begrenzung des Taktverhältnisses auf 50% und die Begrenzung der Frequenz auf den Durchlassbereich des Filters.

Außerdem sind entsprechend hochwertige Filter deutlich teurer als Frequenzteiler. Die besten Werte lassen sich mit entsprechenden Kristallfiltern erreichen, allerdings ist das die kostenintensivste Variante. Die Bandbreite wird auch hier auf den Durchlassbereich des Filters reduziert, und die übertragene Leistung ist sehr begrenzt. Wird eine größere Leistung übertragen als die, für die der Filter spezifiziert ist, kehrt sich der Effekt der Reduzierung des Jitters ins Gegenteil um.

Bei der Spannungsversorgung der Takterzeuger sollten Anwender unbedingt die Vorschläge des Datenblattes beachten. Vergleichsmessungen an einer PLL vom Typ »ADF4350« mit verschiedenen LDOs haben ergeben, dass sich der Jitter durch den Einsatz eines Ultra-Low-Noise-LDOs (z.B. »ADP150«) um bis zu 30% reduzieren lässt. Besitzt ein Baustein mehrere Taktausgänge, ist es sinnvoll, diese einzeln zu versorgen, um das Übersprechen zu verringern.

Ebenso sollten VCO und PLL getrennt versorgt werden. Wichtig ist auch eine gute Masseverbindung, am besten auf einer getrennten Lage im Board, mit Vias direkt an den Masseanschlüssen der jeweiligen Schaltkreise. Dadurch lassen sich unterschiedliche Spannungspotenziale auf den Rückleitungen zum Spannungsregler vermeiden.

- ADCs richtig takten

- Auswirkungen des Jitters

- Wahl des Taktgenerators