Der schnellste ARM-Mikrocontroller

150 MHz für den Cortex-M3

Fortsetzung des Artikels von Teil 1

Zwei bemerkenswerte Peripherie-Elemente

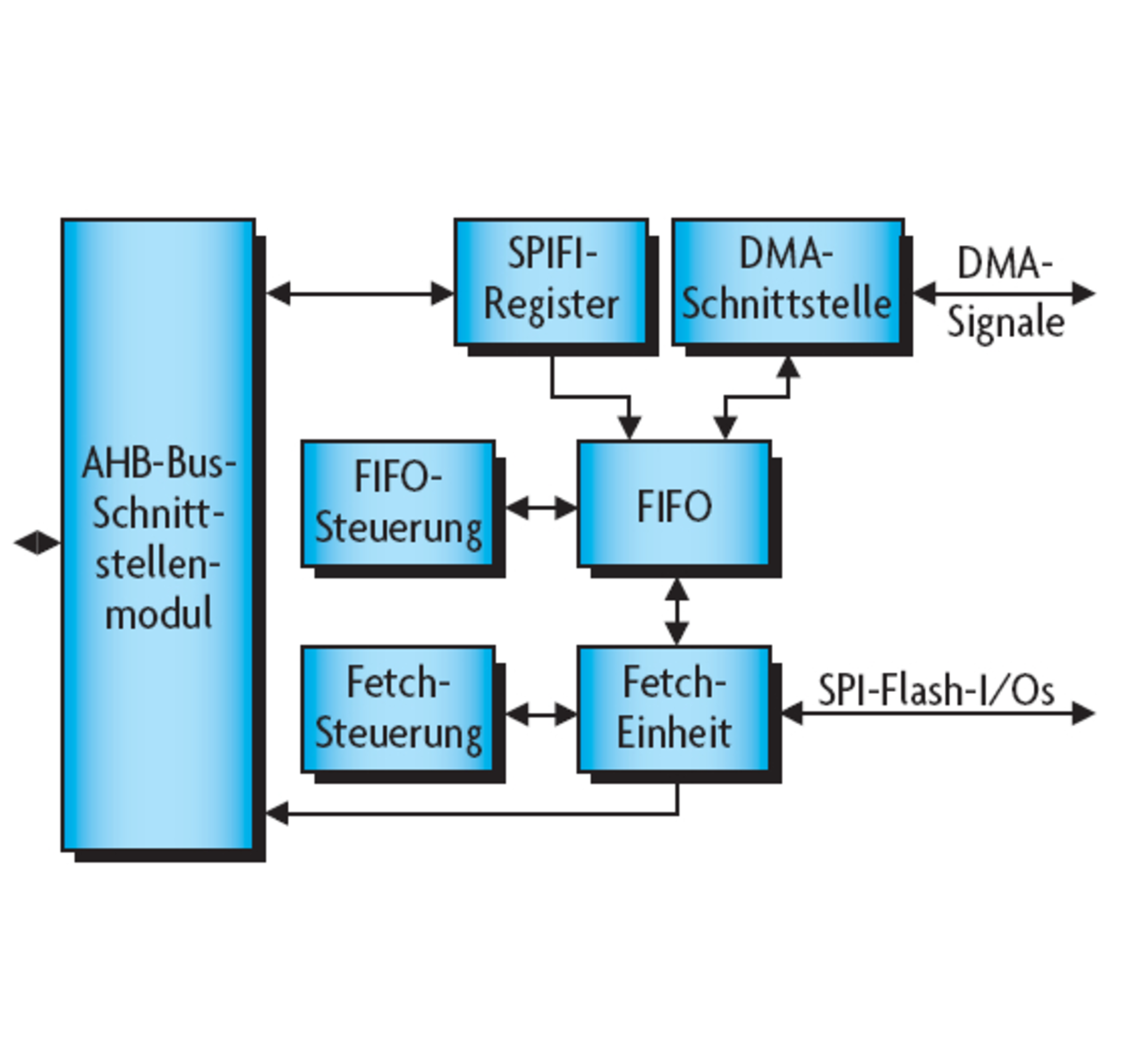

Mit dem LPC1800 wurden auch zwei neue Peripherieelemente eingeführt. Das erste ist eine SPI-Schnittstelle, die eine Quad-Mode-Operation für 8-Pin- Flash-ICs ermöglicht (Bild 2). Nach Abarbeitung des Handshake-Protokolls werden die Pins der SPI-Schnittstelle in vier Datenleitungen umkonfiguriert, die jeweils Datentransfers mit 80 Mbit/s ermöglichen – zusammen also 40 Mbyte/s.

Damit kann der Inhalt des gesamten Flash-Speichers bei einem Kaltstart in 1/3 bis 1/100 s in den SRAM-Speicher auf dem Chip bzw. externes RAM transferiert werden. Diese Werte sind freilich nur dann erzielbar, wenn 256 Bytes pro Fetch gelesen werden, und sinken mit weniger gleichzeitig gelesenen Bytes ab: Wird jeweils nur 1 Byte gelesen, sinkt die Rate auf 5 Mbyte/s. NXP hat die Quad- Mode-Operation mit 80 unterschiedlichen Flash-Chips von 512 Kbyte bis 16 Mbyte von den Herstellern Atmel, Gigadevice, Macronix, Micron, Microchip und Winbond getestet.

Jobangebote+ passend zum Thema

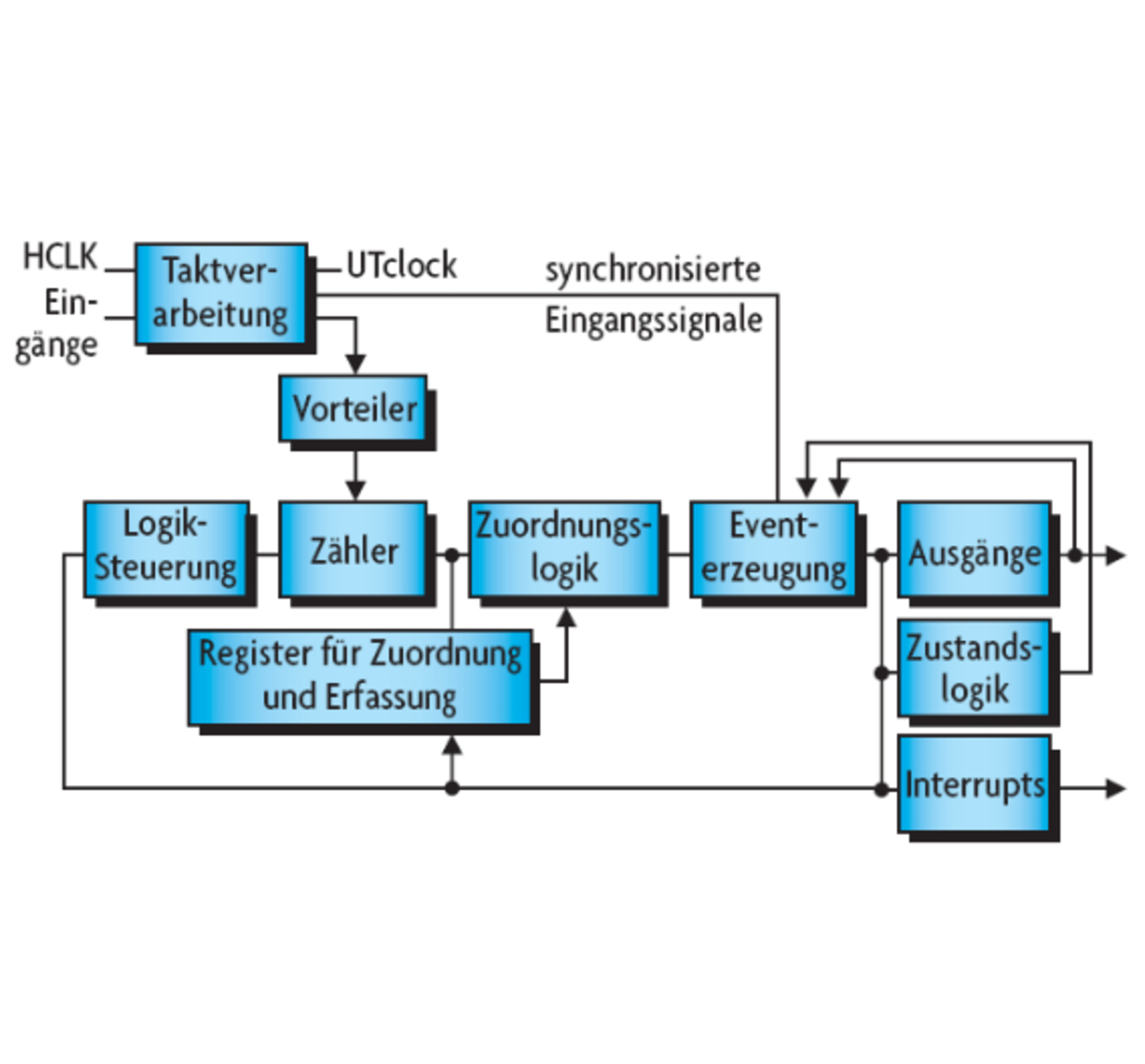

Das zweite interessante Peripherieelement ist das „State-Configurable-Timer- Subsystem“ (Bild 3). Dabei handelt es sich um einen programmierbaren Allzweck-Zustandsautomaten in Kombination mit einem Timer. Die acht Eingänge des Zustandsautomaten und 16 Timer-Ausgänge werden auf Pins herausgeführt, um mit externer Hardware kommunizieren zu können. Nachdem der Zustandsautomat einmal von der CPU initialisiert wurde und vorausgesetzt, dass die Anzahl der Zustände nicht mehr als 16 beträgt, arbeitet der Timer für die Zustandsänderungen völlig autonom und benötigt keine weitere Involvierung der CPU.

Ein weiterer Block decodiert aus Eingängen, Ausgängen und Zuständen bis zu 16 Ereignisse, um den Zustandsautomaten von einem Zustand in den nächsten zu überführen.

Die Funktionalität soll laut NXP dazu ausreichen, auch komplexe Funktionalität wie die Steuerung eines bürstenlosen Gleichstrommotors, eines Schrittmotors oder eines Wechselstrom- Induktionsmotors abzubilden. Möglich wäre auch der Betrieb einer seriellen Schnittstelle wie DALI oder LIN, die nicht als Peripherie auf dem Chip abgebildet sind. Um den Zustandsautomaten zu programmieren, kann das Tool Fizzim (www.fizzim. com) eingesetzt werden.

Die ersten verfügbaren Mitglieder der LPC1800-Familie (1810, 1820, 1830 und 1850) werden ohne Flash- Speicher ausgeliefert und können daher nur mit externem Flash- Speicher betrieben werden. Weitere MCUs werden dann 512 Kbyte, 768 Kbyte oder 1 Mbyte Flash-Speicher aufweisen.

- 150 MHz für den Cortex-M3

- Zwei bemerkenswerte Peripherie-Elemente