IC-Entwicklung

Besser die Leistungsaufnahme optimieren als das Timing

Legen IC-Entwickler beim Place-and-Route-Tool den Fokus auf die Optimierung der Leistungsaufnahme können sie bessere Gesamtergebnisse erzielen, als wenn sie ein optimales Timing anstreben. Die Power-First-Methodik stellt aber auch Anforderungen.

Wenn eine niedrige Leistungsaufnahme hohe Priorität bei den physischen Entwicklungszielen hat, benötigen IC-Entwickler ein Place-and-Route-Tool, das für einen bestimmten Knoten, eine bestimmte Bibliothek oder einen bestimmten IC-Entwurf den niedrigsten Leistungsbedarf sowie eine verbesserte Fläche und Leistung liefert. Die Power-First-Methodik des Aprisa Place-and-Route-Tools von Siemens zeigt, dass Entwickler mit dem Fokus auf die Leistungsaufnahme keine unnötigen Kompromisse eingehen müssen.

Unter den wichtigsten Zielen beim Place-and-Route-Verfahren – Leistungsfähigkeit, Leistungsaufnahme und Fläche (PPA) – war die Leistungsfähigkeit traditionell stets das Hauptziel. Eine geringe Leistungsaufnahme gewinnt jedoch insbesondere im Hinblick auf die heutigen, hochmodernen Prozessknoten zunehmend an Bedeutung. Natürlich möchte niemand weniger leistungsstarke ICs Deshalb nutzen Place-and-Route-Tools heute eine Vielzahl von Strategien, mit denen die Leistungsaufnahme bei unverminderter Leistungsfähigkeit so niedrig wie möglich gehalten wird.

Bei Place-and-Route-Software gibt es jedoch große Unterschiede. Ältere Programme auf dem Markt nutzen mehrere verschiedene Datenmodelle. Dies führt jedoch zu einer ineffizienten Kommunikation zwischen allen beteiligten Engines – Platzierung, Leitungsführung, Taktbaum-Synthese – und umständlichen Arbeitsschritten. IC-Entwickler stehen dann oft vor der Wahl entweder den Projektabschluss zu verzögern oder nicht optimale Ergebnisse zu akzeptieren. Ein Design-Tool, das auf einem einheitlichen Datenmodell basiert und moderne Algorithmen verwendet, ist schneller, benutzerfreundlicher und kann die optimale PPA für die heutigen Hierarchie- und Blockebenen-Entwürfe erstellen. Eine äußerst leistungsfähige Place-and-Route-Software ist jedoch nur die Grundlage zum Erreichen einer geringen Leistungsaufnahme während des Place-and-Route-Verfahrens. Das Tool muss zusätzlich Folgendes leisten:

- Geschickt mehrere Power-Domains verwalten.

- Erweiterte Power-First-Optimierungen während des Prozessablaufs durchführen.

Jobangebote+ passend zum Thema

Verwaltung mehrerer Power-Domains

Eine Unterstützung mehrerer Power-Domains gewährleistet, dass alle Elemente, die für eine Low-Power-IC-Entwicklung erforderlich sind, einbezogen und gemäß den Low-Power-Spezifikationen verwendet werden. Die im digitalen Implementierungsablauf verwendete Software muss in der Lage sein, auf mehreren Power-Domains fehlerfrei zu puffern und die Platzierung aller Stromversorgungszellen, wie Zellen zur Pegelverschiebung, Isolation und Leistungsschaltung sowie Halte-Flip-Flops auszuführen. IC-Entwürfe, in denen eine niedrige Leistungsaufnahme wichtig ist, erfordern auch die Verlegung sekundärer Strom-/Masse-Pins sowie Leiterführungen zur Stromverteilung innerhalb der Spannungsinseln.

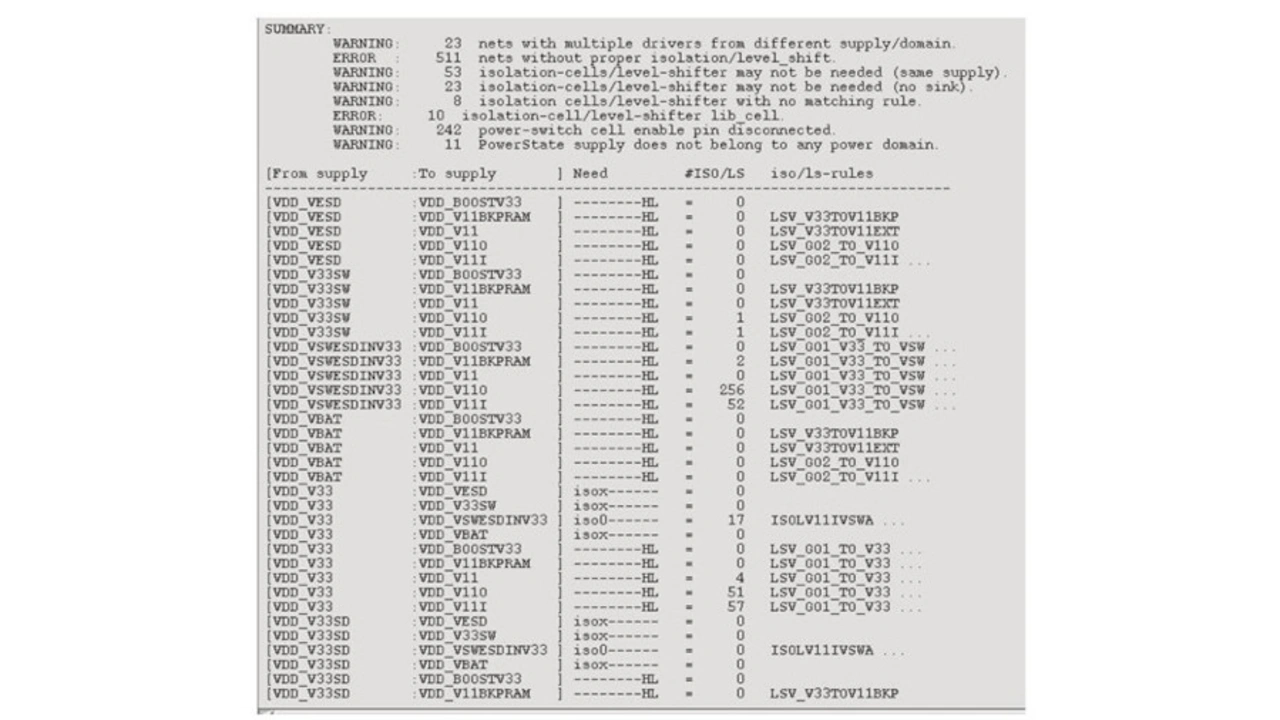

Entwickler sollten also nach Place-and-Route-Software suchen, die ihnen eine umfassende Unterstützung für mehrere Power-Domains bietet und das Unified Power Format (UPF) unterstützt. Es ist sehr nützlich, wenn die Software einen integrierten Power Domain Checker (Bild 1) umfasst, der Fehler in Bezug auf Power Domain, Zellenanordnung, Konnektivität und Pufferung kennzeichnet, so dass kein externes Tool erforderlich ist.

Power-First-Methodik – für eine niedrige Leistungsaufnahme ohne Kompromisse

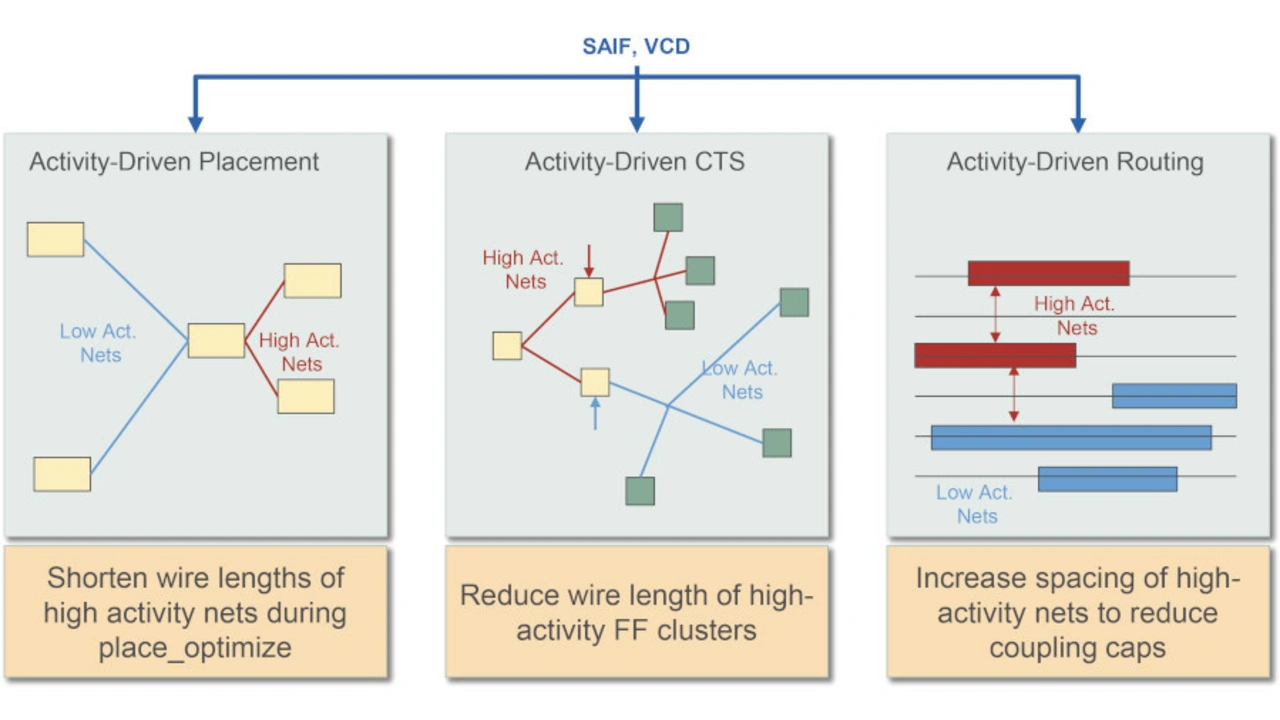

Zur Erfüllung strenger Leistungsaufnahmeforderungen ohne Zugeständnisse an die Leistungsfähigkeit muss das Place-and-Route-Tool einen niedrigen Leistungsbedarf zur höchsten Priorität machen. Durch den Einsatz von Techniken, wie der aktivitätsorientierten Platzierung und Leiterbahnführung zur Erzielung einer geringeren dynamischen Leistungsaufnahme, muss das Tool während des gesamten Prozesses auf dieses Ziel hinarbeiten.

Bild 2 zeigt, wie die Placement-Engine zur Reduzierung der Kapazität in Netzen mit hoher Aktivität Schaltinformationen verwendet. Dies geschieht während des gesamten Arbeitsablaufs einschließlich der Taktbaumsynthese, indem den Netzen mit hoher Aktivität kurze Verbindungen zugewiesen werden. Die Netze mit niedriger Aktivität werden dagegen gespreizt, um eine Überlastung zu vermeiden. Der Router verteilt die Netze hoher Aktivität, um die Kopplungskapazität und den Leistungsbedarf zu reduzieren. Er kann aber auch Schaltinformationen nutzen, um Entscheidungen darüber zu treffen, welche Regeln für Netze mit hoher und mit niedriger Aktivität gelten sollen.

Dank dieser Power-First-Methodik kann der Place-and-Route-Ablauf den bestmöglichen Leistungsbedarf für einen bestimmten Knoten oder eine Bibliothek erreichen, die Entwurfsspezifikationen erfüllen und dann von diesem Punkt aus auf die Optimierung des Timing-Ziels hinwirken. Diese Methode ist effektiver als der Versuch, den Leistungsbedarf nachträglich zu minimieren, nachdem die Zellen mit dem größten Leistungsbedarf bereits verwendet wurden, um das Timing-Ziel zu erreichen.

In der Power-First-Methodik werden unter anderem folgende Techniken eingesetzt:

- Taktübergangsfixierung für einen verbesserten Leistungsbedarf – Abschwächung des schnellen Übergangs der Puffer am Taktbaum, ohne Übergangsverletzungen zu verursachen.

- Kompromisse bei geringfügigen Zeitproblemen zugunsten einer hohen Leistungsreduzierung in der CTS (clock tree synthesis) – intelligenter Ausgleich von Unausgewogenheiten.

- Zusammenlegung und Entflechtung von Multi-Bit-Registern – Zusammenlegung von einzelnen Flip-Flops mit wenigen Bits zu Flip-Flop-Gruppen mit mehreren Bits.

- Vollständige LVF-Analyse (liberty variation format) und Optimierung – Verwaltung der Auswirkungen von On-Chip-Variationen.

Ergebnisse der Power-First-Methodik – ein Beispiel

Die Place-and-Route-Software Aprisa von Siemens nutzt die Power-First-Optimierung, um bei einer gleichzeitigen Minimierung der Timing-Kompromisse die interne Leistung sowie die Schalt- und Leckleistung bei höchst leistungsempfindlichen IC-Entwürfen zu reduzieren. In einem 7-nm-IC-Entwurf für einen Industrie-DDR-PHY mit ca. 1,3 Mio. Instanzen und einer Taktfrequenz von 1 GHz konnten die Power-First-Techniken die Gesamtleistungsaufnahme im Vergleich zum reinen Timing-Modus um 16 % reduziert werden – und das erreichte Timing korreliert mit dem Signoff.

Es ist möglich, im Place-and-Route-Verfahren eine geringere Leistungsaufnahme zu erzielen, indem Software verwendet wird, die dafür ausgelegt ist und die folgenden Funktionen bietet:

- Vollständige Unterstützung für alle branchenüblichen Leistungsformate sowie für mehrere Power-Domains, einschließlich eines integrierten Power Domain Checkers.

- Ein einheitliches Datenmodell, auf das während des gesamten Ablaufs zurückgegriffen wird und das in jeder Phase des Arbeitsablaufs Informationen zum Routing und zu parasitären Effekten zur Verfügung stellt, was zu einem konsistenten Timing und DRC (design rule checking) sowie zu einer ausgezeichneten Korrelation mit den Signoff-Tools führt.

Die Autorin

Janet Attar

ist als Product-Marketing-Managerin bei Siemens EDA verantwortlich für die Place-and-Route-Lösung Aprisa. Sie verfügt über mehr als 15 Jahre Erfahrung in der Halbleiterindustrie. Vor ihrer Tätigkeit bei Siemens war Attar als Anwendungsingenieurin bei Cadence Design Systems und als Physical Design Engineer bei International Rectifier (jetzt Infineon Technologies) tätig.