Hardware

Mehr Sicherheit im IoT

Fortsetzung des Artikels von Teil 1

Hardware-basierte Sicherheitsmerkmale

Es gibt zahlreiche Hardwarefunktionen, mit denen sich die Sicherheit eines Systems erhöhen lässt. Bereitgestellt werden können sie beispielsweise durch ein diskretes Secure-Element oder in einigen Fällen auch durch im Mikrocontroller integrierte Lösungen.

In diesem Kontext ist als erstes Secure Boot zu nennen. Es ist ein essenzielles Feature, um die Echtheit und Unverfälschtheit der vom Prozessor ausgeführten Firmware zu gewährleisten. Hierzu startet der Mikrocontroller zunächst einen Bootloader aus dem ROM. Dieser überprüft die Signatur des Codes bereits im Flash, bevor er ausgeführt wird. Durch eine Flash-Verschlüsselung wird der Code zusätzlich geschützt.

Eine physikalisch nicht-klonbare Funktion (Physical Unclonable Function, PUF) dient als eindeutiger Identifikator. Sie nutzt die zufälligen Variationen der jeweiligen Halbleiter, um eine ganz einzigartige Signatur zu erzeugen, die einen eindeutigen »Fingerabdruck« ergeben. Eine solche PUF und die zugehörige Logik können für die sichere Schlüsselerzeugung und -verwaltung verwendet werden. PUF ermöglicht eine sichere Geräteauthentifizierung und flexible Schlüsselbereitstellung mit den damit verbunden Vorteilen für ein sicheres Asset-Management. Sie dient als Root-of-Trust und sorgt für die in der Kommunikation so wichtige End-to-End-Sicherheit. Sie garantiert zudem, dass Daten, die auf einem Gerät verschlüsselt wurden, auch nur von diesem einen Gerät entschlüsselt werden können. Dadurch bleiben die Daten geschützt, selbst wenn sie auf ein anderes funktionsidentisches System kopiert werden.

Arm-Prozessorkerne integrieren zudem ein Hardware-Sicherheitssystem namens TrustZone. Es kann für den Laufzeitschutz von Assets – zum Beispiel private Daten und Passwörter – verwendet werden, indem diese ausschließlich in einer sicheren Umgebung verwendet werden. TrustZone realisiert dabei zwei Hardwarewelten: eine sichere und eine unsichere. Die nicht-sichere Welt bietet eine flexible Ausführungsumgebung ohne Zugriff auf sicherheitskritische Register oder Daten. Nicht-sicherer Code kann auf gesicherte Ressourcen nur über spezifische Schnittstellen zugreifen, die von der sicheren Welt bereitgestellt werden.

Betriebssystem und Anwendungen laufen typischerweise in der nicht-sicheren Welt, während eine deutlich kleinere Untermenge vertrauenswürdigen Codes in der sicheren Welt ausgeführt wird. Dieses Verfahren reduziert auch die Menge an Code, der besonders sorgfältig programmiert und auditiert werden muss. Für eine hohe Entropie und um zu gewährleisten, dass Handshake-Verfahren nicht anfällig für Replay-Angriffe sind, wird zudem ein echter Zufallszahlengenerator (True Random Number Generator, TRNG) benötigt.

Weitere mögliche Features sind die Manipulationserkennung zum Schutz vor physischem Zugriff auf den Chip, eine Speicherschutzeinheit (MPU) zur Taskisolierung, Hardwarebeschleuniger für verschiedene Krypto-Funktionen sowie eine Abschirmschicht über sicherheitskritische Chip-Areale. Welche dieser Funktionen letztlich in das Target-System implementiert werden sollen, muss anhand des erforderlichen Sicherheitsniveaus und den damit verbunden Mehrkosten für die Hardware entschieden werden.

Jobangebote+ passend zum Thema

Beispiel für eine Sicherheitskonfiguration

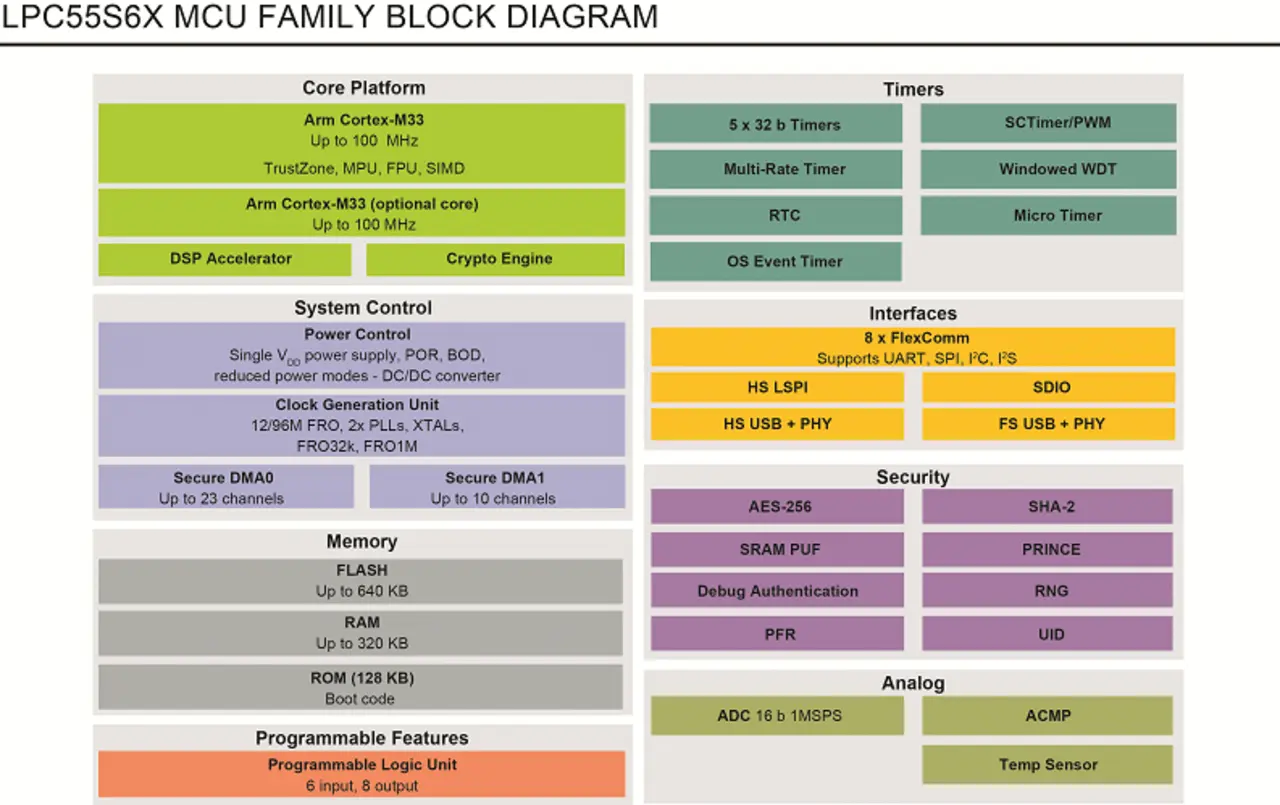

Der kürzlich veröffentlichte LPC55S6x von NXP integriert viele der oben beschriebenen hardwarebasierten Sicherheitsmerkmale und ist damit einzigartig auf dem MCU-Markt. Er verfügt über zwei Arm-Cortex-M33-Kerne, von denen einer TrustZone-M unterstützt, sowie mehrere Co-Prozessoren.

Während der Chipsatz Secure Boot mit Anti-Rollback-Schutz unterstützt, ermöglicht die Hardware auch die Echtzeitausführung von verschlüsselten Images aus dem Flash-Speicher. Der Flash-Inhalt wird nur im Ausführungspfad des Cores entschlüsselt. Die Folge: Böswillige Versuche, den Flash-Speicher direkt auszulesen, ergeben nur verschlüsselte Daten. Das geistige Eigentum der Software und die damit verbundenen Daten bleiben geschützt.

Zudem verwendet der LPC55S6x-Mikrocontroller eine PUF-Technik, die auf einem dedizierten SRAM-Block basiert. Aufgrund von Transistorvarianzen nimmt jede Speicherzelle beim Einschalten entweder den Status 1 oder 0 an. Dieses Verhalten ist bei jedem Einschalten des SRAMs konsistent, sodass diese Anlaufwerte sowohl ein zufälliges als auch reproduzierbares Muster erzeugen, das für jeden Chip einzigartig ist. Dieser Silizium-Fingerabdruck wird als geheimer Schlüssel genutzt, mit dem sich ein Device eindeutig identifizieren lässt und als Root-of-Trust für die weiteren Sicherheitsfunktionen dient.

Der LPC55S6x bietet zudem mehrere Hardwarebeschleuniger für die Verschlüsselung und Entschlüsselung von Daten in Echtzeit sowie die Beschleunigung verschiedener symmetrischer und asymmetrischer kryptographischer Algorithmen. Er verfügt auch über Manipulationserkennung, sichere GPIO und DMA sowie ein Debug-System, das eine Authentifizierung erfordert, um aktiviert zu werden. Der LPC55S6x ist der erste Mikrocontroller, der diese Funktionen zu einem kompletten Sicherheitspaket kombiniert und damit ein hohes Maß an Sicherheit für viele IoT- und Embedded-Anwendungen bei geringen Kosten bietet.

Der zweite Arm-Core und der DSP-Coprozessor lassen sich zudem verwenden, um komplexe Anwendungssoftware auszuführen. So können beispielsweise Machine-Learning- und Inferenz-Systeme auf Basis der Arm CMSIS-NN-Library implementiert werden. Sie bietet eine Sammlung speichereffizienter neuronaler Netzwerk-Kernels, die auf den Cortex-M Core optimiert wurden, und kann mit branchenüblichen Frameworks wie Caffe genutzt werden, um auf Basis von Bildklassifizierung, Spracherkennung und natürlicher Sprachverarbeitung neue Nutzungserfahrungen für Anwender zu generieren.

Sicherheit ohne Leistungseinbußen

Dem steigenden Sicherheitsbedürfnis in IoT-Systemen kann durch den Einsatz von Hardware Rechnung getragen werden, die integrierte Sicherheitsfeatures moderner Mikrocontroller nutzt. Solche MCUs vereinfachen die Embedded-Sicherheit und ermöglichen eine hardwarebasierte Root-of-Trust für sichere Authentifizierung, Kommunikation und Datenspeicherung. Sicherheit muss jedoch den Kostenvorgaben von Embedded-Systemen entsprechen.

Der Mikrocontroller LPC55S6x zeigt, dass ein Mehr an Sicherheitsfunktionen in einer MCU ohne Mehrkosten oder Leistungseinbußen umgesetzt werden kann. Ermöglicht wurde dies durch den Einsatz eines Halbleiterfertigungsprozesses höherer Dichte als bisher, sodass ein höherer Integrationsgrad erreicht wurde.

Bezogen werden kann der neue Mikrocontroller LPC55S6x unter anderem bei EBV. Der technische Vertriebspartner von NXP bietet OEM- und ODM-Kunden technische Unterstützung in allen Phasen des Designprozesses.

Die Autoren

Christian Krieber (li.) ist Director Segment Security & Identification bei EBV Elektronik.

Thibault Richard ist Connectivity & Security Specialized FAE bei EBV Elektronik.

- Mehr Sicherheit im IoT

- Hardware-basierte Sicherheitsmerkmale