CompactPCI mit 11. Core/Xeon-Generation

Langzeitsupport des parallelen PCI-Busses

PCI-Bus basierte Boards des 1999 gelaunchten CompactPCI-Standards sind vor allem in Systemen mit hohen Langzeitverfügbarkeitsanforderungen zu finden. Hier besteht weiherhin Nachfrage nach neuer Performance. EKF Elektronik stattet sie nun sogar mit neuen Intel Core- und Xeon-Chips aus.

Zur embedded world 2023 kündigt EKF Elektronik zwei neue Prozessorkarten im Format »CompactPCI« mit 3HE Einbauhöhe an. Bestückt sind sie mit Intels Core- und Xeon-Prozessoren der 11. Generation – Codename Tiger Lake H45. Sie sollen sowohl »CompactPCI Serial«, »CompactPCI Classic« sowie »CompactPCI PlusIO« unterstützen. Letztere beiden Spezifikationen unterstützen noch den klassischen parallelen PCI-Bus, für den es noch heute zahlreiche Erweiterungskarten in Form von Commercial off-the-shelf (COTS)-Produkten sowie proprietäre Entwicklungen gibt.

Entwickler von CompactPCI-Systemen können somit jedwede Version umsetzen und ihre Investitionen in den 1999 gelaunchten Standard der PCI Computer Manufacturers Group (PICMG) langfristig sichern. Die neuen Baugruppen sind bis mindestens 2032 verfügbar – genauso wie die Vorgänger-CompactPCI-CPU-Baugruppen mit Intels Xeon-E3-v6-Prozessoren der 7. Generation (Codename Kaby Lake). Diese bietet EKF ebenfalls für alle drei Sub-Spezifikationen von CompactPCI an.

Vorteile der Upgrades sind unter anderem eine höhere Energieeffizienz, höhere prozessorintegrierte Sicherheit und Rechenleistung, aktueller Softwaresupport sowie der Support von künstlicher Intelligenz (KI) und aktuellen Grafikfeatures. Die 11. Generation der Core-Prozessoren unterstützt PCI zwar nicht mehr nativ. EKF Elektronik verbaut auf seinen CompactPCI-Classic- und CompactPCI-PlusIO-konformen CPU-Boards jedoch eine softwaretransparente PCIe-zu-PCI-Bridge sodass Entwickler bestehende Applikationen nahtlos auf die neuen Module portieren können.

Neuer J2-Konnektor für PlusIO

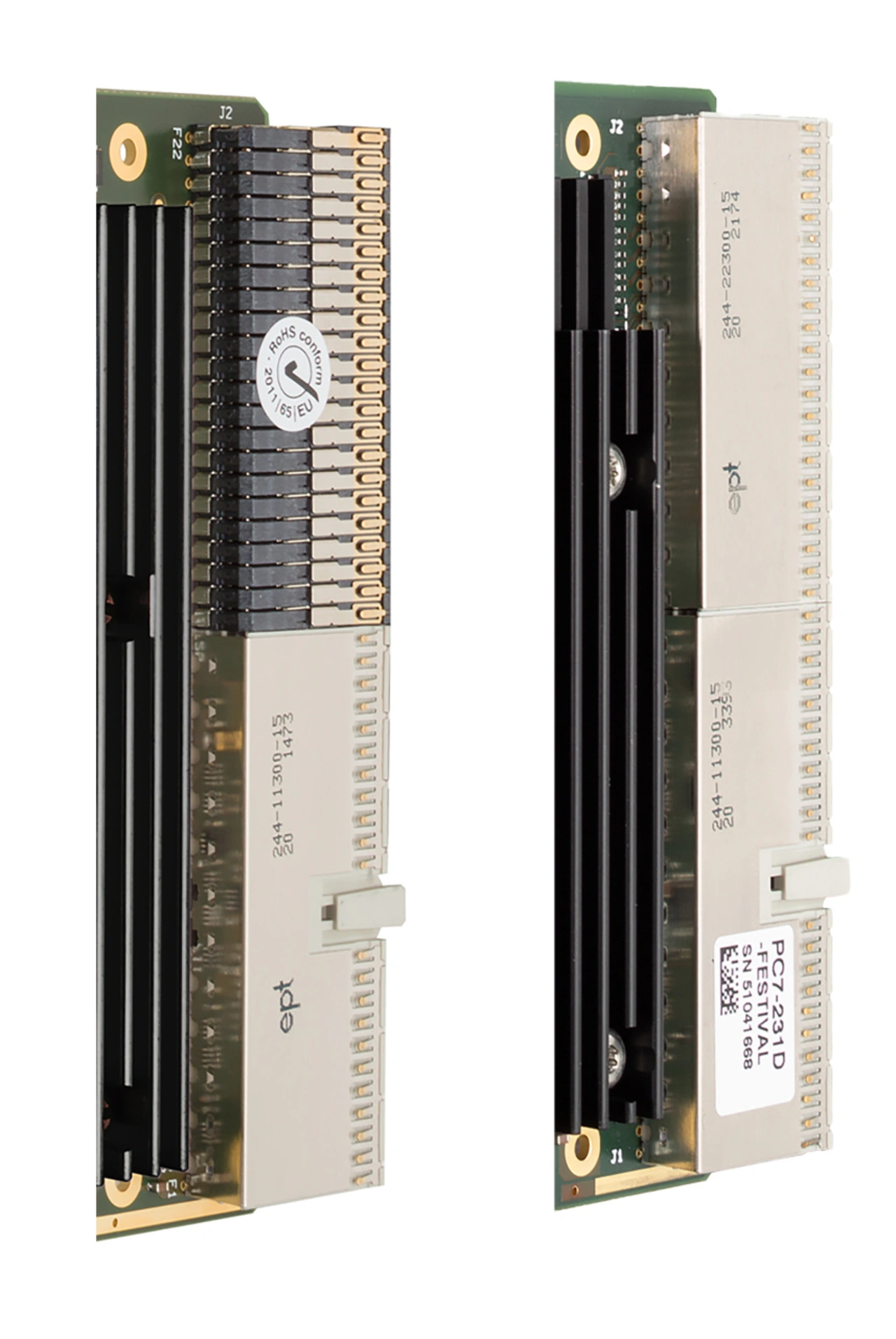

Anwender der CompactPCI-PlusIO-Spezifikation finden auf den Baugruppen einen neuen J2-Konnektor vor. Es ist der Footprint-kompatible J2-Konnektor der CompactPCI Classic (PICMG 2.0)-Spezifikation. Erforderlich wurde der Wechsel, weil der speziell für PlusIO entwickelte J2-Konnektor abgekündigt wurde. Für das Umstellen ist jedoch kein Re-Design der Backplane erforderlich. Einzige Einschränkung: Der Hochgeschwindigkeits-Backplane-Transfer ist für PCIe Gen1 auf 2,5 Gigatransfers pro Sekunde (GT/s) und für SATA auf 1,5 Gbit/s limitiert. Möchte man die volle Bandbreite nutzen, ist das applikations- und systemspezifisch möglich. Der CompactPCI-seitige PCI-Bus ist in gewohnter Bandbreite bis 133 MB/s verwendbar.

Wer nutzt heute noch den PCI-Bus?

Der Langzeit-Support von PCI ist für viele »Generation Z«-Applikationen entscheidend. Also Systeme, die ab dem Jahr 2000 eingeführt wurden, als der PCI-Bus seinen Siegeszug feierte und den alten ISA-Bus ablöste. Zu der Zeit wurden sehr viele Erweiterungskarten entwickelt, da die Prozessortechnik beziehungsweise der Chipsatz deutlich weniger Input/Output (I/O)-nativ unterstützten und die Komponenten einen hohen Platzbedarf hatten. Aus dem Grund konnten sie vergleichsweise weniger I/O-Funktionen anbieten. Gute Motherboards zeichneten sich folglich über ihre vielen PCI-Erweiterungssteckplätze aus. Gleichzeit zog die x86-Technik erfolgreich in den Markt der industriellen Steuerungen ein, weshalb zahlreiche industrielle I/O-Baugruppen auf Basis von PCI für Motherboards und auf Basis von CompactPCI für Backplane-Systeme verfügbar wurden.

Der PCI-basierte Baugruppenbestand ist bei CompactPCI sehr breit und viele verwandte Schnittstellen wie digitale und analoge I/Os, RS-232, RS-485 sowie Feldbusse wie CAN oder Relaiskarten erfordern keine höhere Bandbreite, als der PCI-Bus bereitstellt. Entsprechend findet man in vielen Applikationen, die auf eine lange Verfügbarkeit setzen, noch heute PCI-basierte Systemdesigns. Typische Anwendungsbereiche sind beispielsweise

- die Bahntechnik (von Fahrgastinformationssystem bis zu Stellwerkssteuerung),

- Leitstand- und Wartentechnik in Kraftwerken mit Supervisory Control and Data Acquisition (SCADA)-Anbindung und Visualisierungsfunktionen,

- Bildinspektionssysteme sowie

- Messtechnik-Applikationen.

Jobangebote+ passend zum Thema

Verbinder der Welten

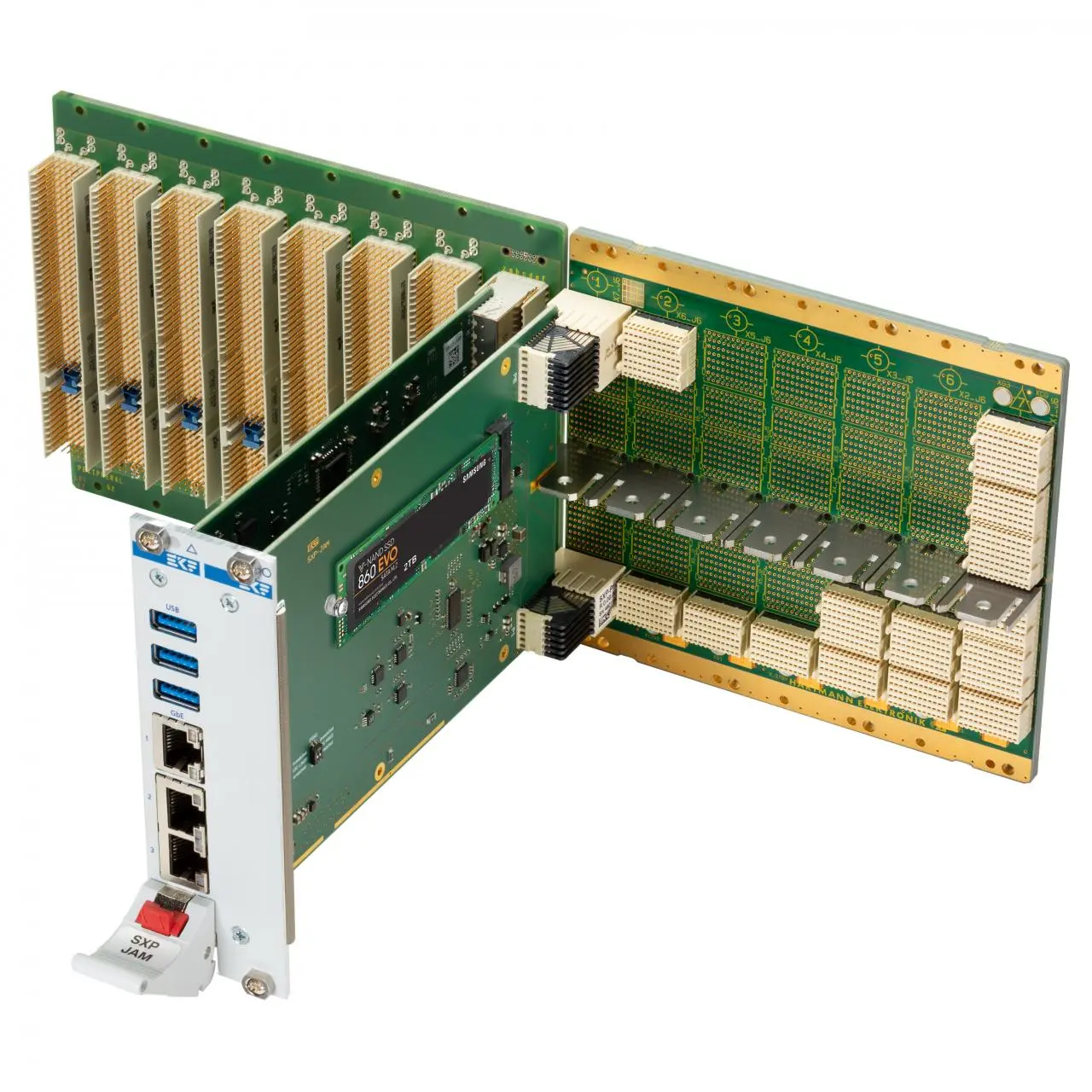

OEM wollen diese Applikationen auf Basis der bestehenden Investitionen in ihren individuellen I/O-Karten und Systemdesigns weiterhin zuverlässig und langzeitverfügbar betreiben. Zumal CompactPCI mit seinen drei Primärstandards CompactPCI Classic, PlusIO und Serial jedweden Migrationspfad unterstützt. Zudem ermöglicht das jeden Mix aus Legacy- und State-of-the-Art-Backplane-Kommunikation: Neben den PlusIO-CPU-Boards, die per se für hybride Systeme entwickelt wurden, kann eine CompactPCI Serial CPU das ebenfalls tun. Die von EKF Elektronik entwickelte Kopplerbaugruppe »SPX-JAM« wird im letzten I/O-Slot einer Serial-Backplane platziert und darüber eine CompactPCI-Busplatine angebunden. Hiermit stehen bis zu sieben PCI-Bus-basierte CompactPCI-I/O-Baugruppen zusätzlich bereit. Es gibt also zahlreiche Optionen, PCI-Legacy weiter zu betreiben. Von puren 32 oder 64 Bit PCI-Bus-kompatiblen Auslegungen mit CompactPCI-Classic-CPU-Baugruppen über hybride PCI- und PCIe-Systeme mit CompactPCI-PlusIO-CPU-Boards bis hin zu CompactPCI-Serial-CPU-Boards – bald mit PCIe Gen4 und Gen5 Support – ist mit CompactPCI alles möglich. Kein anderer Embedded-Standard bietet eine so hohe Bandbreite an Möglichkeiten zum Beibehalten des PCI-Supports.

Günstige Alternative zu PXI

Auch für die in der Messtechnik weit verbreiteten PCI extensions for Instrumentation (PXI)-Systeme sind CompactPCI-Baugruppen attraktiv. PXI baut auf CompactPCI auf und ist somit mechanisch voll kompatibel. Einzig nutzt PXI über den J2-Konnektor einige bei CompactPCI nicht belegte Pins, um von der CPU-Karte aus Trigger- und Clocksignale für I/O-Baugruppen zu senden. Jede Systemvariante, die diese nicht zwingend erfordert – und das sind alle Applikationen, die keine Trigger brauchen oder bei denen sich die I/O-Karten selbst triggern – kann also eine CompactPCI-CPU-Baugruppe in sein PXI-System integrieren. Somit profitieren die Applikationen von einem deutlich günstigeren Preis gegenüber PXI-CPU-Baugruppen der Messtechnik-Platzhirsche. Einziger Unterschied: CompactPCI-CPU-Baugruppen sind auf der rechten Seite bestückt und die Backplane ist links ausgerichtet. Steckt man sie in ein PXI-System, das die CPU links vorsieht, kann es vorkommen, dass die Konnektoren der ersten Peripheriesteckplätze überdeckt werden, setzt man vorgefertigte PXI-Backplanes ein. Als Ausweg können Nutzer PXI-Peripherie-Baugruppen jedoch in Standard CompactPCI Backplanes zusammen mit der CompactPCI-CPU-Baugruppe verwenden.

Die neuen CompactPCI-Prozessorboards mit Intel-Core-Prozessoren der 11. Generation in CompactPCI Serial (»SC9-TOCCATA«) sind voraussichtlich ab Mitte 2023 verfügbar. Die »PC9-TOCCATA«-Varianten für CompactPCI Classic und CompactPCI PlusIO gehen etwas später in Serie. Bis zur Serienverfügbarkeit steht zudem die siebte Generation in Form der »PC7-FESTIVAL« ab sofort zur Verfügung, um bereits heute bestehende Verfügbarkeitsprobleme in cPCI- und PlusIO-Anwendungen sicher und langfristig zu lösen. Alle sind ab sofort unter sales@ekf.de vorbestellbar.