Leiterplattenfertigung

Dünner als jedes Menschenhaar

Fortsetzung des Artikels von Teil 1

Panel-Plating mit Strukturbreiten von 25 µm

Beim Panel-Plating oder -Tenting indes wird die Leiterplatte mit dem gesamten benötigten Kupfer beschichtet; anschließend wird mittels Fotolithografie das Schaltbild erzeugt. Der Prozess ist einfacher als das Pattern Plating, weil er weniger Prozessschritte benötigt. Zudem ist er sehr zuverlässig und kommt ohne Metallresist aus.

Aber auch diese Technik stößt an ihre Grenzen bezüglich kleinster Leiter- und Abstandsbreiten. So sind eine Auflösung von 25 µm und entsprechende Abstände nur bei einer sehr niedrigen Kupferdicke von etwa 8 µm beziehungsweise mit einem Fotoresist von 10 µm Dicke zu erreichen.

Wegen der maximalen Gesamtkupferdicke von 8 µm können keine Verbindungen zwischen Schichten mit Stacked-Via-Technologie und keine Vias-in-Pad-Strukturen eingesetzt werden. Selbst bei Verwendung von Basismaterialien mit ultradünnen Kupferkaschierungen reicht die aufgebrachte galvanische Kupferschicht nicht aus, um Blindlöcher ausreichend bzw. spezifikationskonform mit Kupfer zu füllen.

In den vergangenen Jahren realisierte man zunehmend Schaltkreise mit Hilfe einer Dünnfilmtechnologie auf organischen Substraten wie Folien; und zwar als klassischer Semi-Additiv-Prozess, bei dem Vakuumbeschichtung, Fotolithografie, Elektrogalvanisierung und chemische sowie Trockenätzverfahren zum Einsatz kommen.

Jobangebote+ passend zum Thema

Mit dieser Technik erreicht man zwar Leiterbreiten und -abstände von weniger als 15 µm, muss dies aber mit einem zu hohen Preis erkaufen, der vor allem durch die Begrenzung auf maximal 36 Quadratzoll bedingt ist. Mit neuen Prozessen könnte man diese Technologie zwar hochskalieren, aber zu welchem Preis?

Vonnöten wäre ein neue Anlagentechnik; zudem müssten Prozessschritte und das Handling flexibler Folien ohne Kupferkaschierung verbessert werden. Außerdem sind die heute verwendeten Polyimid-Materialien nicht ohne Kupferkaschierung erhältlich. Diese müsste jedoch vor Beginn der Verarbeitung entfernt werden und es fehlen auch geeignete Fotolacke. Selbst wenn so größere Schaltkreise möglich wären, die hohen Prozesskosten machen die Herstellung unrentabel.

Durch eine intelligente Kombination der klassischen Techniken lassen sich deren Nachteile vermeiden. Die Firma Cicor nennt diese Kombination DenciTec. Auf deren Basis lassen sich PCB-Designs mit extrem hoher Dichte fertigen, ohne die Nachteile der genannten Methoden in Kauf nehmen zu müssen. Außerdem stehen für DenciTec neue Basismaterialien zur Verfügung.

DenciTec steht für eine Kombination klassicher Techniken

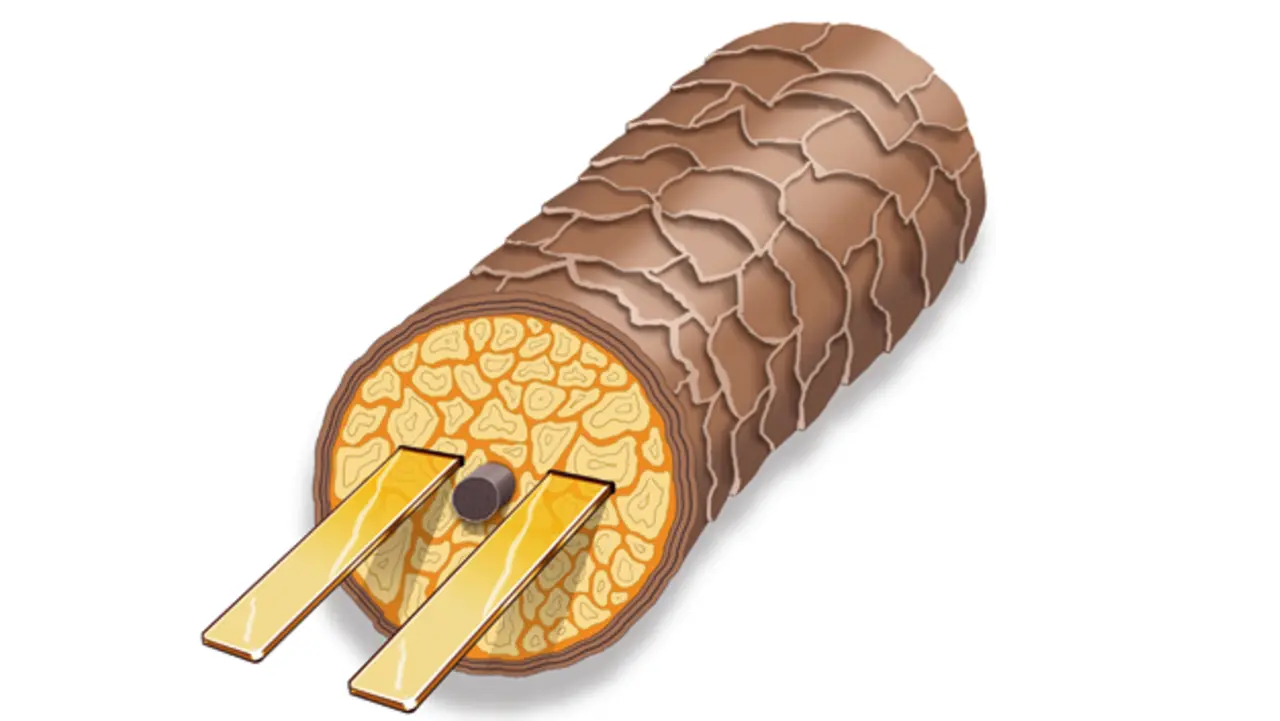

Mit der neuen Technologie lassen sich die funktionalen Strukturen einer Leiterplatte weiter miniaturisieren; bei den Leiter- und Abstandsbreiten zum Beispiel auf Werte bis zu 25 µm und bei den Kupferdicken auf Werte von 20 ± 5 µm auf allen Lagen. Des Weiteren lassen sich Laser-Via-Durchmesser von 35 µm sowie Restringe von 30 µm auf den Innenlagen und 20 µm auf den Außenlagen realisieren. Ebenfalls machbar sind kupfergefüllte Blind-Vias mit der Möglichkeit zum Via-Stacking und Vias in Pads sowie ultradünne Schaltkreise durch Einsatz eines 12,5-µm-Polyimid-Kernmaterials (4-Schicht-Flex-Schaltkreise mit weniger als 120 µm Dicke).

Aufgrund dieser immens kleinen Strukturen lassen sich auf den Leiterplatten sogar neue Funktionen integrieren, ohne die Leiterplatte vergrößern zu müssen. In jedem Fall aber können bei vielen Leiterplattendesigns unter günstigsten Voraussetzungen bis zu 70 % der Fläche über alle Lagen eingespart werden.

- Dünner als jedes Menschenhaar

- Panel-Plating mit Strukturbreiten von 25 µm