3D-Integration mit Hilfe keramikbasierender Fertigungsprozesse:

Passives Embedding

Fortsetzung des Artikels von Teil 1

Snubber-Kondensatoren für IGBT-Module

Alle diese Vorteile prädestinieren CeraLink für das Embedding als Snubber-Kondensatoren in IGBT-Module. Dafür sind zwei SMD-Typen mit Nennspannungen von 500 V DC verfügbar (Bild 2). Die Low-Profile-1-µF-Variante mit Abmessungen von 4,35 × 7,85 × 10,84 mm3 und der 5-µF-Typ mit Abmessungen von 13,25 × 14,26 × 9,35 mm3 sind besonders kompakt und lassen sich sehr nahe und niederinduktiv am Halbleiter platzieren.

Temperaturschutz einbetten

Um eine möglichst hohe Effizienz von IGBT-Modulen in Invertern zu erzielen, werden sie an ihrem oberen Temperaturlimit betrieben. Will man dabei eine Schädigung der Halbleiter ausschließen, so macht dies die exakte Überwachung der Betriebstemperatur erforderlich. Allerdings sind bislang eingebettete, konventionelle Chip-NTC-Thermistoren nur bedingt geeignet, da sie nicht alle Halbleiter-Fertigungsprozesse überstehen. Dazu gehören insbesondere das Hochtemperatur-Löten und das Silber-Sintern unter Druck.

Jobangebote+ passend zum Thema

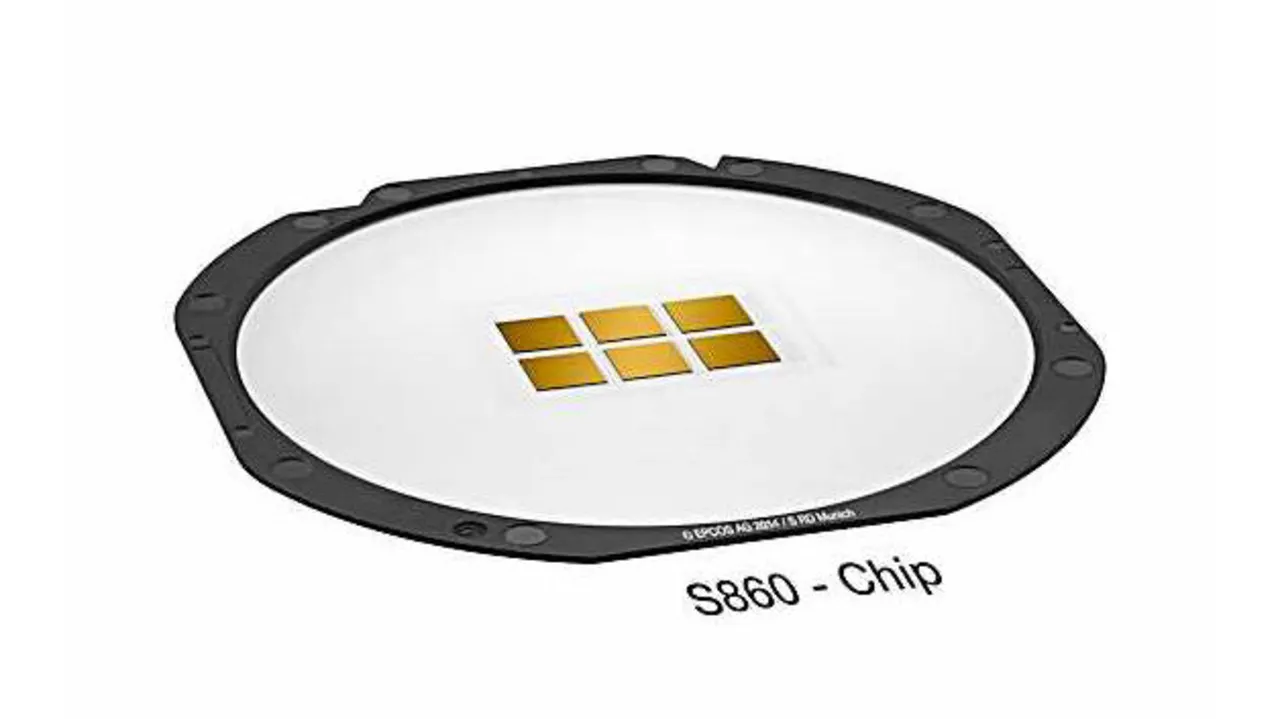

Um dieses Problem zu lösen, wurde ein Wafer-basierter Herstellungsprozess für Epcos-Chip-NTC-Thermistoren entwickelt (Bild 3). Diese neuen Bauelemente können dem thermischen und mechanischen Stress der Halbleiterprozesse standhalten. Darüber hinaus sparen sie Platz, weil keine speziellen Pads für das Löten auf dem Halbleitersubstrat nötig sind.

Bei NTC-Thermistoren, die aus Wafern gefertigt werden, ist die Anordnung der elektrischen Kontaktierungen entscheidend: Sie ist in diesem Fall horizontal und nicht vertikal. Dadurch wird mit dem unteren Anschluss eine direkte und sehr plane Kontaktierung auf dem Halbleitersubstrat unter Verwendung herkömmlicher Halbleiterprozesse ermöglicht. Der obere Anschluss wird über konventionelles Bonden kontaktiert – so wie es bei IGBT-Modulen üblich ist. Wahlweise sind die Kontaktflächen auch in vergoldeter oder versilberter Ausführung erhältlich, um bestmögliche Ergebnisse beim Bonden zu erzielen.

- Passives Embedding

- Snubber-Kondensatoren für IGBT-Module

- Sehr enge Toleranzgrenzen

- Semiconductor Embedded in Substrate

- Kompaktes TDK-Bluetooth-Low-Energy-Modul