Power Sequencing

Prozessoren, FPGAs, DSPs und SoCs richtig starten

Prozessoren, FPGAs, DSPs, A/D-Wandler und SoCs müssen mit mehreren Spannungen versorgt werden. Damit diese Bausteine richtig initialisieren, müssen diese in einer exakt festgelegten Reihenfolge ein- und ausgeschaltet werden. Was gilt es beim Power Sequencing zu beachten?

FPGAs und ähnlich komplexe ICs besitzen intern mehrere Stromversorgungsbereiche (Power Domains). Bei den meisten dieser Bausteine müssen diese Bereiche in einer eine bestimmte Reihenfolge gestartet oder heruntergefahren werden. Bei FPGAs etwa werden die Kernlogik, die I/O-Blöcke und die Hilfsschaltungen im Allgemeinen getrennt versorgt.

Der Kern umfasst typischerweise den Prozessor und die logische Basis des Bausteins. Dieser Bereich zeichnet sich durch eine niedrige Spannung und hohe Ströme aus. Wegen der extrem niedrigen Spannung sind die Anforderungen an die Genauigkeit entsprechend hoch, und aufgrund der dynamischen Natur der digitalen Last muss das Verhalten der Stromversorgung bei Lasttransienten hervorragend sein. Die I/O-Blöcke repräsentieren die verschiedenen Ein- und Ausgänge des FPGAs. Die erforderliche I/O-Spannung hängt vom Typ der Schnittstelle ab, wobei die Pegel generell höher sind als die des Kerns. Der erforderliche Strom hängt vom Typ, der Anzahl und der Geschwindigkeit der Schnittstelle ab.

Zu den Hilfsschaltungen gehören die rauschempfindlichen analogen Schaltkreise des FPGAs, z. B. PLLs und andere Schaltungsteile. Der Strombedarf ist relativ niedrig, aber die Welligkeit der Spannung stellt ein größeres Problem dar und ist zu minimieren. Welligkeit in den analogen Bereichen kann zu erheblichem Jitter und Phasenrauschen bei PLLs und zu störenden Reaktionen von Verstärkern führen.

Startet die Stromversorgung für die verschiedenen Bereiche in falscher Reihenfolge, kann das zu Problemen führen und das FPGA beschädigen. Ein Beispiel: Der I/O-Bereich beruht auf einem Tri-State-fähigen Bus, um Daten senden und empfangen zu können. Gesteuert wird dieser Bereich allerdings von der Kernlogik. Wird der I/O-Bereich vor dem Kern mit Strom versorgt, befinden sich die I/O-Pins in einem undefinierten Zustand. Wenn die externen Bus-Komponenten versorgt werden, kann es zu Konkurrenzsituationen auf dem Bus kommen. Dies kann zu hohen Strömen in den I/O-Treibern führen. Der Kern sollte also vor dem I/O-Bereich gestartet werden. Es ist wichtig, die Spezifikationen des FPGA-Herstellers zu beachten, um die empfohlene Reihenfolge des Ein- und Ausschaltens der Stromversorgung sowie die maximalen Differenzen zwischen den Versorgungsspannungen einhalten zu können.

Ein anderes Beispiel sind Leistungsoperationsverstärker. Auch sie haben zwei Stromversorgungsbereiche: einen analogen und einen digitalen. Im digitalen Bereich werden die Diagnosestatus-Flags für Übertemperatur und Überstrom sowie deren Aktivierungs- und Abschaltfunktion versorgt. Laut Spezifikation ist der digitale Teil vor dem analogen mit Strom zu versorgen, damit die Status-Flags gültig sind, bevor der analoge Bereich hochgefahren wird. Damit lässt sich eine mögliche Beschädigung des Bausteins vermeiden.

Jobangebote+ passend zum Thema

Methodologie des Power Sequencing

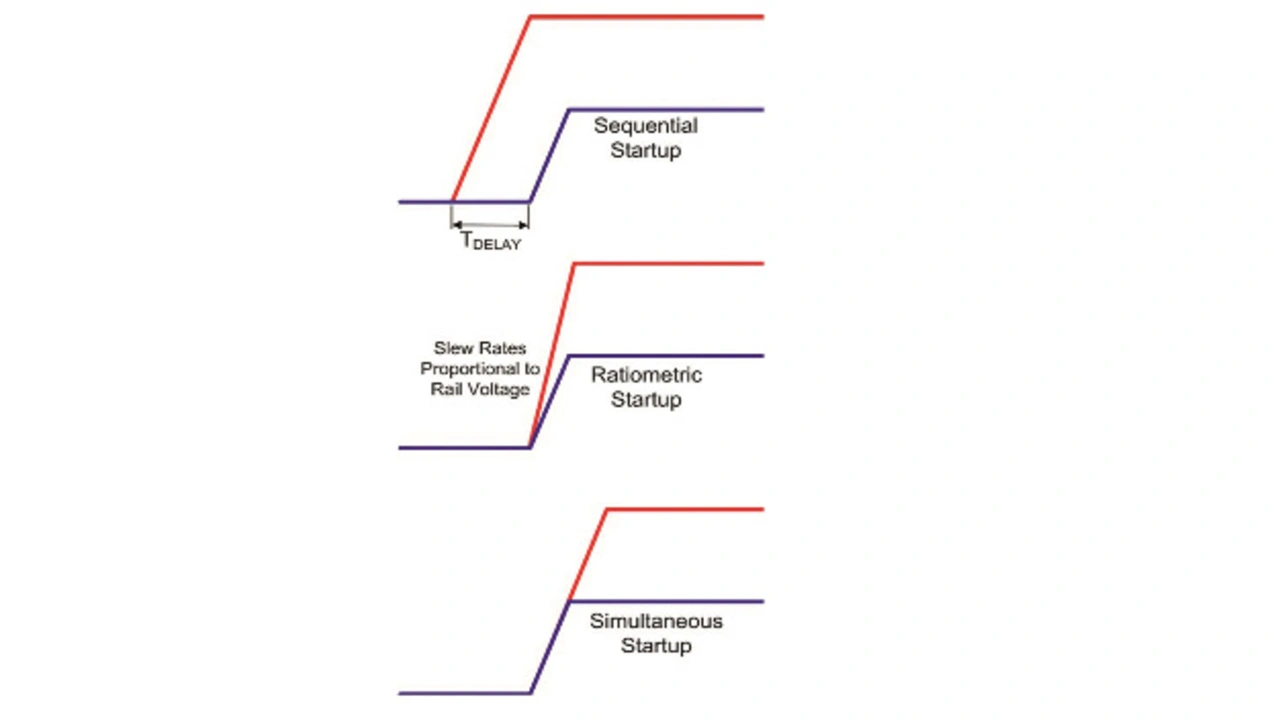

Drei Arten des Power Sequencing sind am häufigsten. Am weitesten verbreitet ist die sequenzielle, bei der die verschiedenen Versorgungsspannungen nacheinander starten (Bild 1, oben). Die Verzögerung zwischen den einzelnen Spannungen wird so festgelegt, dass die erste eingeregelt ist, bevor die nächste startet.

Die zweite Sequenzierungstechnik heißt ratiometrisch. Dabei starten die Spannungen gleichzeitig und erreichen gleichzeitig den jeweiligen Nennwert. Dazu muss die Anstiegszeit zur jeweiligen Nennspannung proportional sein (Bild 1, Mitte). Manche Bausteine vertragen vor dem Erreichen des eingeregelten Zustands möglicherweise keine zeitweiligen Spannungsdifferenzen. In einem solchen Fall könnte der Baustein während dieses Zeitraums auf einer der Versorgungsspannungen mehr Strom ziehen.

Der dritte Ansatz, ein gleichzeitiger Start, minimiert die vorübergehenden Spannungsdifferenzen. Diese Technik verringert den Umfang und die Dauer dieser Beanspruchung. Eine übliche Implementierung dieser Methode besteht darin, dass alle Versorgungsspannungen gleichzeitig hochfahren, wobei der Anstieg jeweils gleich groß ist (Bild 1, unten). Die Versorgungsspannung mit dem höheren Nennwert, normalerweise die I/O-Spannung, setzt den Anstieg weiter fort, nachdem die Versorgungsspannungen mit den niedrigeren Nennwerten, z. B. für den Kern, ihren endgültigen Wert bereits erreicht haben.

Unabhängig von der eingesetzten Technik müssen die Spannungen monoton ansteigen. Ist dies nicht der Fall, so wird der Baustein wegen eines unerwarteten Spannungsabfalls möglicherweise nicht richtig initialisiert. Zusätzlich kann ein Sanftanlauf (Soft Start) erfolgen, um die Einschaltströme zu begrenzen. Das Herunterfahren der Versorgungsspannungen sollte im Allgemeinen in umgekehrter Reihenfolge erfolgen. Die Wahl der Technik beim Starten und Herunterfahren hängt von der Spezifikation der Bausteine ab.

Beispiele für das Power Sequencing

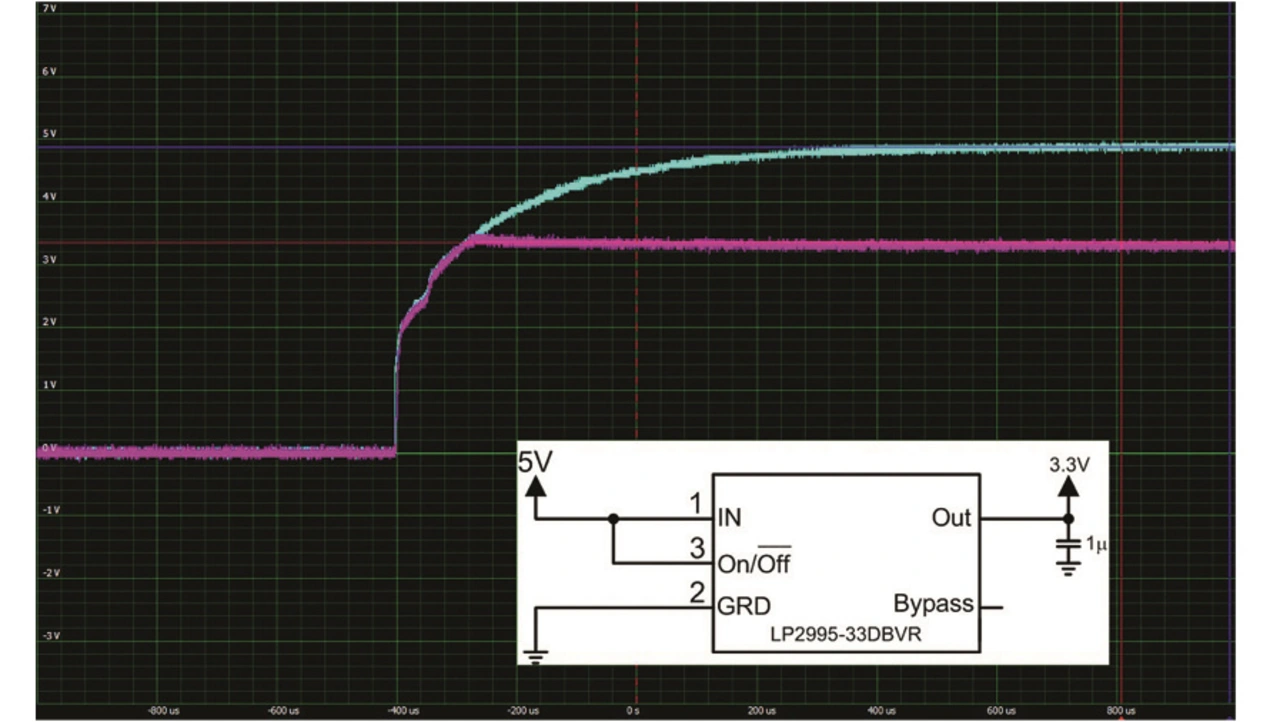

Ein gleichzeitiger Start ist relativ einfach einzurichten. Die höchste Ausgangsspannung wird an die Eingänge der Regler mit der niedrigeren Spannung angeschlossen (Bild 2). In diesem Falle ist die 5-V-Stromversorgung die höhere, sodass deren Ausgang mit dem Eingang des 3,3-V-Reglers verbunden ist. Daher steigen beide Ausgangsspannungen mit minimaler Spannungsdifferenz an, bis der 3,3-V-Regler seinen Regelpunkt erreicht.

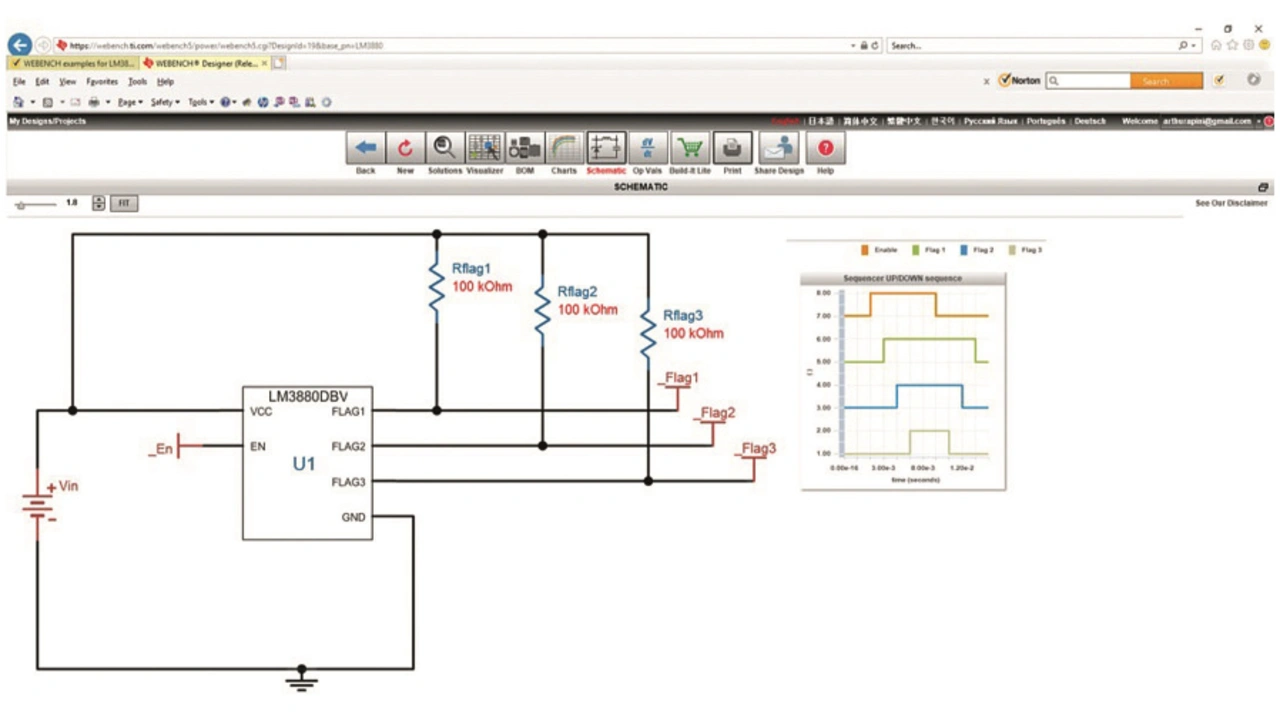

Diese sequenzielle Technik wird am besten mit einem dedizierten IC wie dem LM3880 von Texas Instruments implementiert. Dieser Baustein ist ein einfacher Stromversorgungs-Sequenzierer, der mehrere unabhängige Regler oder Stromversorgungen über ihre Freigabe-Eingänge steuern kann. Ein aktivierter LM3880 gibt seine drei Ausgangs-Flags mit individuellen Verzögerungen zwischen den Flags nacheinander frei, sodass die angeschlossenen Stromversorgungen dementsprechend nacheinander starten.

Das Herunterfahren erfolgt in umgekehrter Reihenfolge der Ausgangs-Flags. Ein Beispiel mit dem LM3880 lässt sich mithilfe der Software WEBENCH Power Designer implementieren (Bild 3). Dieses kostenlose Software-Tool unterstützt die Anwender bei der Entwicklung von Versorgungsschaltungen mithilfe von Schaltplänen, Stücklisten und simulierten Ergebnissen. Die Abbildung zeigt den Schaltplan und Diagramme, die Freigabe-Flags und die drei Flag-Ausgänge. Beim LM3880 sind die Verzögerungszeiten und die Reihenfolge fest, können aber über das integrierte EPROM ab Werk eingestellt werden. Texas Instruments bietet mit dem LM3881 auch einen Baustein, dessen Verzögerung sich per Kondensator einstellen lässt.

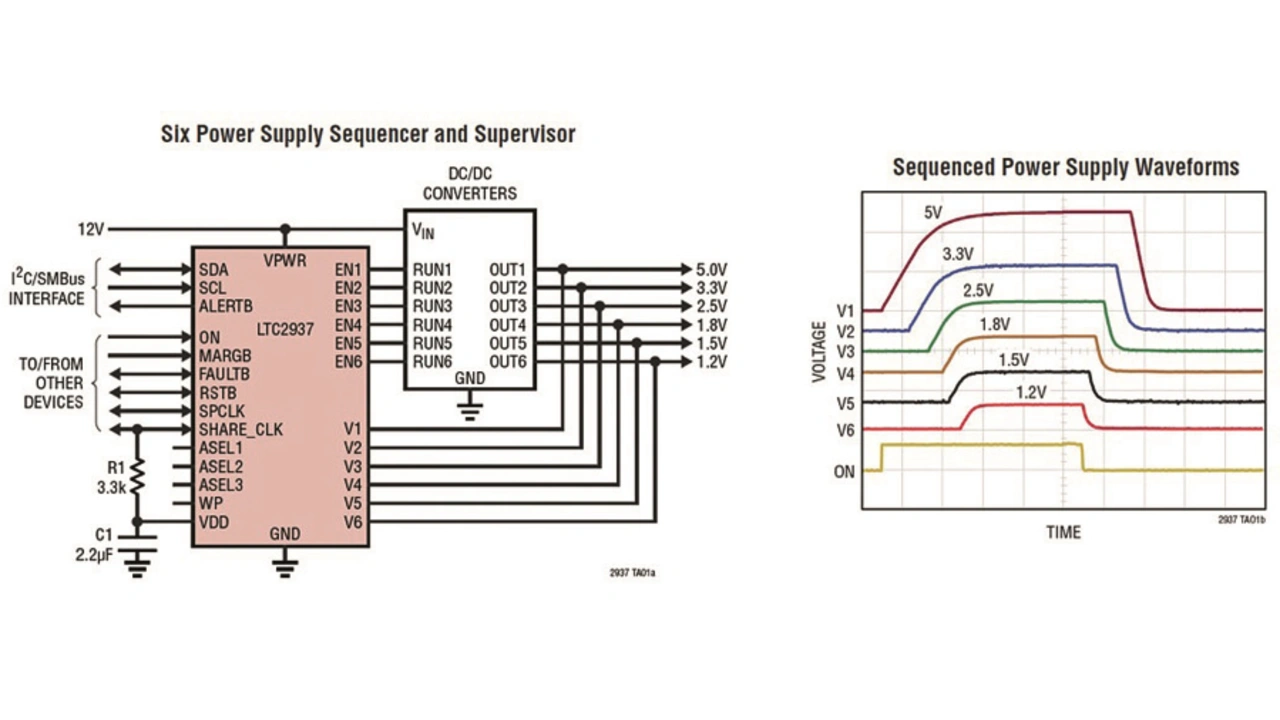

Ein etwas komplexerer Baustein ist der LTC2937 von Analog Devices. Dieser kann die Reihenfolge und Verzögerung von bis zu sechs Stromversorgungen oder Reglern steuern (Bild 4). Daneben überwacht das IC die Spannungen an diesen Schienen und erkennt Überspannungen, Unterspannungen, Ausfälle und blockierte Einschaltvorgänge. Der Baustein lässt sich so programmieren, dass er im Fall eines Fehlers die Stromversorgungen herunterfährt oder neu startet.

Die Fehler werden im internen EEPROM protokolliert. Der LTC2937 kann über I²C oder SMBus programmiert und gesteuert werden. Zur Programmierung eignet sich die Software LTpowerPlay von Analog Devices. Durch das integrierte EEPROM kann das IC ohne Software autonom agieren. Wenn ein System mehr als sechs Versorgungsspannungen benötigt, können mehrere LTC2937 verkettet werden und bis zu 300 Spannungsregler bedienen.

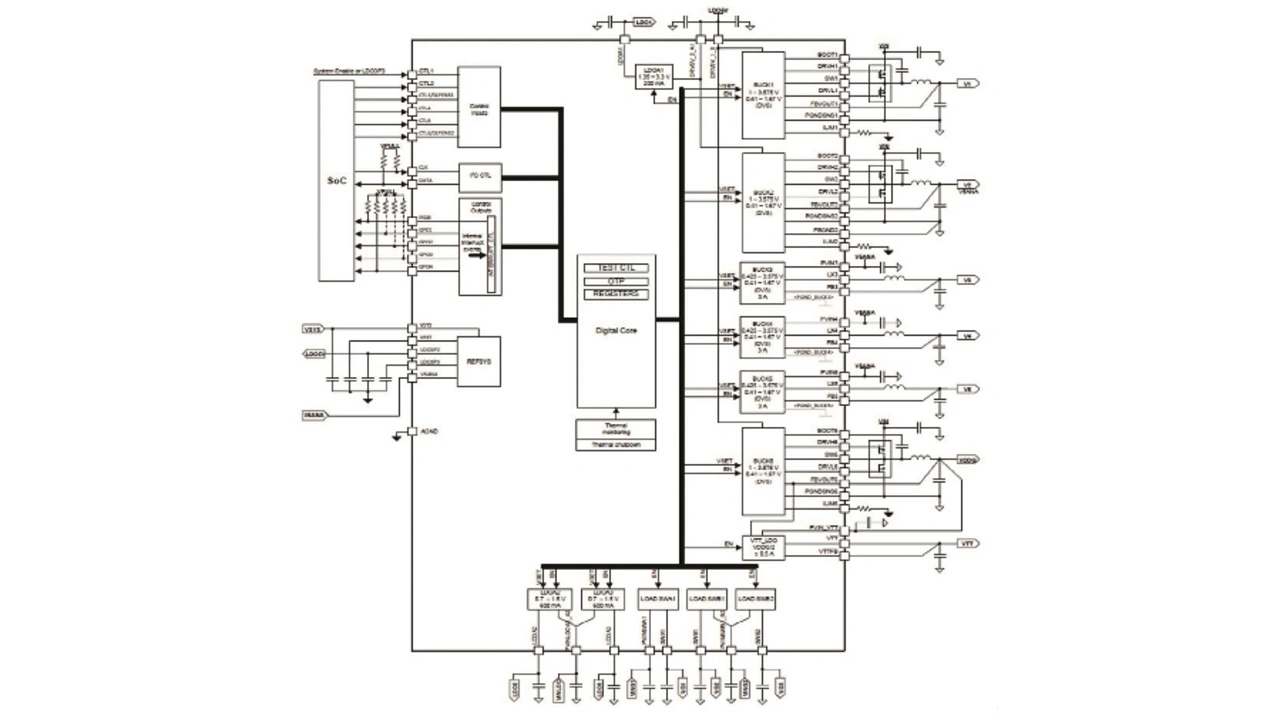

Für komplexe Multicore-Prozessoren, FPGAs und andere SoC-Bausteine bietet Texas Instruments den TPS650860 an. In einem einzigen konfigurierbaren Powermanagement-Baustein mit einer Eingangsspannung von 5,6 V bis 21 V sind 13 geregelte Ausgänge integriert, darunter sechs Tiefsetzsteller, drei Universal-LDOs, ein LDO mit DDR-Speicher-Terminierung sowie einige Lastschalter (Bild 5).

Drei Tiefsetzsteller besitzen eine integrierte Leistungsstufe, die drei anderen benötigen externe Mosfets. Sowohl Wandler als auch Controller verfügen über integrierte Messeingänge an den Ausgängen, um das Sequencing zu überwachen. Bei den Lastschaltern lässt sich die Anstiegsgeschwindigkeit steuern, um die drei Sequenzierungstypen sequenziell, ratiometrisch oder gleichzeitig zu implementieren. Der TPS650860 verfügt über eine I²C-Schnittstelle, um diesen über einen eingebetteten Controller oder über einen angeschlossenen SoC-Manager anzusteuern.

Zusammenfassend lässt sich sagen: Es gibt mehrere Methoden zur Steuerung der Start- und Ausschaltreihenfolge von einfach bis sehr ausgefeilt. Diese unterscheiden sich in der Anzahl der gesteuerten Stromschienen, der Genauigkeit und im Umfang der Steuerfunktionen sowie in den Kosten.