Karosserie-Elektronik

Schlüsselsuche ade mit Fahrzeug-Zugangskontrolle

Fortsetzung des Artikels von Teil 4

Kommunikation über die SPI-Schnittstelle

Sind alle für die jeweilige Anwendung benötigten Funktionen in der ROM-Bibliothek vorhanden, besteht keine Notwendigkeit, eigene Funktionen zu schreiben. In diesem Fall lassen sich die Transceiver und Empfänger über SPI-Befehle von einem Host-Controller steuern.

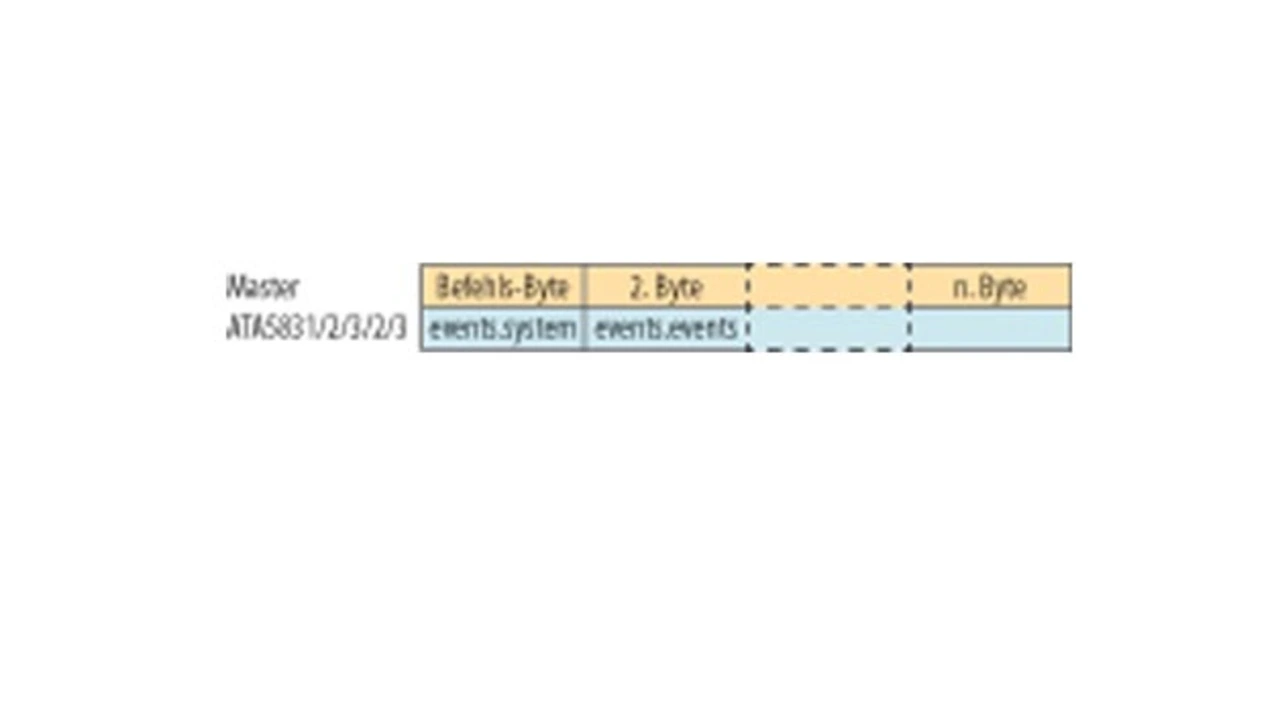

Ein wesentlicher Vorteil ist, dass der Host-Controller jederzeit die Kontrolle über den HF-Baustein behält, weil die SPI-Kommunikation immer die höchste Priorität hat und jeden anderen Prozess innerhalb des HF-Schaltkreises unterbrechen kann. Mit dem Befehlswort und dem zweiten Byte wird der interne Status des HF-Schaltkreises ausgegeben, so dass der Host-Controller erkennt, ob ein Systemfehler vorliegt oder ob die gewünschte Funktion erfolgreich abgeschlossen wurde. Tabelle 2 zeigt die Kommunikation über die SPI-Schnittstelle.

Die Steuerung eines HF-ICs über eine SPI-Schnittstelle ist nicht so schnell wie durch eine im Flash abgelegte Software. Damit die Bauteile dennoch in zeitkritischen Applikationen zum Einsatz kommen können, werden die SPI-Befehle mit einer möglichst hohen Datenrate gesendet: die maximale Übertragungsrate ist 500 kbit/s, zwischen zwei SPI-Befehlen muss eine Pause von mindestens 8 µs vorhanden sein, damit die Firmware Zeit hat, den vorhergehenden Befehl abzuschließen.

Diese hohe Datenrate basiert auf einer Änderung der SPI-Hardware im Vergleich zu anderen AVR-Mikrocon-trollern. Zusätzlich zum SPI-Datenregister gibt es noch einen 4 Byte großen Sende- und Empfangs-Buffer. Dadurch muss die Firmware nicht mehr jedes Byte einzeln in das SPI-Datenregister schieben. Am Anfang eines Lesebefehls und jeweils nach 4 Bytes prüft die Firmware, wie viele Bytes gelesen werden sollen. Sind das 4 und mehr Bytes, so schreibt die Firmware die nächsten 4 Bytes in den SPI-FIFO-Buffer.

- Schlüsselsuche ade mit Fahrzeug-Zugangskontrolle

- HF-Eigenschaften im Fokus

- Bauteile vereinfachen Entwicklungsprozess

- Vorteil: der Polling-Modus

- Kommunikation über die SPI-Schnittstelle

- Komfortable Polling-Konfiguration

- Eigene Flash-Programme

- Lösungen für den Fahrzeugzugang

- Die Autoren: