Seitenkanalangriffe

Auflösung schlägt Duplizierung

Fortsetzung des Artikels von Teil 4

Praxisbezug

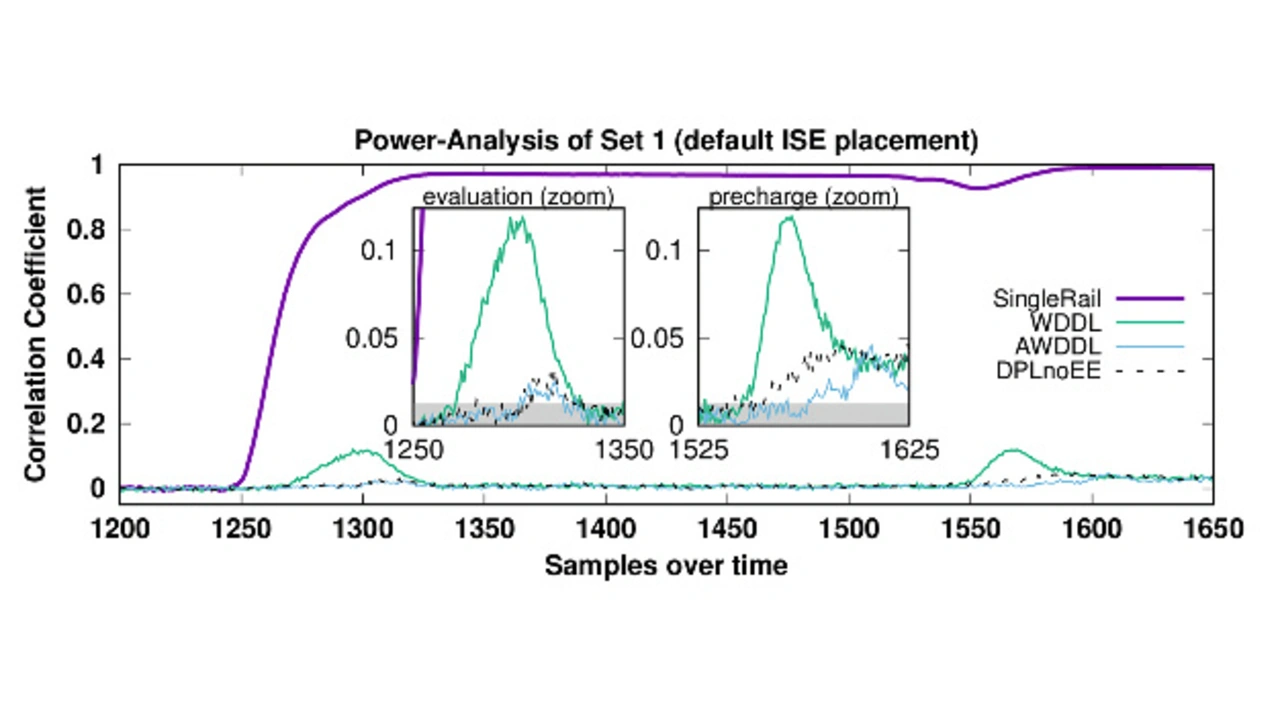

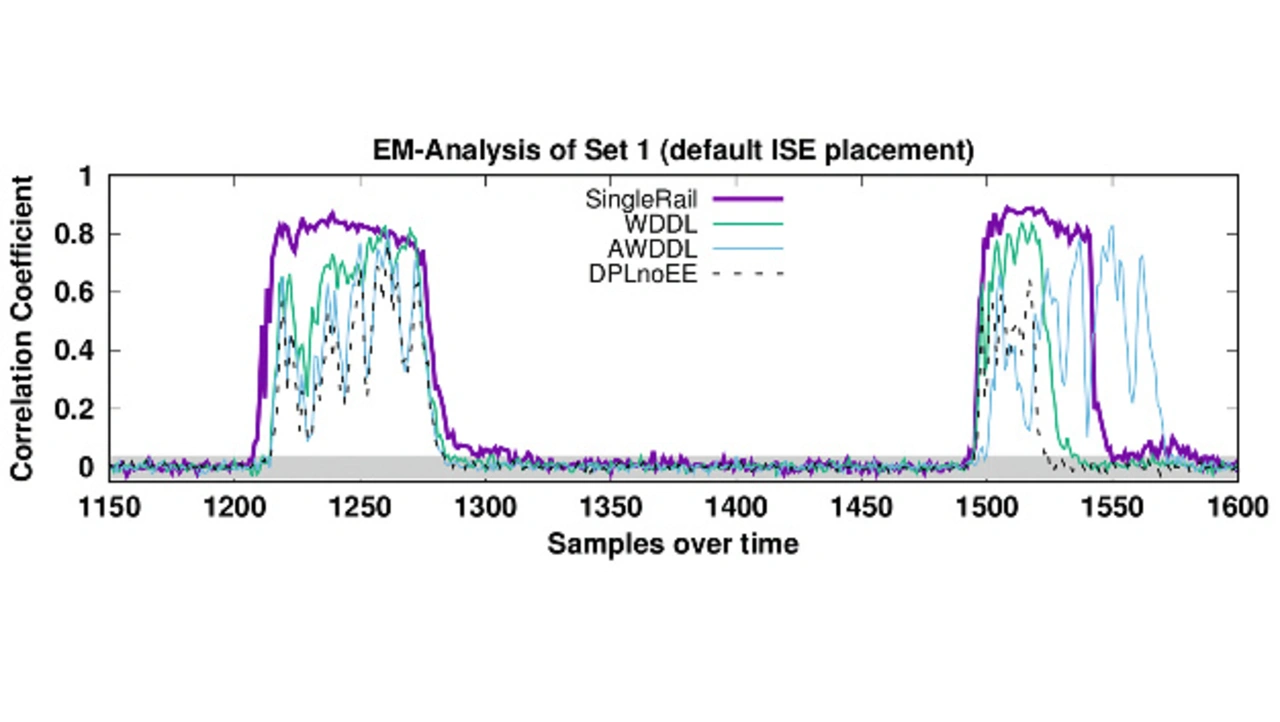

Mit den selben Eingangsdaten, Topologie und Messmethoden werden die Logikarten vergleichbar. Bild 5 und 6 zeigt den Vergleich einer mit Standard-ISE positionierten Logikfamilie der selben Topologie.

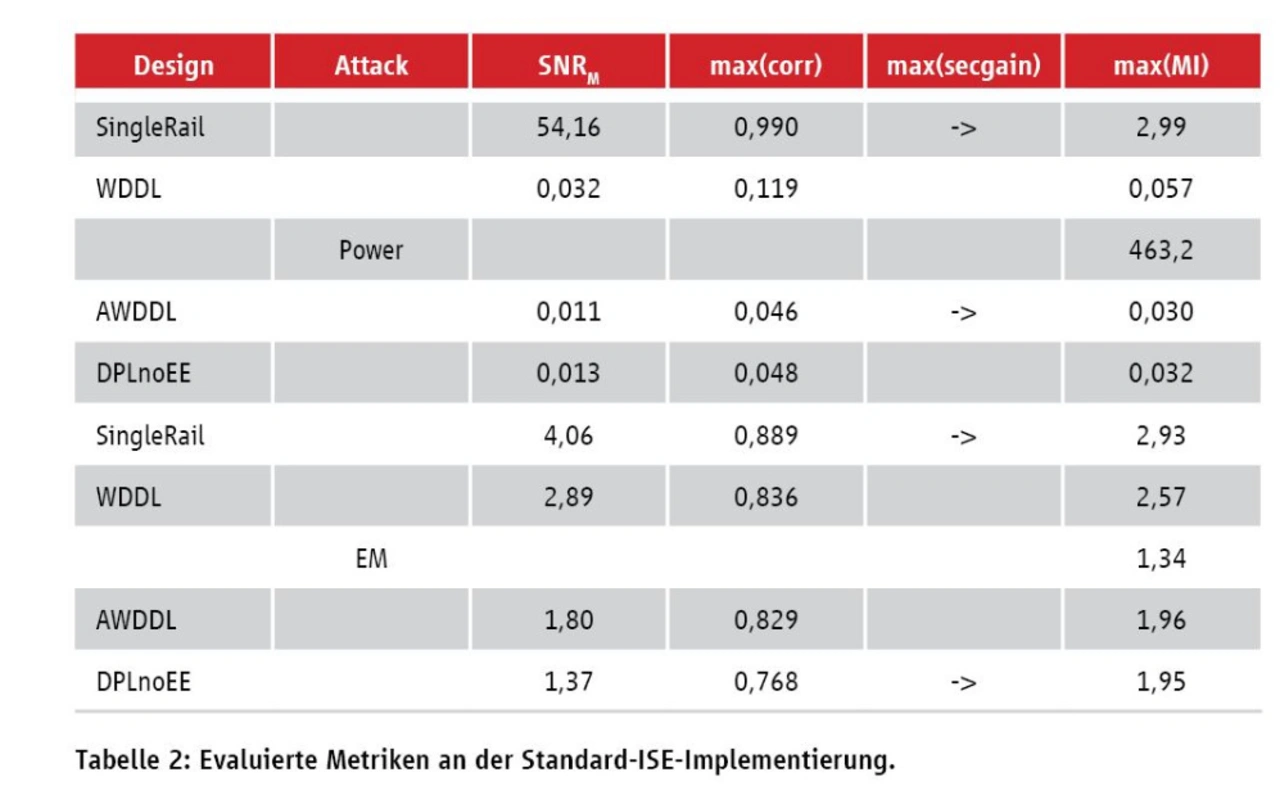

Zum Vergleich werden drei Metriken herangezogen: Der korrelationsbasierte Test von Durvaux et al. [5], der Korrelationen in der mittleren Leistungsaufnahme berechnet und einen Pearsonkorrelationskoeffizient angibt; Eine informationstheoretische Metrik quantifiziert die maximal extrahierbare Information auf Basis der Transinformation. Die dritte Metrik ist das oben beschriebene SNR.

Die korrelationsbasierte Leistungsanalyse unter Standard-ISE-Positionierung zeigt Bild 5. Jede der betrachteten Implementierungen zeigt zwei eindeutige Korrelationsausschläge die zur Berechungs- und Vorladephase gehören. Die beobachteten Korrelationen übersteigen die von Mangard et al. definierten Signfikanzschwelle von 0,012 erheblich.

Bei der Single-Rail-Variante steigt die Korrelation bis zu 0,99, nahe dem theoretischen Maximum von 1. WDDL zeigt ein Korrelationsmaximum von 0,119, DPLnoEE 0,048 und AWDDL 0,046. WDDL zeigt wegen seiner datenabhänigen Evaluations- und Vorladezeit die höchste Korrelation unter den Dual-Rail-Arten. Analog zu [6] fällt die Datenabhängigkeit von AWDDL nur marginal niedriger aus als in der Vorladephase, verglichen mit DPLnoEE.

Die Datenabhängigkeit zeigt in der AWDDL-Implementierung auch einen deutlichen Versatz, was auf die Eigenschaften der asynchronen Logik in AWDDL zurückgeht. Die Single-Rail-Variante weist eine extreme Datenabhängigkeit auf, sowohl in Evaluations- wie auch in der Vorladephase. Der Sicherheitszuwachs ist dabei 69,2 von Single-Rail auf WDDL, 6,15 von WDDL auf DPLnoEE und 1 von DPLnoEE auf AWDDL. Die informationstheoretische Metrik auf Basis der Transinformation zeigt dasselbe Verhalten (Tabelle 2).

Jobangebote+ passend zum Thema

Standard-ISE-Positionierung

In der Evaluierungsphase der lokalisierten Feldanalyse korrelieren alle Implementierungen auf etwa demselben Niveau. Die Single-Rail-Implementierung bei 0,89, WDDL und AWDDL bei 0,83 und DPLnoEE bei 0,77. Nur 10.000 Messungen reichten aus um diese Ergebnisse zu erreichen. Der Sicherheitszuwachs ist dabei 1,13 von Single-Rail auf WDDL, 1,18 von WDDL auf DPLnoEE und 0,858 von DPLnoEE auf AWDDL.

Damit ist die leichte Angreifbarkeit per EM-Feldmessung nachgewiesen. Da die selben FPGA-Konfigurationsdateien verwendet wurden, ist die Vereinfachung des Angriffs ausschließlich auf die verbesserte Messmethode zurückzuführen. Die informationstheoretische Metrik ist ebenfalls in Tabelle 2 aufgenommen worden. Bei dieser Methode schneidet AWDDL überraschenderweise schlechter als DPLnoEE ab.

Feldmessung versus Leistungsmessungen

Unter identischen Voraussetzungen des sonstigen Testaufbaus sind Unterschiede im Ergebnis nur durch die abweichende Messmethode möglich. Tabelle 2 fast die Ergebnisse beider Methoden an unterschiedlichen Implementierungen, anhand der drei Metriken zusammen. Im Ergebnis kann die Dual-Rail-Implementierung bei lokalisierten EM-Messungen nur einen marginalen Sicherheitsgewinn erreichen, womit vorherige Annahmen in Bezug auf die Sicherheit überdacht werden müssen.

Im Kern wurde damit auch die Frage nach der Unterscheidbarkeit der einzelnen Leitungen einer dualen Verdrahtung beantwortet. Dabei lassen sich zwei Szenarien betrachten um den Ausgang des Experiments zu beurteilen: Im ununterscheidbaren Fall würde ein signifikanter Zuwachs in der Datenabhängigkeit unter Deaktivierung einer kompensierenden Leitung erwartet. Im unterscheidbaren Fall sollte die Datenabhängigkeit von der Deaktivierung einer einzelnen Leitung nicht wesentlich beinflusst werden.

Bei der Leistungsanalyse trifft ersteres zu, bei der Feldmessung letzteres. Diese Beobachtungen werden auch von der Auswertung über die Transinformation bestätigt.

Verdichtete Positionierung

Um die Situation bei lokalisierter Feldmessung zu verbessern, wird eine höhere Packungsdichte untersucht. Dabei werden die HPWL- und SSST-Methoden betrachtet. Mit der HPWL-Positionierung die lediglich Topologie ändert ergeben sich keine Verbesserungen. In der dichteren SSST-basierten Positionierung ergibt sich ein Sicherheitsgewinn von 2,24.

Fazit

DRP-Logik erzielt auf FPGAs nur bei Leistungsanalysen den erwünschten Sicherheitsgewinn. Bei lokalisierter EM-Feldmessung mit hoher Auflösung ist jedoch kaum eine Erhöhung der Sicherheit vorhanden. Zukünftige Sicherheitsbegutachtungen solcher Logikarten sollten daher immer auch die lokale EM-Feldanalyse berücksichtigen.

Ein dichtere Positionierung der Logikelemente als mit der ISE-Standard-Methode erhöht die Sicherheit um den Faktor 2,24. Dies ist jedoch nur ein kleiner Zugewinn an Sicherheit, weshalb weitere Gegenmaßnahmen, zum Beispiel eine Maskierung, genutzt werden sollten. Wir erwarten, dass unsere Ergebnisse auch auf Logikarten anwendbar sind, die nach dem Duplizierverfahren arbeiten; mit dem größeren Abstand zwischen der zu untersuchenden Logik werden diese Implementierungen leichter angreifbar.(ct)

Referenzen

[1] W. Swartz - Placement Using Simulated Annealing. In C. J. Alpert, D. P. Mehta and S. S. Sapatnekar, editors, Handbook of Algorithms for Physical Design Automation, pages 311-325. Auerbach Publications, November 2008.

[2] Federal Information Processing Standards Publication (FIPS 197) - Advanced Encryption Standard (AES), 2001.

[3] D. Canright - A Very Compact S-Box for AES. In CHES 2005, volume 3659 of LNCS, pages 441-455. Springer, 2005.

[4] S. Mangard, E. Oswald, and T. Popp - Power Analysis Attacks: Revealing the Secrets of Smart Cards. Springer, 2007.

[5] F. Durvaux and F.-X. Standaert - From Improved Leakage Detection to the Detection of Points of Interests in Leakage Traces, pages 240-262. Springer Berlin Heidelberg, Berlin, Heidelberg, 2016.

[6] T. D. Cnudde et al. ePrint Archive, Report 2016/1080, 2016

- Auflösung schlägt Duplizierung

- Stand der Technik

- Topologie und Positionierung

- Messaufbau

- Praxisbezug