Seitenkanalangriffe

Auflösung schlägt Duplizierung

Fortsetzung des Artikels von Teil 1

Stand der Technik

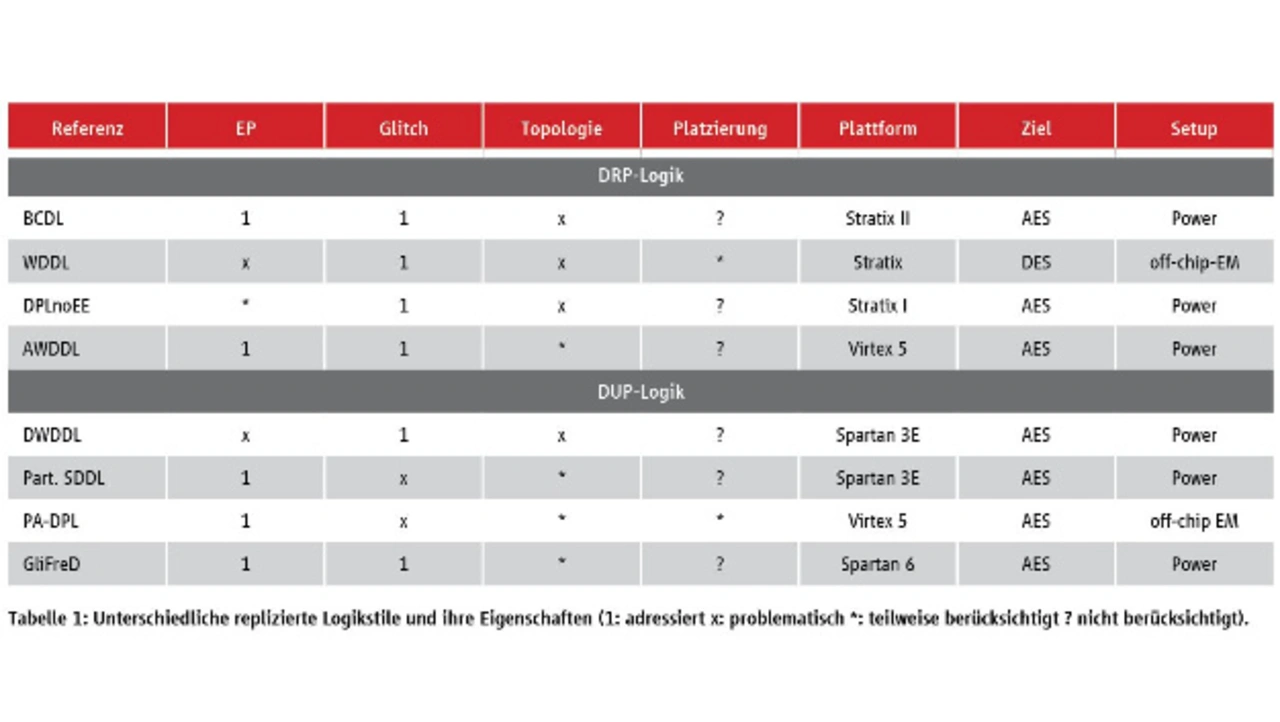

DRP-Logik-Gatter arbeiten in zwei taktgesteuerten Phasen: Vorladen und Evaluation. Dazu gehören die in Tabelle 1 aufgelisteten Logikstile. Bisherige Sicherheitsuntersuchungen dieser Logikstile äußern sich nicht quantitativ zur Bedrohung durch Feldangriffe, respektive zu einer möglichen richtungsabhängigen Messung der Emission einer Einzelleitung, die Teil einer zuvor beschriebenen dualen Verdrahtungslogik ist. Insbesondere bei großen Verdrahtungsnetzen können mit Abweichungen in der Netztopologie nicht alle dualen Verdrahtungsleitungen exakt abgeglichen werden: Die Timing-Informationen in den Xilinx-Werkzeugen sind dazu nicht präzise genug. Auch sind Parasitäre Kopplungen zwischen den Verbindungen möglich, die Störemissionen und Übersprechen innerhalb des FPGA-Blocks erzeugen.

Jobangebote+ passend zum Thema

Die Literatur kennt Hinweise darauf, dass die Feldemission in einer DRP-Implementierung mit der Positionierung vermindert werden kann. Tabelle 1 zeigt unterschiedliche DRP-Logikarten und das Potenzial einer On-Chip-Feldanalyse. Die alternativen Duplizierungsschemata sind durch das Auftreten von nicht-dualen Glitches, einfach kompromitierbar. Ein Vorteil ist jedoch, dass damit beliebige Logikfunktionen realisiert werden können, allerdings fällt der Abstand zwischen Original und Duplikat relativ hoch aus, was eine deutliche Schwachstelle für lokalisierte Feldangriffe bildet. Abhilfe gegen die Leistungsmessung schafft das GliFreD-Verfahren auf Kosten eines stark erhöhten Flächenverbrauchs im FPGA, durch eine große Anzahl zu nutzender Flip-Flops. Tabelle 1 listet dazu ebenfalls unterschiedliche Designs und ihre konzeptionellen Schwachstellen.

Im Allgemeinen kennt die Literatur viele Beispiele bei der die Feldmessung einer Leistungsmessung überlegen ist, obgleich kein direkter Vergleich erfolgte. Aus diesem Grund untersuchen wir ebenso die praktischen Grenzen einer lokalen Feldmessung in Abhängigkeit von Auflösung und Routingverfahren am Spartan-6 von Xilinx.

- Auflösung schlägt Duplizierung

- Stand der Technik

- Topologie und Positionierung

- Messaufbau

- Praxisbezug