Seitenkanalangriffe

Auflösung schlägt Duplizierung

Fortsetzung des Artikels von Teil 2

Topologie und Positionierung

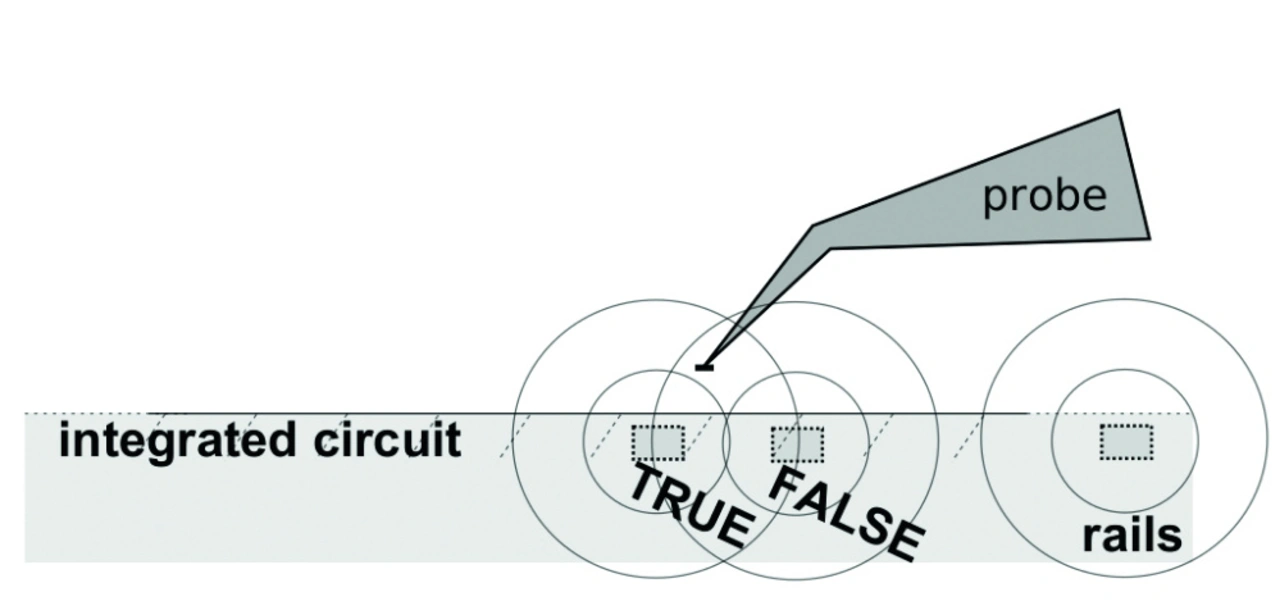

Sowohl bei DRP-Logik als auch Duplikationsverfahren gleichen komplementäre Gatter und Verdrahtung den Leistungsumsatz an. Allerdings sind Situationen denkbar, mit denen eine lokale Feldmessung die einzelnen Gatter oder Teile der Einzelverdrahtung auflösen kann (vergleiche Bild 2a), zum Beispiel unter asymmetrischer Feldstärke. Bei vorgegebener Positionierungsdichte und Topologie entscheidet die Auflösung somit über den Angriffserfolg.

Jobangebote+ passend zum Thema

Bild 1b skizziert die Dupliziermethode: Eine bereits verdrahtete Single-Rail-S-box wird dupliziert, symmterisch positioniert und die Funktionen komplementär ersetzt. Der Abstand der zueinander komplementärer Blöcke beträgt viele FPGA-Elementarzellen, sowohl Verbindungen als auch verarbeitende Blöcke der True- und False-Zellen liegen getrennt. Anders dazu die DRP-Logik, hier werden true- und false-Blöcke in der gleichen Look-Up-Tabelle beieinander gesetzt, jeder Ausgang zur Verdrahtung hin muss dann aber einzeln verdrahtet werden und ist nicht wie zuvor einfach kopierbar.

Je nach Qualität der Positionierung und der Topologie können DRP-Logiken daher viel enger gepackt werden als Logik nach dem Duplikationsverfahren. Der Nachteil: Wenn keine dichte Platzierung und Verdrahtung möglich ist, treten lokale Inhomogenitäten (großer Abstand zwischen Einzelleitungen eines dual-kodierten Bits) und Ungleichgewichte (abweichende kapazitive Lasten) auf. In der DRP-Logik-Topologie sollten solche Inhomogenitäten jedoch eigentlich schwieriger auszunutzen sein als in der LUT-separierten Realisierung eines Duplikationsverfahrens. Daher werden nur DRP-Arten hinsichtlich ihrer Resilienz gegen indirekte Leistungs- und Feldanalyseangriffe verglichen.

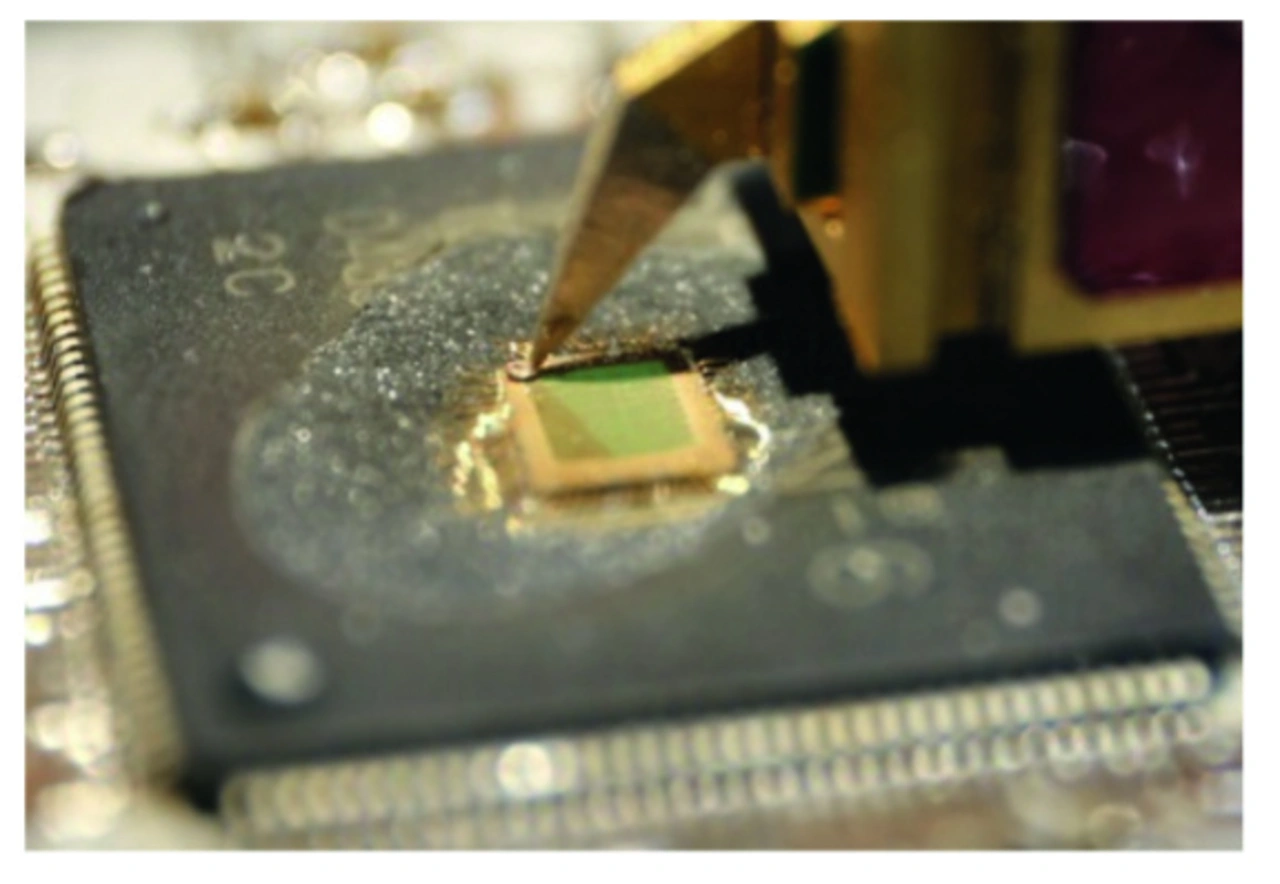

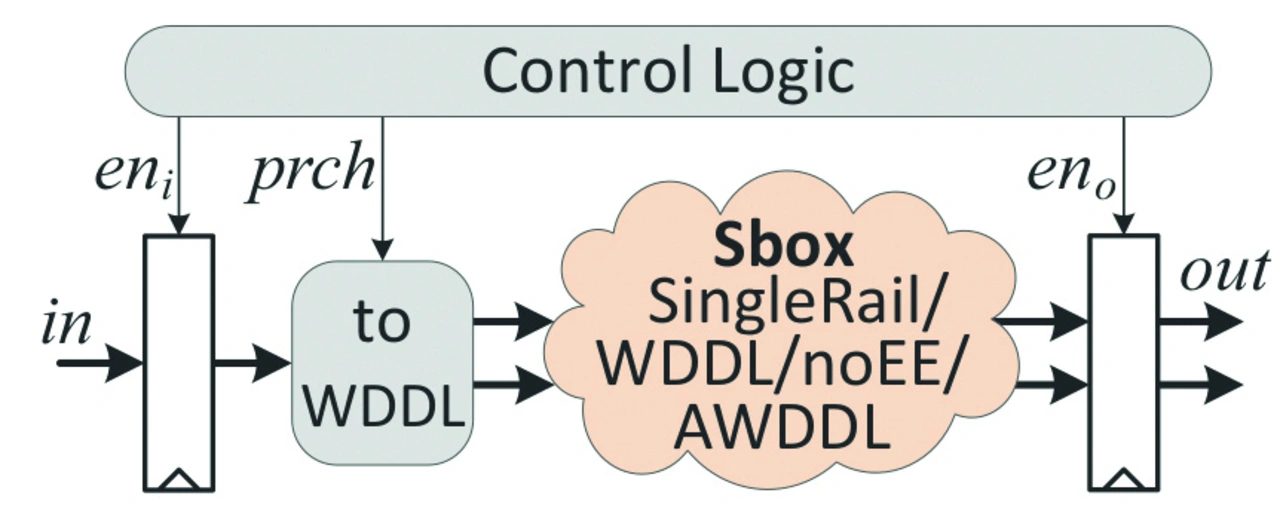

Die Positionierung der beschriebenen Logik im FPGA verwendet simuliertes Abkühlen (simulated annealing) [1]. Beim simulierten Abkühlen wird iterativ mit einem Abkühlfaktor und einer Kostenfunktion gearbeitet, solange bis die Positionierung ein definiertes Qualitätsmaß erfüllt. Dies erlaubt daher am Anfang größere Änderungen, wodurch lokale Minima und Maxima vermieden werden können. Die HPLW-Kostenfunktion optimiert dabei die Gesamtnetztopologie, eine eigens gewählte SSST genannte Kostenfunktion positioniert bevorzugt mit hoher räumlicher Dichte. Zur Analyse wurde zusätzlich zur AES-S-Box [2] eine Steuerlogik implementiert. Dabei wurde die auf eine geringer Gatteranzahl optimierte S-Box von Canright [3] verwendet. Alle Logikarten sind dabei in der selben Topologie und damit vergleichbar implementiert. Bild 3 zeigt ein Blockdiagramm des Designs.

Die Implementierung arbeitet folgendermaßen: In einem bestimmten Taktzyklus deaktiviert die Steuerlogik das prch-Signal und die »to WDDL«-Einheit sendet die Eingangswerte an die S-Box. Damit startet die Evalutionsphase. In der nächsten Taktzyklushälfte aktiviert die Steuerlogik das prch-Signal, die Vorladephase beginnt und setzt die Logik in der S-Box wieder auf den Ursprungszustand zurück. Die Schaltung ist so ausgelegt, dass nur der kombinatorischen Logik untersucht werden; Einflüsse aus der Registerstufe werden ignoriert.

Die Vergleichbarkeit der Einzeluntersuchungen besserte folgende Prozedur: Mit AWDDL als Ausgangspunkt, werden WDDL und DPL-noEE nur durch Änderung der LUT im XDL-File implementiert. Für die Single-Rail-Variante wird zusätzlich der False-Pfad in WDDL deaktiviert und die »toWDDL«-Konvertierung ebenfalls angepasst. Auf diese Art bleibt die Verdrahtung trotz unterschiedlicher Logik gleich. Zusätzlich wurden unterschiedliche Positionierverfahren getestet. In Summe sind daher folgende Gruppen mit allen vier Logikvarianten erzeugt worden, die innerhalb jeder Gruppe dieselbe Topologie besitzen:

- Menge 1: Standard-ISE-Positionierung unter Nebenbedingungen,

- Menge 2a: Proprietäre Positionierung mit HPWL,

- Menge 2b: Proprietäre Positionierung mit SSST.

- Auflösung schlägt Duplizierung

- Stand der Technik

- Topologie und Positionierung

- Messaufbau

- Praxisbezug