Das Mooresche Gesetz fortsetzen

Herausforderungen bei Design und Test von Chiplets

Fortsetzung des Artikels von Teil 1

Komplexität an der Schnittstelle

Die aktuellen Trends und Standards für Chipverbindungen lassen sich grob in zwei Kategorien einteilen: parallele Versionen mit niedriger Geschwindigkeit für Chiplets und serielle Versionen mit hoher Geschwindigkeit zwischen einzelnen Chips. Es ist schwer zu sagen, welcher Ansatz sich durchsetzen wird oder ob ein einziger Gewinner überhaupt notwendig ist, um den vielfältigen Gehäuseanforderungen der Industrie gerecht zu werden.

Was die parallelen und seriellen Standards unterscheidet, sind in der Regel übergeordnete Parameter wie höhere Protokollschichten, die Position der Signale im Gehäuse sowie die technischen Spannungen und Anstiegsgeschwindigkeiten. Die Ähnlichkeit zwischen diesen beiden Signalisierungsstrategien besteht darin, dass beide zum Teil die gleichen physikalischen Signalisierungsansätze verwenden.

Unabhängig davon, ob es sich um einen relativ langsamen, parallelen Signalbus zwischen verschiedenen Halbleiterchips oder um eine serielle Hochgeschwindigkeitsstruktur zwischen zwei oder mehr Chips, wie die PCIe-Schnittstelle und die zugehörigen Protokolle, handelt, ist die gesamte Systemlösung komplex. Die Komponenten der Bitübertragungsschicht können mehrere verschiedene Protokolle für die Datenkommunikation in einem Netzwerk verwenden.

Damit die Chiplet-Architektur erfolgreich ist

Für einen Erfolg der Chiplet-Architektur muss es Standardschnittstellen geben, damit das weltweite Ökosystem der Chiphersteller sich beteiligen kann. Intel hat seine Advanced-Interface-Bus(AIB)-Technologie für das UCIe-Programm [1] lizenziert, um die heterogene Integration mehrerer Chips in einem einzigen Gehäuse zu ermöglichen. In ähnlicher Weise hat sich der CXL (Compute Express Link) als führende Chip-zu-Chip-Protokollschicht etabliert.

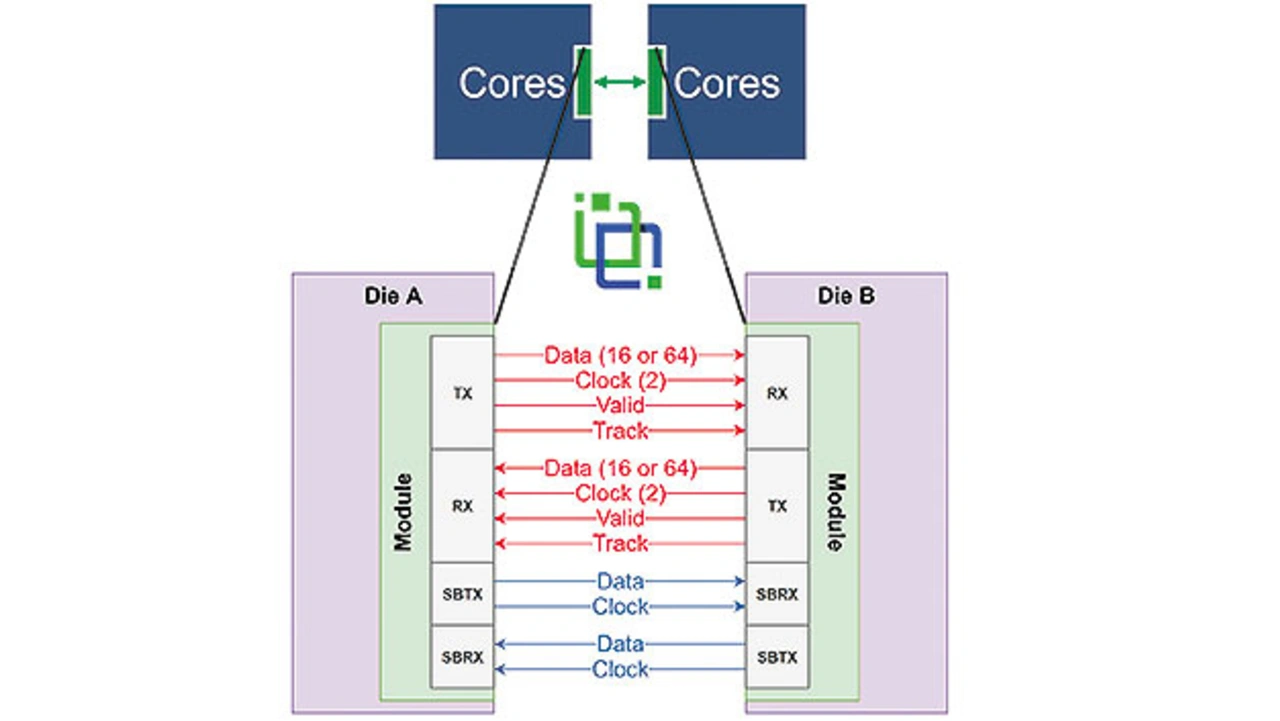

Das AIB-Verbindungskonzept zielt da- rauf ab, eine flexible Hochgeschwindigkeitsverbindung zwischen Chips und Chiplets zu schaffen. Wichtig ist, dass dieser Ansatz sich von den Baustein-zu-Baustein-Schnittstellen der letzten 25 Jahre unterscheidet, deren Ziel es war, komplexe Schaltungen zu verwenden, um hohe Geschwindigkeiten über wenige Drähte zu erreichen, wie z. B. bei PCI Express. Stattdessen verwendet die AIB eine sehr breite parallele Schnittstelle, die durch eine neue Technologie mit hoher Packungsdichte unterstützt wird. Dadurch, dass jede Leitung der Schnittstelle mit einer relativ niedrigen Geschwindigkeit läuft, wird die Schaltung für jeden Sender und Empfänger stark vereinfacht und benötigt nur minimale Siliziumfläche.

Jobangebote+ passend zum Thema

Bei der Betrachtung der Bandbreite im Vergleich zur Leistung ist die Bitübertragungsschicht von UCIe (Bild 3) sogar PCIe überlegen. Die erste Version von UCIe scheint bei einer begrenzten Anzahl von physischen Schnittstellen über die gleiche Entfernung um ein Vielfaches schneller als PCIe zu sein. Das Schlüsselwort ist hier »Entfernung«, da UCIe für eine sehr kurze Strecke auf einem Chipsubstrat entworfen wurde, während PCIe auf der Motherboard-Ebene implementiert wird. Hier laufen die Daten über eine längere Strecke und haben andere elektrische Anforderungen.

Herausforderungen bei Design und Test

Das Design für Chiplet-Architekturen ist eine vielfältigere technische Aufgabe als die Vorbereitung eines Single-Chip-SoC-Systems. Für die Erkundung des Designraums im Frühstadium werden Simulatoren benötigt, insbesondere für Multi-Chiplet-Bauteile, was vor allem auf den Mangel an Chiplet-Verbindungsmodellen zurückzuführen ist. Vorhandene fortschrittliche Tools für das Design von Schaltungen und Schaltungssimulationssoftware werden benötigt, um Entwicklungsteams bei der Bewältigung der Signalkomplexität, der inhärenten Dichte von Chiplet-Strukturen und heterogenen Schnittstellentechnologien zu unterstützen.

Zusätzlich zum Testen der parallelen Schnittstellen des Chiplets sind auch Tests der seriellen PCIe-4.0- und 5.0-Sender (Tx), -Empfänger (Rx) sowie der Bitübertragungsschichten und -protokolle der Kanäle erforderlich, um die Validierung nach der Fertigung zu beschleunigen. Die fortschrittliche PCIe-6.0-Input/Output(I/O)-Signaltechnologie wird noch leistungsstärkere I/O-Schnittstellen liefern. Die nächste Generation von PCIe wird auch zusätzliche Innovationen ermöglichen, darunter Beschleunigerverbindungen wie CXL und On-Chip-Kommunikation wie UCIe. PCIe-6.0-fähige Protokollanalysatoren und Messgeräte sind entscheidend für die Beschleunigung der Entwicklung, Einrichtung und Verbreitung von Hochleistungs-I/O-Technologien in der Chipindustrie.

Zusammenfassung

Bis vor Kurzem hatten nur die größten Chiphersteller das Budget und das Interesse, die Vorteile von Chiplet-Architekturen zu erforschen, indem sie firmeneigene Ansätze, proprietäres geistiges Eigentum (IP) für Verbindungen und Bestückungstechniken verwendeten. Das Aufkommen von Verbindungsstandards wie UCIe und OCPs Bunch-of-Wires senkt jedoch die Einstiegshürden für kleinere Firmen, um zum Chiplet-Ökosystem beizutragen. Messlösungen von Keysight bringen die passenden Prüftechnologien mit und leisten praxisorientierte Unterstützung in der Wertschöpfung.

Literatur

[1] https://www.intel.com/content/ www/us/en/newsroom/news/industry-leaders-foster-open-ecosystem-chiplet-based-design.html

Der Autor

Ben Miller

kam 2022 als Product Marketing Manager für digitale Produkte zu Keysight Technologies, wo er unter anderem Projekte im Bereich Hochgeschwindigkeitslösungen für Rechenzentren fördert. Miller hat einen Bachelor-Abschluss in Elektrotechnik von der University of Texas in Austin.

- Herausforderungen bei Design und Test von Chiplets

- Komplexität an der Schnittstelle