Das Mooresche Gesetz fortsetzen

Herausforderungen bei Design und Test von Chiplets

Die wirtschaftlichen Vorteile des Mooreschen Gesetzes haben nachgelassen. Besonders im Bereich der SoC-Produkte sind Halbleiterkunden verunsichert. Die Chiplet-Technologie verspricht nun, die Leistungs- und Kostenvorteile des Mooreschen Gesetzes auszuweiten. Was bedeutet das für Design und Test?

Bei den modularen Chips der Multi-Chip-Technologie, heute allgemein als Chiplets bekannt, werden einzelne Siliziumchips durch mehrere kleinere Chips ersetzt, die in einem gemeinsamen Gehäuse zusammenarbeiten. Die Integration verschiedener physischer Teile von Halbleiter-Dies in ein Lego-artiges Bauteil auf Gehäuseebene wird schon seit einiger Zeit genutzt. Das Interesse an diesem Ansatz wurde jedoch verstärkt, als sich das Mooresche Gesetz am entscheidenden 28-nm-Knotenpunkt etwa im Jahr 2011 zu verlangsamen begann.

Konzentration auf Chiplet-Architektur

Seitdem haben sich viele Unternehmen und Industriegruppen auf die Chiplet-Architektur konzentriert, darunter AMD, Intel und TSMC. Ziel dieser Aktivitäten war es, die Zeit bis zur Markteinführung und die Kosten zu reduzieren, indem vorentwickelte und getestete Chiplets in ein Gehäuse integriert werden. Wie bei früheren Innovationen in der Entwicklung von Halbleitertechnologien bestand die anfängliche Herausforderung in den konkurrierenden proprietären Designs ohne gemeinsame Standards. Inzwischen haben sich neue Standards herausgebildet. Nachfolgend geht es um die grundlegenden Trends in der Chiplet-Schnittstellentechnologie sowie vielversprechende Standards.

Jobangebote+ passend zum Thema

Herausforderungen bei Chiplets

Ein Chiplet ist ein Halbleiter-Die, der so entworfen wurde, dass er in verschiedene fortschrittliche Gehäuse mit anderen Dies (oder Chiplets) integriert werden kann. Dafür eignen sich die meisten existierenden Gehäusetypen, z. B. SiP (System-in-Package), 2,5D (planar oder vertikal) oder 3D-IC.

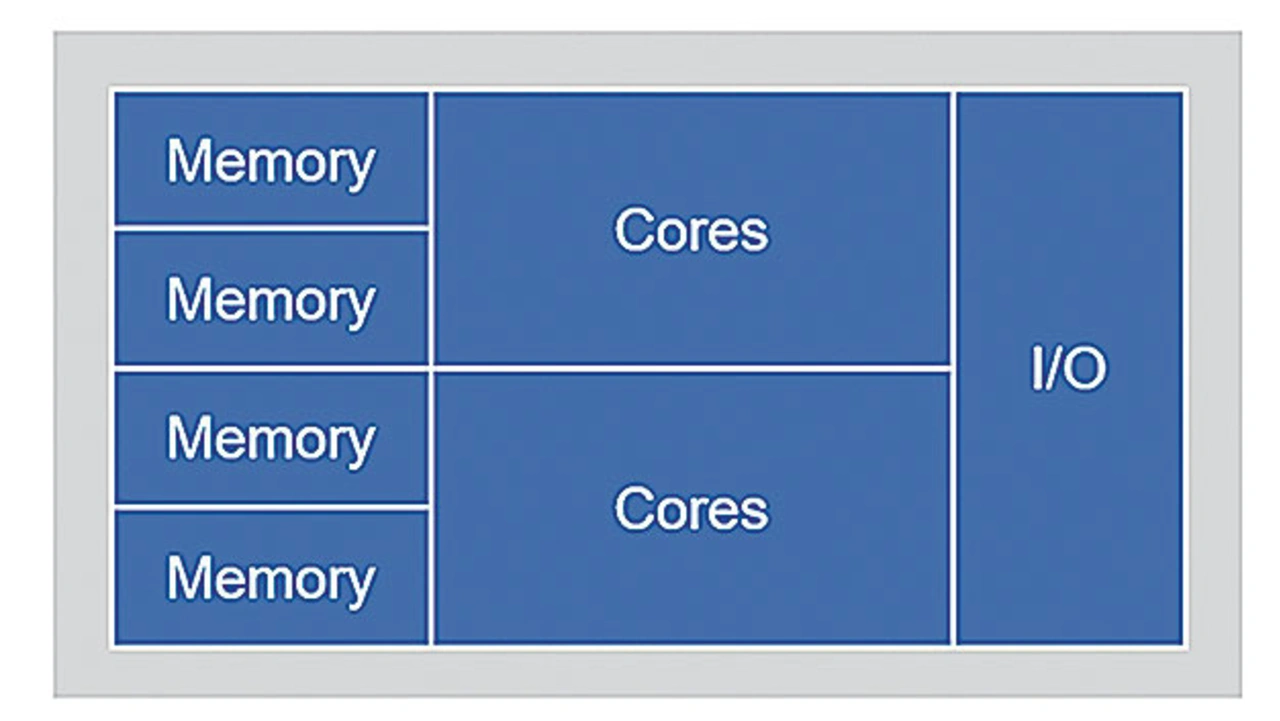

Chiplets basieren auf der heterogenen Integration mehrerer separat hergestellter Halbleiterkomponenten in ein übergeordnetes Bauteil, z. B. ein SiP, das mehr Funktionalität und Leistung zu geringeren Kosten bietet. Das steht im Gegensatz zum traditionellen monolithischen Chipdesign, das auf demselben Die zur gleichen Zeit hergestellt wird (Bild 1).

Vorteile des Chiplet-Designs

- Ein bemerkenswerter Vorteil des Chiplet-Designs ist die Wiederverwendung von IP (Intellectual Property) für verschiedene Produkte.

- Ein weiterer Vorteil ist die Flexibilität, da Chiplets im Gegensatz zu herkömmlichen SoC-Designs (System-on-a-Chip), die auf eine einzige Prozesstechnologie beschränkt sind, verschiedene Herstellungsprozesse für jedes Chiplet ermöglichen.

Heute entdecken immer mehr Chiphersteller die Vorteile der Chiplet-Architekturen, die auf der Grundlage bestehender und weiterentwickelter Gehäusetechnologie entstehen.

Und genau darin liegt der Schlüssel, nämlich darin, wie die Chiplets zusammengesetzt und miteinander verbunden werden können, um spezifische Anforderungen zu erfüllen.

Es ist nicht einfach, Chiplets für die Entwicklung von Multi-Die-Designs zu verwenden. Eine der größten Herausforderungen besteht darin, dass es keine standardisierte Die-to-Die-Verbindung oder Schnittstellenlösung gibt. Stattdessen gibt es mindestens zwei konkurrierende Chiplet-Schnittstellentechnologien – Intels Advanced Interface Bus (AIB) und das CEI-112G-XSR-Schema des Optical Internetworking Forum.

Jede Lösung hat Vor- und Nachteile

Zwei weitere Schnittstellenkonzepte wurden von der Industriegruppe ODSA (Open Domain-Specific Architecture) vorgeschlagen – BoW (Bunch of Wires) und OpenHBI (Open High Bandwidth Interface). Außerdem gibt es einige proprietäre Lösungen. Jede dieser Lösungen hat ihre Vor- und Nachteile, und es gibt noch keinen bevorzugten Standardansatz für das Design von Chiplet-Schnittstellen.

Die Chiplet-Entwicklung wird auch dadurch behindert, dass es keine branchenweite Unterstützung für Design-Tools und anerkannte Test- und Bestückungsmethoden gibt.

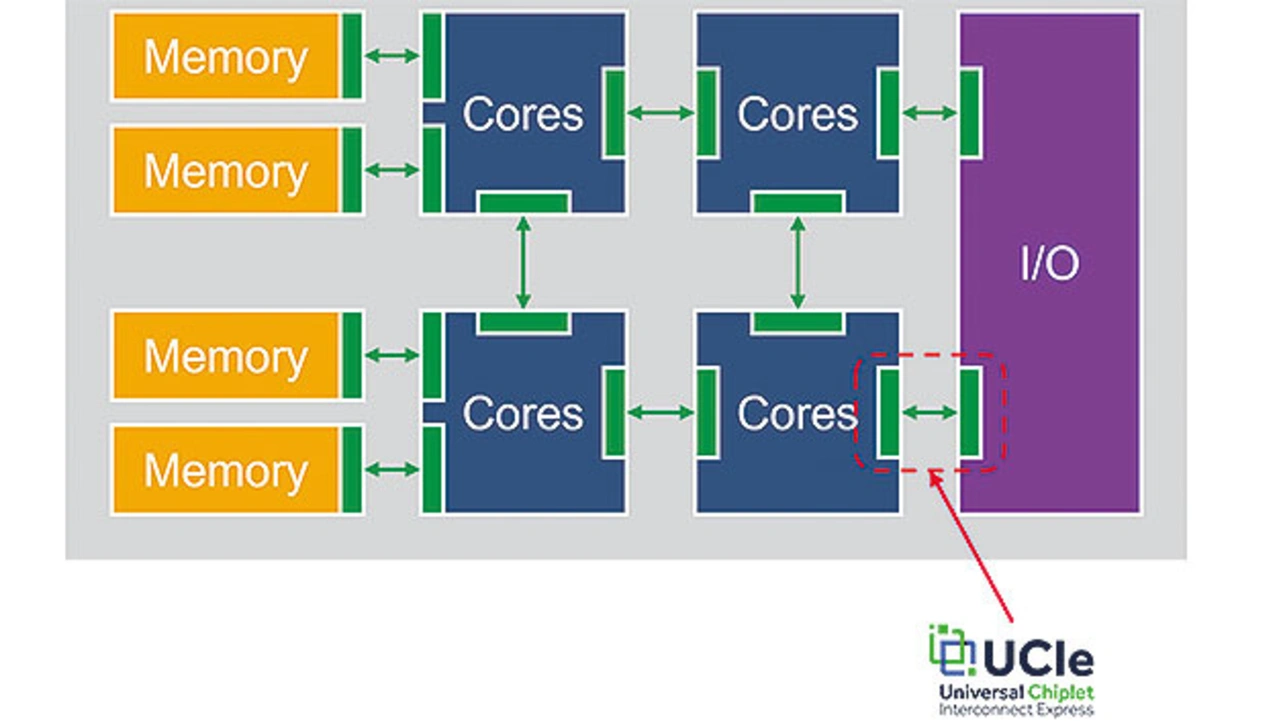

Damit sich die heterogenen Chiplet-Architekturen durchsetzen können, müssen sich die kommerziellen Chiphersteller auf Standards für die Die-to-Die-Signalkommunikation einigen. Zu diesem Zweck haben sich mehrere führende Halbleiterhersteller zusammengeschlossen, um einen Industriestandard für die Die-to-Die-Kommunikation zu unterstützen, den »Universal Chiplet Interconnect Express« (UCIe, Bild 2). Die Spezifikation soll ein offenes, herstellerübergreifendes Chiplet-Ökosystem schaffen.

Universal Chiplet Interconnect Express (UCIe)

Im März 2022 wurde die ratifizierte UCIe-1.0-Spezifikation veröffentlicht, die die physikalische I/O-Schicht, die Die-to-Die-Adapterschicht und einen Softwareprotokollstapel umfasst, der die bestehenden PCIe- und CXL-Industriestandards für Verbindungen nutzt:

- Bitübertragungsschicht: die elektrische Schnittstelle zum Medium, einschließlich der Sende- und Empfangskomponenten.

- Die-to-Die Adapterschicht: Dieser Mechanismus übernimmt das Link-Management, die Protokoll-Arbitrierung und die Vermittlung.

- Protokoll: Diese Schicht regelt die Datenübertragungen durch die Implementierung eines oder mehrerer von der UCIe unterstützter Protokolle, einschließlich PCIe und CXL.

Sowohl das PCIe- als auch das CXL-Protokoll – letzteres baut auf PCIe 5.0 auf – laufen auf der physikalischen UCIe-Verbindung. Ein Ziel von UCIe ist es, auf der Ebene des Chipgehäuses das zu erreichen, was PCIe seit Jahrzehnten auf der Ebene der Leiterplatte erreicht hat. Der Vorteil der Verbindung von Systemen und IP auf Chipgehäuseebene gegenüber der Leiterplattenebene besteht darin, dass der Stromverbrauch erheblich reduziert, die Bandbreitenleistung verbessert und schließlich die Kosten des Produkts gesenkt werden können.

Chiplets müssen interoperabel sein

Der UCIe-Standard soll unabhängig von der Gehäusetechnologie sein. Angesichts der Vielzahl unterschiedlicher Gehäusetechnologien ist dieses Ziel jedoch nicht leicht zu erreichen. Das bedeutet, dass die Chiplets interoperabel sein müssen, d. h. sie müssen miteinander kommunizieren und Daten austauschen können. Neben dem UCIe-Standard hat sich der Compute Express Link (CXL) als möglicher Standard für die Chip-zu-Chip-Protokollschicht herauskristallisiert.

Andere Organisationen haben sich auf die UCIe-Architektur konzentriert. Das Open Compute Project (OCP) zum Beispiel hat eine Arbeitsgruppe namens »Chiplet Design Exchange« (CDX). Die Charta dieser Gruppe ist ein offenes Ökosystem, das dazu beitragen soll, Fragen zwischen An- bietern, die Chiplet-IPs in einem integrierten Paket bereitstellen, und deren letztendlichen Bereitstellungsansatz zu beantworten. Es sind die Liefermodelle, die in einem Standard definiert werden müssen, wie z. B. thermische Gehäusemodelle und Testmuster für die gehäusten Chiplets.

- Herausforderungen bei Design und Test von Chiplets

- Komplexität an der Schnittstelle