Manipulation des Mikrocontroller-SPI

AD-Umsetzer mit Nicht-Standard-SPI einsetzen

Fortsetzung des Artikels von Teil 2

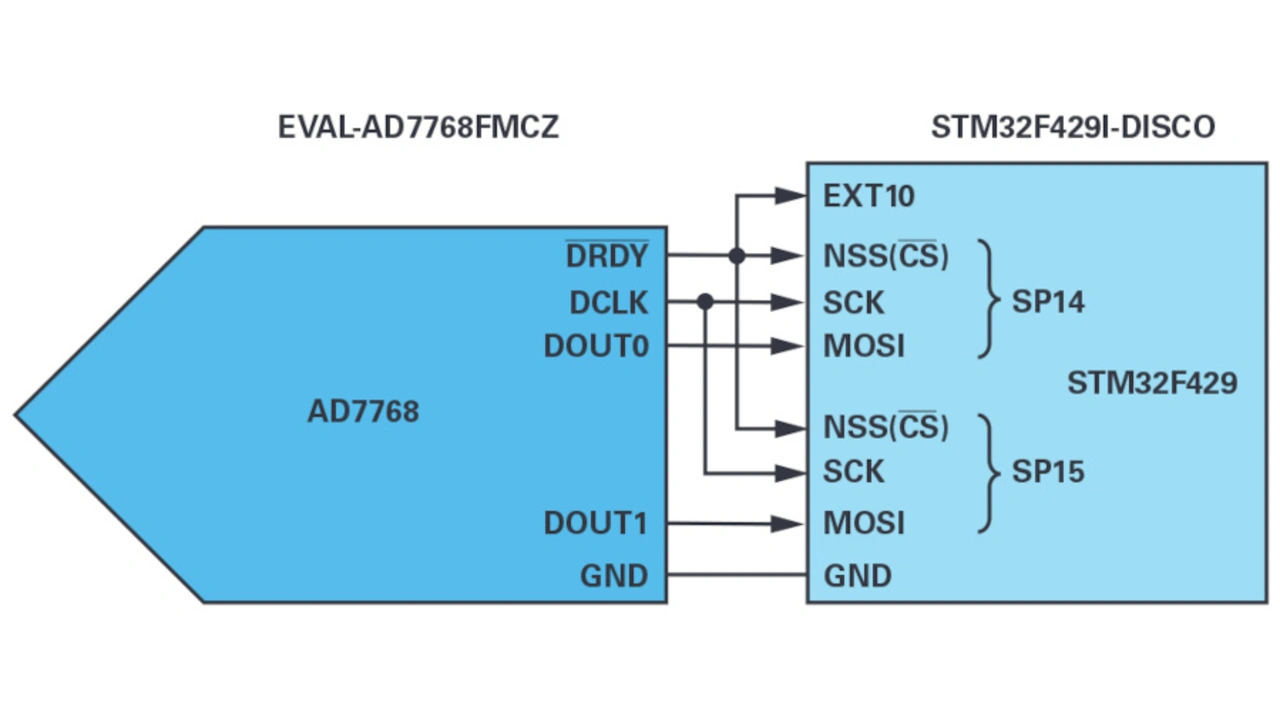

Lösung 2: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 über zwei DOUT-Leitungen

Bei der ersten Lösung wird nur DOUT0 zur Ausgabe aller Daten auf den acht Kanälen verwendet. Das Auslesen der Daten begrenzt also die ADU-Durchsatzrate auf 8 kSample/s. Gemäß Bild 1 kann die Ausgabe von Kanal 0 bis Kanal 3 auf DOUT0 und von Kanal 4 bis Kanal 7 auf DOUT1 die Datenübertragungszeit verkürzen. Dazu werden die seriellen Datenübertragungsleitungen entsprechend Bild 8 angeschlossen. Mit einer solchen Verbesserung kann die Umsetzungsrate leicht bis zu 16 kSample/s bei einem DCLK-Signal von 4 MHz betragen.

Jobangebote+ passend zum Thema

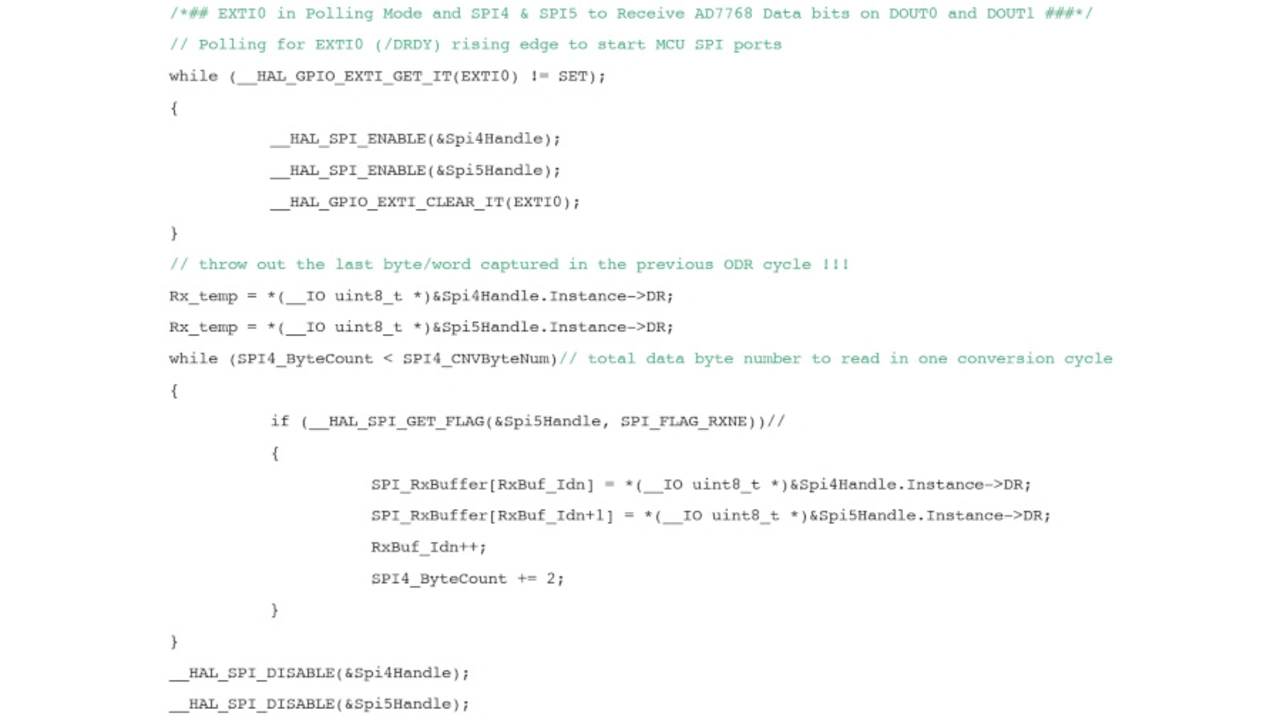

Die Firmware (Bild 9) kann die Polling-Betriebsart statt des Interrupt-Modus verwenden, um die Latenz vom Trigger der steigenden DRDY-Flanke bis zur Freigabe des SPI für den Datenempfang zu verkürzen. So ist eine ODR von 32 kSample/s bei einem DCLK-Signal von 8 MHz erreichbar.

- AD-Umsetzer mit Nicht-Standard-SPI einsetzen

- Lösung 1: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 über eine DOUT-Leitung

- Lösung 2: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 über zwei DOUT-Leitungen

- Lösung 3: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 über DMA

- Lösung 4: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 als SPI-Master und SPI-Slave über zwei DOUT-Leitungen.

- Code-Beispiele zum Download