Manipulation des Mikrocontroller-SPI

AD-Umsetzer mit Nicht-Standard-SPI einsetzen

Fortsetzung des Artikels von Teil 1

Lösung 1: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 über eine DOUT-Leitung

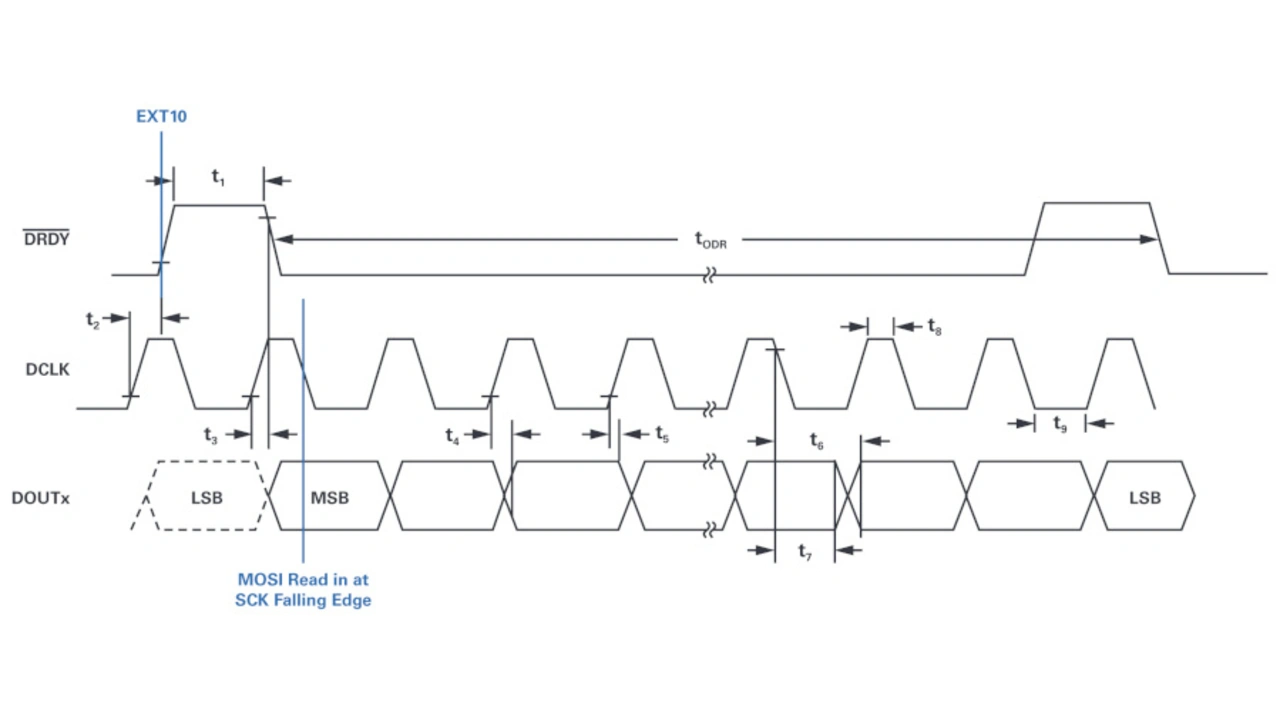

Wie Bild 4 zeigt, werden bei FORMAT0/1 = 11 oder 10 die Daten von Kanal 0 bis Kanal 7 nur auf DOUT0 ausgegeben. Im Standardbetrieb arbeitet der AD7768/AD7768-4 als Master und sendet Daten zum Mikrocontroller, DSP oder FPGA. Der AD7768/AD7768-4 liefert die Daten, den Datentakt (DCLK) und ein Wortsignal mit fallender Flanke (DRDY) an den Slave-Baustein.

Die Mikrocontroller der Familie STM32Fxxx von STMicroelectronics verfügen über mehrere SPI-Ports, die als SPI-Master oder -Slave mit typischen SPI-Timing-Modi konfigurierbar sind. Die im folgenden Abschnitt vorgestellten Methoden sind auch auf andere Mikrocontroller mit 8-, 16- oder 32-bit-Wörtern anwendbar.

Bei den AD7768/AD7768-4 handelt es sich um acht- beziehungsweise vierkanalige simultan abtastende Sigma-Delta-A/D-Umsetzer. Sie enthalten pro Kanal einen Sigma/Delta-Modulator und ein digitales Filter und ermöglichen eine synchrone Abtastung von AC- und DC-Signalen. Die Umsetzer-ICs erreichen einen Dynamikbereich von 108 dB bei einer maximalen Eingangsbandbreite von 110,8 kHz sowie typische Leistungsdaten wie eine integrale Nichtlinearität (INL, Integral Nonlinearity) von ±2 ppm, einen Offsetfehler von ±50 μV und einen Verstärkungsfehler von ±30 ppm.

Jobangebote+ passend zum Thema

Entwickler können sich beim AD7768/AD7768-4 für einen Kompromiss aus Eingangsbandbreite, Ausgangsdatenrate und Verlustleistung entscheiden und einen von drei Power-Betriebsarten wählen, um Entwicklungsziele hinsichtlich Rauschen und Stromaufnahme zu erreichen. Aufgrund ihrer Flexibilität eignen sich die beiden Umsetzer-ICs für Schaltungen die als wiederverwendbare Plattformen für Low-Power-DC- und Hochleistungs-AC-Messmodule eingeplant werden können. Leider arbeitet die serielle Schnittstelle des AD7768 nicht in einem typischen SPI-Timing-Mode – und der AD7768 fungiert als serieller Schnittstellen-Master. In der Regel müssen Entwickler ein FPGA/CPLD als Controller verwenden.

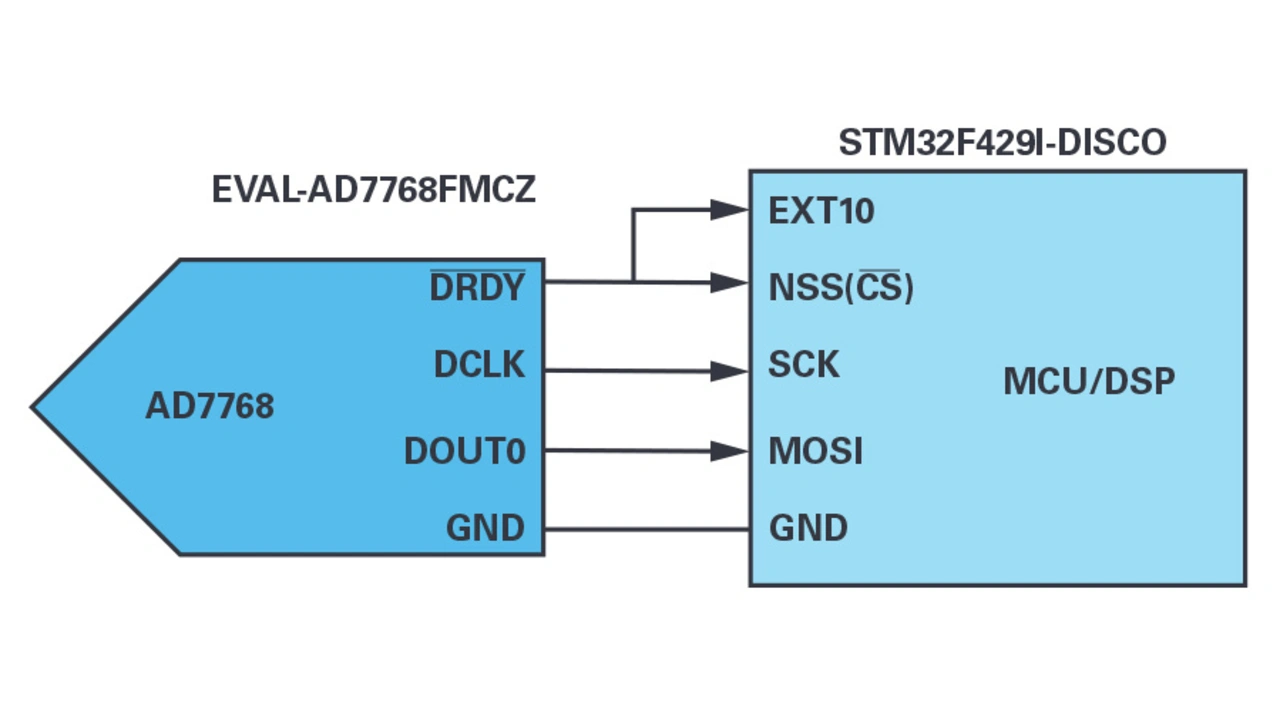

Für das folgende Beispiel werden die Evaluierungsmodule STM32F429I-DISCO mit dem STM32F429-Mikrocontroller und das EVAL-AD7768 mit dem ADU verwendet. Die SPI-Leitungen werden wir in Bild 5 gezeigt angeschlossen. In diesem Aufbau werden alle acht Kanaldaten des AD7768 nur auf DOUT0 ausgegeben.

Zu lösende Probleme:

- Der AD7768 arbeitet als SPI-Master. Somit muss das SPI des STM32F429 als SPI-Slave konfiguriert werden.

- Der DRDY-High-Impuls dauert nur einen DCLK-Zyklus, was kein typisches CS-Signal ist.

- DCLK gibt kontinuierlich Daten aus und DRDY hat Low-Pegel, wenn alle Datenbits auf dem Kanal ausgegeben sind.

Lösungsvorschlag:

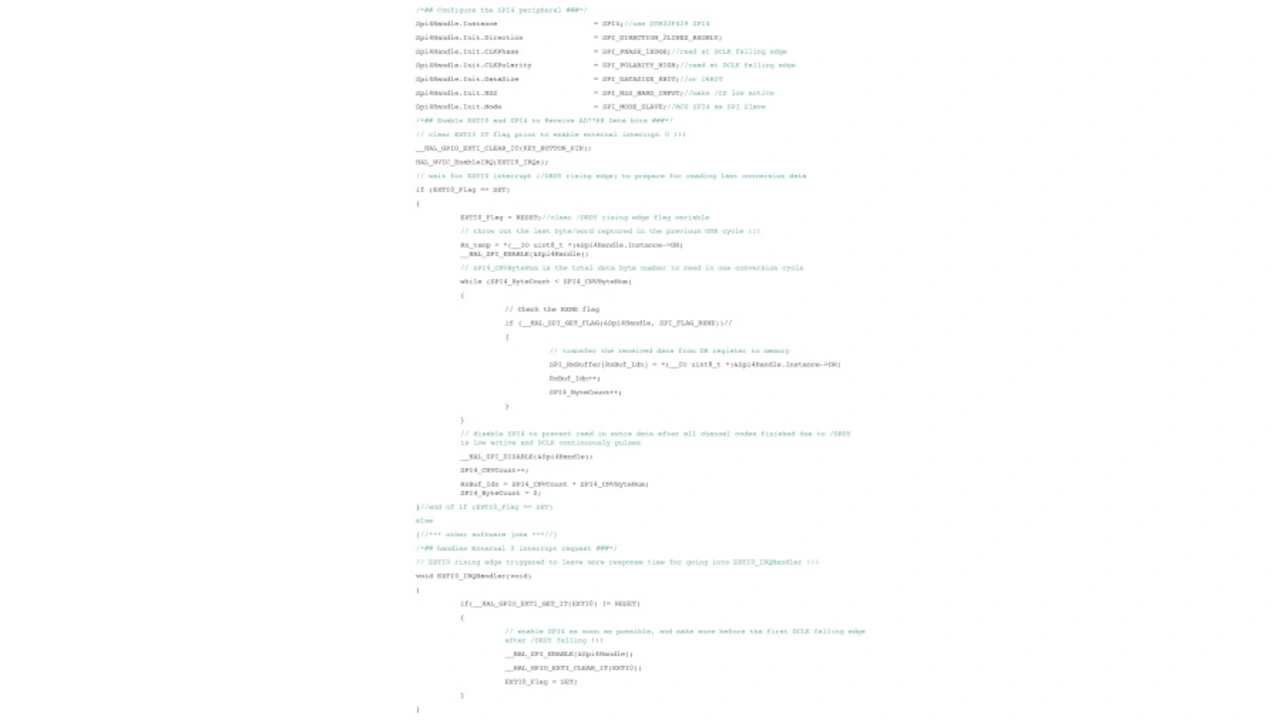

- Der SPI-Port des STM32F429, zum Beispiel SPI4, wird als Slave konfiguriert, um Datenbits auf MOSI mit DCLK zu empfangen.

- Der DRDY-Anschluss des AD7768 wird mit dem externen Interrupt-Eingang EXTI0 des STM32F429 und dem NSS-Pin (SPI CS) verbunden. Die steigende Flanke von DRDY löst die EXTI0-Handler-Routine aus, damit der SPI-Slave ab der ersten fallenden DCLK-Flanke, nachdem DRDY auf Low-Pegel geht, mit dem Empfang von Datenbits beginnen kann. Die Gestaltung des Timings ist hier kritisch.

- Nachdem alle Daten von Kanal 0 bis Kanal 7 empfangen wurden, sollte das SPI deaktiviert werden, um das Einlesen weiterer ungültiger Daten zu verhindern, da das Signal DRDY den SPI-Slave-CS auf Low-Pegel bringt und DCLK weiter toggelt.

Tipps für die Mikrocontroller-Firmware

Mit der Software (Bild 7) im Interrupt-Betrieb kann das Signal DCLK auf bis zu 4 MHz hochlaufen, und es wird eine Umsetzungsrate (ODR, Output Data Rate) von 8 kSample/s erreicht. Die Software sollte in den Interrupt-Handler eingreifen, um das SPI innerhalb von eineinhalb Perioden von DCLK (375 ns) zu starten. Damit die Software leichter in die Interrupt-Routine einsteigen kann, kann der Mikrocontroller die Daten bei der steigenden Flanke von DCLK lesen, wodurch eine zusätzliche halbe DCLK-Periode Zeit gewonnen werden kann. Da jedoch bei t5 (siehe Bild 5), der Anstieg von DCLK auf das ungültige DOUTx minimal –3 ns beträgt (–4 ns für IOVDD = 1,8V), sollte eine Laufzeitverzögerung (>|t5| + Haltezeit) auf DOUTx durch die Leiterbahnführung oder Puffer hinzugefügt werden.

- AD-Umsetzer mit Nicht-Standard-SPI einsetzen

- Lösung 1: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 über eine DOUT-Leitung

- Lösung 2: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 über zwei DOUT-Leitungen

- Lösung 3: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 über DMA

- Lösung 4: Lesen der Daten des ADU AD7768 mit dem µC STM32F429 als SPI-Master und SPI-Slave über zwei DOUT-Leitungen.

- Code-Beispiele zum Download