Wegen Ingenieurmangels

TSMC baut 450-mm-Fabs

Auf dem TSMC Technical Symposium 2011 in San Jose bestätigte die weltgrößte Foundry, zukünftig Chips auf 450-mm-Wafern zu fertigen. Die Begründung war überraschender als die Ankündigung an sich: Ingenieurmangel in der IC-Industrie.

Bislang hatte TSMC angegeben, aufgrund von Kostenvorteile gegenüber den Rivalen Globalfoundries, Samsung, UMC in die 450-mm-Fertigung einzusteigen.

Auf dem TSMC-Symposium 2011 in San Jose erklärte Dr. Shang-Yi Chiang (siehe Bild), Senior Vice President für Forschung und Entwicklung bei TSMC, dass sein Unternehmen für die 450-mm-Fertigung weniger Ingenieure benötigen würde. Konkret nannte er für einen 10-Jahreszeitraum die Zahl von 7.000 Mitarbeiter. Dies sei deshalb wichtig, weil mit einem Mangel an „guten Ingenieuren“ auszugehen sei, speziell an solchen, die auf Prozesstechnik spezialisiert seien.

Durch den Umstieg auf 450-mm-Wafer lassen sich rund 1,8x mehr Chips produzieren als auf einem 300-mm-Wafer. Dadurch könnte TSMC die Anzahl seiner Fabs reduzieren und damit Personal einsparen. Dazu gibt es allerdings auch wenig Alternativen, wenn man bedenkt, dass die Kosten für eine 450-mm-Fab auf 10 Mrd. Dollar geschätzt werden.

Auf der anderen Seite will die Foundry die Ausgaben für Forschung und Entwicklung sowie für Fab-Tools erhöhen.

Chiang erklärte, dass die 450-mm-Fertigung mit der 20-nm-Prozessgeneration starten wird. Die Pilot-Fertigungslinie wird in Fab 12 in Hsinchu, Taiwan, installiert. Zieltermin soll 2013 bis 2014 sein.

In diesem Zeitraum werden auch 300-mm-Fabs Chips in 20-nm-Technologie fertigen, die dann nach und nach umgestellt werden. Die erste vollständige 450-mm-Fab wird Fab 15 in Taichung, Taiwan, werden, die Produktion soll 2015 oder 2016 aufgenommen werden.

Jobangebote+ passend zum Thema

TSMC hat sogar schon Pläne für die Fab 15 in der Post-20-nm-Zeit: Mit Beginn der 14-nm-Fertigung sollen sich die Transistor-Strukturen von planaren Bulk-CMOS-Transistoren hin zu FinFET-Transitoren ändern.

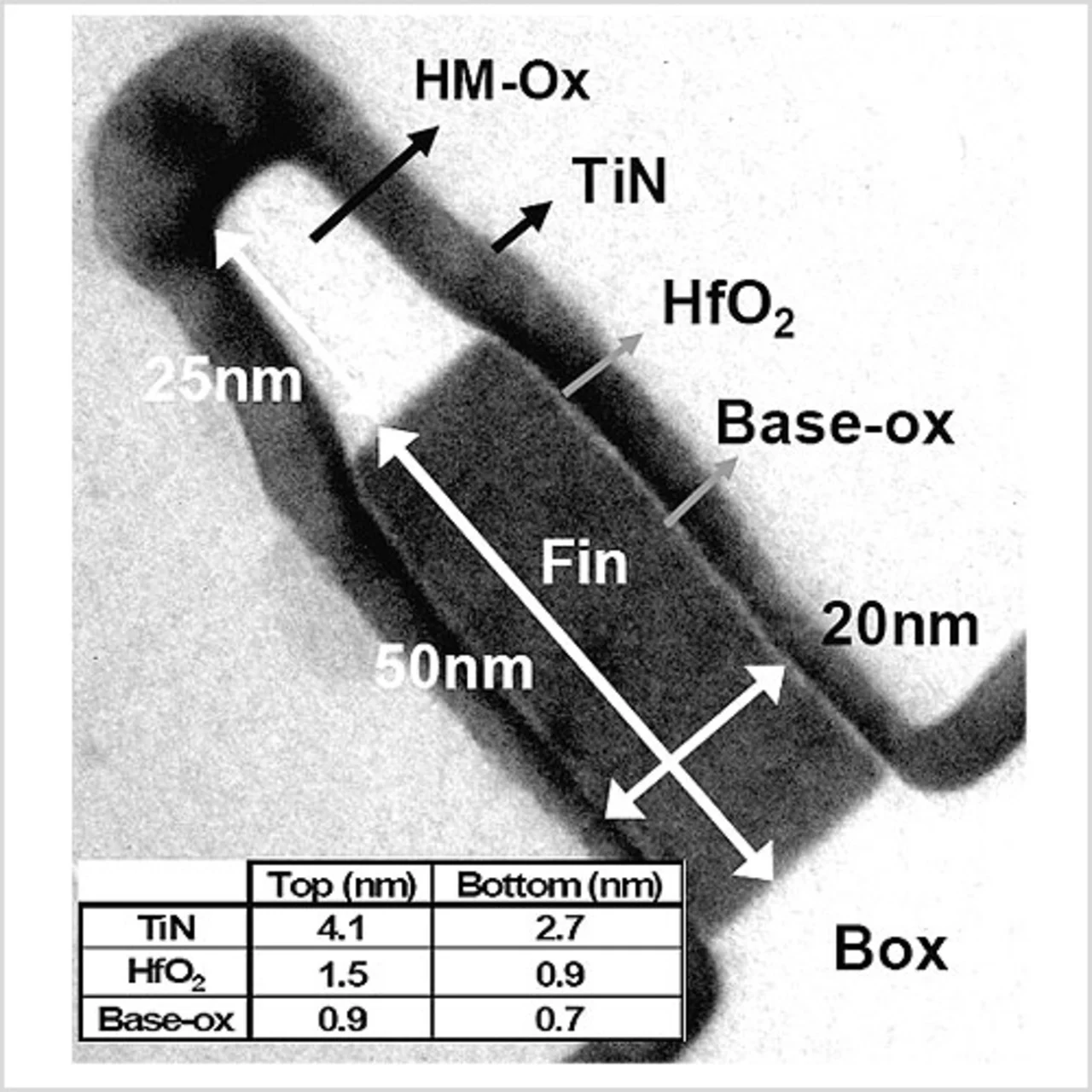

Das FinFET-Design basiert auf einer dünnen, vertikalen „Siliziumlamelle“, die den Leckstrom minimiert, solange der Transistor im Aus-Stadium ist. Es wurde Ende der 90er Jahre an der Universität Berkeley entwickelt. Der Ladungsträgerkanal wird beidseitig von den Gate-Elektroden umschlossen (siehe Bild).

Der Vorteil gegenüber planaren Transistoren ist, dass die Gate-Elektroden besser auf den Ladungsträgerkanal einwirken können und der Transistor somit schneller schalten kann. Dadurch verringern sich auch die Leckströme, was besonders bei zukünftigen, kleineren Strukturgrößen immer wichtiger wird. Die Zelle, die mit einem High-k/ Metall-Gate-Material (HKMG) entwickelt wurde, kann dazu beitragen, kleinere und schnellere Prozessoren herzustellen, die weniger Leistung aufnehmen.