Arbeitsspeicher der Zukunft

Speed-Limit (fast) unendlich – Teil 1

DDR3-SDRAMs werden in vielen modernen Computersystemen verwendet und erzielen Datenraten bis 1600 Mbit/s. Um die Rechenleistung darüber hinaus zu steigern, müssen künftige Arbeitsspeicher-Subsysteme höhere Datenraten aufweisen, dabei aber weiterhin eine niedrige Leistungsaufnahme und einen schnellen Zugriff bieten sowie ein wettbewerbsfähiges Preisniveau wahren. Dieser zweiteilige Artikel skizziert einige der entscheidenden Herausforderungen im Zusammenhang mit der nächsten Arbeitsspeicher-Generation und stellt Lösungen vor, mit denen sich die entsprechende Roadmap voranbringen lässt.

Getrieben von den neuesten Trends in Sachen Multicore, Virtualisierung und Prozessorintegration, besteht ein Bedarf an einer Arbeitsspeicher-Lösung mit Datenraten bis zu 3200 Mbit/s, während die Verlustleistung den Rahmen der DDR3-1600-Lösungen einhalten oder sogar unterbieten soll.

Abgesehen von der Energieeffizienz stehen künftige Speicherlösungen auch vor potentiellen Engpässen in Bezug auf die Zugriffszeiten und die Speicherkapazität. Um diese Herausforderungen zu bewältigen, entwickelte die Firma Rambus, die Technologien an Speicherhersteller lizensiert, ein Architekturkonzept für den Arbeitsspeicher der Zukunft. Diese Architektur stützt sich einerseits auf bestehende Technologien von Rambus wie zum Beispiel FlexPhase-Schaltungen sowie die FlexClocking- und die Dynamic-Point-to-Point-Technologie (DPP), führt aber andererseits auch neue Konzepte ein wie etwa das Near-Ground-Signaling und das Module-Threading. Gemeinsam eingesetzt, schaffen diese Technologien die Voraussetzungen dafür, einem künftigen Arbeitsspeichersystem einen um 50 % höheren Datendurchsatz zu verleihen, während die Leistungsaufnahme um 40 % geringer ist als mit jetzigen Techniken möglich.

Jobangebote+ passend zum Thema

Trends und wichtige Aspekte in der Industrie

Der erste wichtige Trend ist das Multicore-Computing, also das Integrieren mehrerer Prozessor-Cores in einen Chip. Ein zweiter Trend, der höhere Anforderungen an den Arbeitsspeicher mit sich bringt, ist die Virtualisierung. Dieser Begriff bezeichnet die Einrichtung mehrerer parallel arbeitender „virtueller Maschinen“, die alle auf derselben Hardware installiert sind, aber jeweils unter ihrem eigenen unabhängigen Betriebssystem laufen und ihre eigenen Applikationen verarbeiten. Ein dritter Trend ist die Integration des Grafikprozessors und des normalen Prozessors in ein und denselben Chip.

Alle Trends setzen eine Erhöhung der Speicherbandbreite voraus. In den letzten zehn Jahren haben sich die Arbeitsspeicher-Datenraten durchschnittlich alle vier bis fünf Jahre verdoppelt. Schreibt man diesen Trend fort, so wird die nächste Generation Datenraten bis zu 3200 Mbit/s unterstützen. Abgesehen von der Steigerung der Speicher-Datenraten verfügen die Computersysteme inzwischen über eine größere Zahl paralleler Speicherkanäle je Prozessor.

Eine weitere Methode zur Verbesserung der Rechenleistung besteht darin, den Speicher-Controller in den Prozessor zu integrieren. Dies kommt durch den Wegfall der zusätzlichen Chipsatz-Latenz tatsächlich der Rechenleistung zugute, doch können sich wegen der unterschiedlichen Betriebsspannungen von CPU und Speicher-Subsystem neue Schwierigkeiten ergeben.

Hinsichtlich des Energiebedarfs ist anzumerken, dass künftige Speichersysteme infolge des steigenden Leistungs-Niveaus einen immer größeren Anteil am Energiebedarf des Gesamtsystems haben werden, denn die Datenrate pro Pin nimmt ebenso zu wie die Zahl der Speicherkanäle.

Im Active-Mode führt ein DRAM aktiv Lese- und Schreibzugriffe aus, wobei sich die Leistungsaufnahme in drei Kategorien einteilen lässt: I/OSignalisierung, Systemtaktung und eigentliche Zugriffe im DRAM-Kern. In diesem Zustand mit maximaler Verlustleistung kann z.B. ein einziges ungepuffertes DDR3-Modul mit 1 Gbyte im aktiven Modus mehr als 3 A Strom aufnehmen, sodass auf den Speicher eine Leistungsaufnahme von nahezu 5 W entfällt. Mit der I/O-Signalisierung kommen weitere 2 W hinzu. Die daraus resultierende aktive Leistungsaufnahme der Speicher bei einem Prozessor mit vier Speicherkanälen kann sich auf über 25 W aufsummieren, und dementsprechend macht diese Leistung bei Server-Plattformen mit bis zu vier solchen Prozessoren unter Umständen mehr als 100 W aus.

Ungeachtet der Tatsache, dass die Betriebsspannung bei den DDR3-Speichern von 3,3 V auf 1,5 V zurückgenommen wurde, hat sich die aktive Leistungsaufnahme von einer Speichergeneration zur anderen erhöht, denn mit der höheren Speicherbandbreite wird die durch das Absenken der Versorgungsspannung erreichte Ersparnis vom höheren Leistungsbedarf infolge der höheren Datenraten, von den höheren Core-Zugriffsraten und von der größeren Zahl von Speicherkanälen aufgezehrt.

Auch wenn im Standby-Modus keine Zugriffe auf das DRAM erfolgen, müssen die chip-interne DLL-Funktion (Delay-Locked-Loop) und die Taktpuffer auf beiden Seiten der Schnittstelle auch zwischen den Transaktionen in Betrieb bleiben, sodass sie ununterbrochen Leistung aufnehmen. Selbst wenn die momentane Standby-Leistungsaufnahme bei einem typischen DDR3-DRAM nur etwa ein Viertel der aktiven Verlustleistung ausmacht, macht sie unter Zugrundelegung typischer Nutzungsmodelle weiterhin einen nennenswerten Teil des Gesamt-Energiebudgets der Speicher aus.

Mit zunehmender Datenrate kann die Zahl der von einem schnellen Speicherkanal unterstützten Module aus Gründen der Signalintegrität eingeschränkt sein. Bei früheren Speichergenerationen konnten bis zu acht SDRAM-Module mit 100 Mbit/s an einem Kanal operieren. Heute wird bei 1333 Mbit/s und mehr nur noch ein einziges DDR3-Modul unterstützt. Wenn sich an einen Kanal nur noch ein Modul anschließen lässt, müssen heutige Speichersysteme DRAMs mit mehr Dichte verwenden und von Puffern Gebrauch machen, um hohe Kapazitäten zu bieten. Jede dieser Alternativen aber bringt im Vergleich zum konventionellen Multi-Modul-Konzept Mehrkosten mit sich.

Ein Architekturkonzept für die Arbeitsspeicher der Zukunft

In Anbetracht dieser Anforderungen hat Rambus für künftige Arbeitsspeicher ein Architekturkonzept entwickelt, das den entscheidenden Kriterien Rechnung trägt.

Damit dies möglich ist, enthält die Speicherarchitektur eine Taktweiterleitungs-Architektur auf Basis der FlexClocking-Technologie. Befehle, Daten und die zugehörigen Adressen werden den DRAM-Bausteinen mit einer Topologie zugeführt, die den gegenwärtigen XDR- und DDR3-Speichersystemen ähnelt. Für das De-Skewing der Speicher-Transaktionen zu jedem Baustein sorgt der Controller mit Hilfe von FlexPhase-Timing-Angleichungen. An Stelle von Daten-Strobes schickt der Speicher-Controller ein Data-Clock-Signal an die DRAMs und erhält von jedem DRAM während der Lese- und Schreiboperationen ein Timing-Reference-Signal (TRS), um die Datenerfassung zu verbessern. Diese Taktungsarchitektur lässt sich mit controllerseitiger Kompatibilität zu aktuellen DDR3-DRAMs implementieren.

Die Architektur bietet außerdem Unterstützung für die Dynamic-Pointto-Point-Technologie (DPP). Diese behält im Interesse hoher Datenraten einerseits eine Punkt-zu-Punkt-Signalisierungs-Topologie bei, während sie andererseits die Voraussetzungen für die von einem Speicherkanal nativ unterstützte Modul-Upgrade-Fähigkeit und für erhöhte Kanalkapazität schafft. Um die aktive I/O-Leistungsaufnahme zu senken, nutzt die Architektur ferner die Near-Ground-Signalisierung mit deutlich niedrigerer Signalspannung. Darüber hinaus verringert die Near-Ground-Signalisierung die Kosten und die Komplexität bei der Integration eines Speicher-Controllers in einen Prozessor, der in einem 45-nm-Prozess oder weniger gefertigt wird. Threading-Techniken wie Threaded-Module, zweikanalige Module und Micro-Threading auf der Bausteinebene reduzieren die Leistungsaufnahme weiter und erhöhen die Speichereffizienz durch kleine Transfergrößen.

Die Taktungsarchitektur

Die Taktungsarchitektur macht von der FlexClocking-Technologie und weiteren Schaltungsverbesserungen Gebrauch, um hohen Datendurchsatz mit niedriger Leistungsaufnahme zu verbinden. Überdies unterstützt die Taktungs-Topologie die Abwärtskompatibilität zu DDR3.

Das zentrale Merkmal der Taktung ist die sehr geringe Standby-Stromaufnahme im Verbund mit einer kurzen Einschaltzeit. Die FlexClocking-Architektur erlaubt eine präzise Ausrichtung der Daten ohne den Einsatz einer DLL- oder PLL-Stufe (Phase-Locked Loop) im DRAM. Bei Hochleistungs-DRAMs greift man üblicherweise auf DLL- oder PLL-Schaltungen zurück, um die Timing-Schwankungen der Funktionen zum Senden und Empfangen von Daten gegenüber dem globalen Takt zu minimieren. Nachteilig an diesen Schaltungen ist, dass sie auch ohne aktive Datentransfers zwischen Speicher-Controller und RAM Strom aufnehmen. In neueren Server-Plattformen mit einigen hundert DRAMBausteinen kann die Standby-Leistungsaufnahme bis zu 60 % des gesamten Energiebedarfs der Speicher ausmachen. Bei der neuen Architektur werden Timing-Diskrepanzen zwischen Daten und Takt deshalb durch die FlexClocking-Architektur ausgeglichen, die im Standby-Status zwischen den Daten-Transaktionen keine Leistung aufnimmt.

Zum Minimieren der Leistungsaufnahme in Zeiten, in denen das DRAM nicht aktiv Daten sendet oder empfängt, sendet der Controller ein differenzielles Taktsignal („Data Clock“) an das DRAM-Modul. Das Routing erfolgt dabei auf ähnliche Weise wie im Fall des CCA-Busses (Command/Control/ Address) und des zugehörigen Takts. Data Clock und TRS sind nur während der Daten-Transaktionen aktiv und werden sehr schnell eingeschaltet.

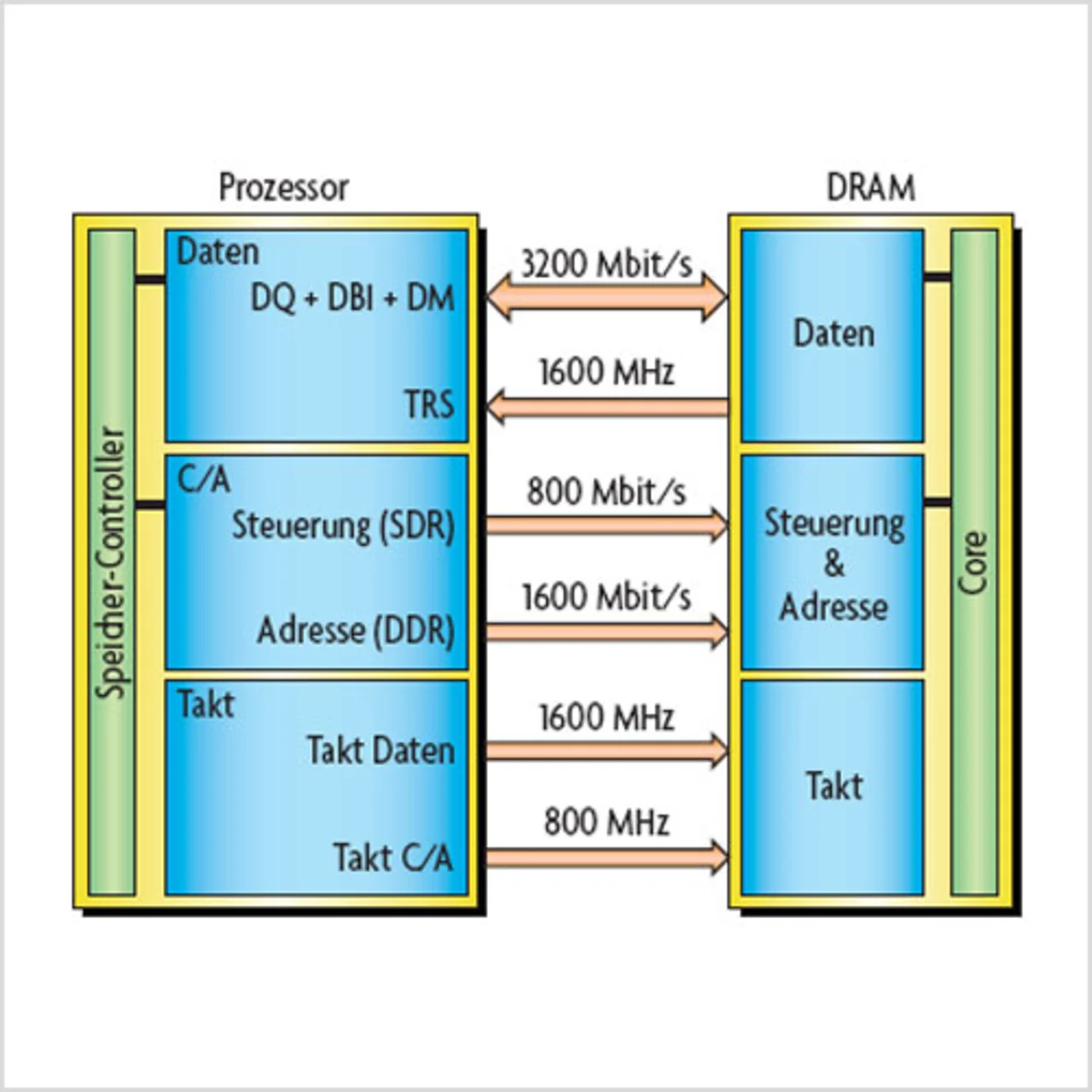

Der Data Clock hat die Nyquist-Frequenz der Datenrate, also beispielsweise 1,6 GHz bei Double-Data-Rate-Übertragungen mit 3,2 Gbit/s. In Verbindung mit der FlexClocking-Architektur kann die Verwendung eines separaten Datentaktsignals an Stelle des C/A-Takts hohe Datenraten möglich machen, ohne dass die DRAMs eine DLL- oder PLL-Funktion benötigen. Bild 1 zeigt ein Beispiel für eine künftige Speicherarchitektur mit Anbindung an den Prozessor.

- Speed-Limit (fast) unendlich – Teil 1

- Neue Bus-Techologien für hohe Datenraten

- Das DDP-Konzept