Arbeitsspeicher der Zukunft

Speed-Limit (fast) unendlich – Teil 1

Fortsetzung des Artikels von Teil 1

Neue Bus-Techologien für hohe Datenraten

Abwärtskompatibilität zu DDR3

Abwärtskompatibilität zu DDR3-Speicherbausteinen ist wichtig, da es beispielsweise möglich ist, dass erste Implementierungen künftiger Arbeitsspeicher-Controller bei Interims-Datenraten zwischen 1600 und 2000 Mbit/s mit DDR3-Speicherbausteinen kombiniert werden. Um das Design eines solchen Controllers zu vereinfachen, könnten künftige DRAM-Bausteine eine optionale Betriebsart unterstützen, in der bei Leseoperationen ähnlich dem Data-Strobe heutiger DDR3-Speicher am TRS-Pin ein Read-Capture-Signal an den Speicher-Controller ausgegeben wird.

Die pin-weise Kalibrierung kann zum Erzielen hoher Datenraten beitragen, indem gehäuse-, system- und bausteinbedingte Timing-Diskrepanzen kompensiert werden. Eine taktbasierte Referenz lässt sich über eine 64-bit-Schnittstelle leichter verteilen als eine Spannungs- oder Stromreferenz. Bei pin-weiser Kalibrierung muss das TRS des DRAM kein Strobe-Signal mehr sein, sondern es kann weitere sinnvolle Informationen enthalten (z.B. EDC). Dieses Signal kann vom Speicher-Controller zudem periodisch auf Zustandswechsel abgefragt werden, um die kalibrierte Timing-Integrität zu wahren. Die „Bimodalität“ lässt sich seitens des DRAM-Bausteins mit sehr wenig Aufwand umsetzen. In der einfachsten Ausführung reichen wenige Logikgatter, während bei vollwertigem EDC-Support einige hundert Logikgatter erforderlich sein können.

Jobangebote+ passend zum Thema

Kapazitätsgrenzen überwinden

Konventionelle Speicherbusse in SSTL-Technik (Stub Series Terminated Logic) in Personal Computern und Workstations bedienen sich einer „Stub-Bus“-Topologie, die den Anschluss von mehr als einem Speichermodul an eine elektrische Leiterbahn erlaubt. Mit dieser Topologie lässt sich die Speicherkapazität einfach aufrüsten, indem je nach Bedarf mehrere Module an den Bus angesteckt werden. Hiervon profitieren die Systemhersteller ebenso wie die Endanwender. Mit zunehmender Datenrate leidet jedoch diese Topologie unter mangelnder Signalintegrität, was der Geschwindigkeit des Speicherbusses Grenzen setzt. Ein Faktor ist die größte denkbare Belastung, wenn alle Steckverbinder mit Speichermodulen besetzt sind. Die Folge ist, dass die Zahl der unterstützten Speichermodule mit zunehmender Busgeschwindigkeit stetig sinkt. Durch diese Einschränkung reduziert sich die Gesamt-Speicherkapazität des Systems. Bei Arbeitsspeichern jenseits der DDR3-Generationwerden die Busgeschwindigkeiten auf ein so hohes Niveau steigen, dass es sehr schwierig werden wird, mehr als ein Modul an einen Speicher-Port anzuschließen.

In sehr schnellen Speichersystemen, wie sie beispielsweise von Grafikapplikationen benötigt werden, kommt in der Regel eine Punkt-zu-Punkt-Topologie zum Einsatz, was bessere Signalintegritäts-Eigenschaften ergibt und höhere Busgeschwindigkeiten zulässt. Unkomplizierte Upgrades sind mit Punkt-zu-Punkt-Topologien indes ausgeschlossen, da es nicht möglich ist, mehrere Module anzuschließen. Gerade die Fähigkeit, die Speicherkapazität durch Nachrüsten von Modulen aufzustocken, stellt aber in Computersystemen ein so wichtiges Merkmal dar, dass traditionelle Arbeitsspeichersysteme nicht auf Punkt-zu-Punkt-Topologien basieren.

DPP (Dynamic-Point-to-Point) ist die Bezeichnung einer neuen Signalisierungs-Topologie von Rambus, mit der sich die Speicherkapazität bei hohen Datenraten erhöhen lässt. Bei Hochleistungs-Computern wird hiermit die Möglichkeit zum Nachrüsten von Modulen ohne Einfluss auf die Leistungsfähigkeit des Speichersystems geschaffen. Unangetastet bleibt dabei die Abwärtskompatibilität zu den meisten Signalisierungs-Standards wie SSTL und RSL.

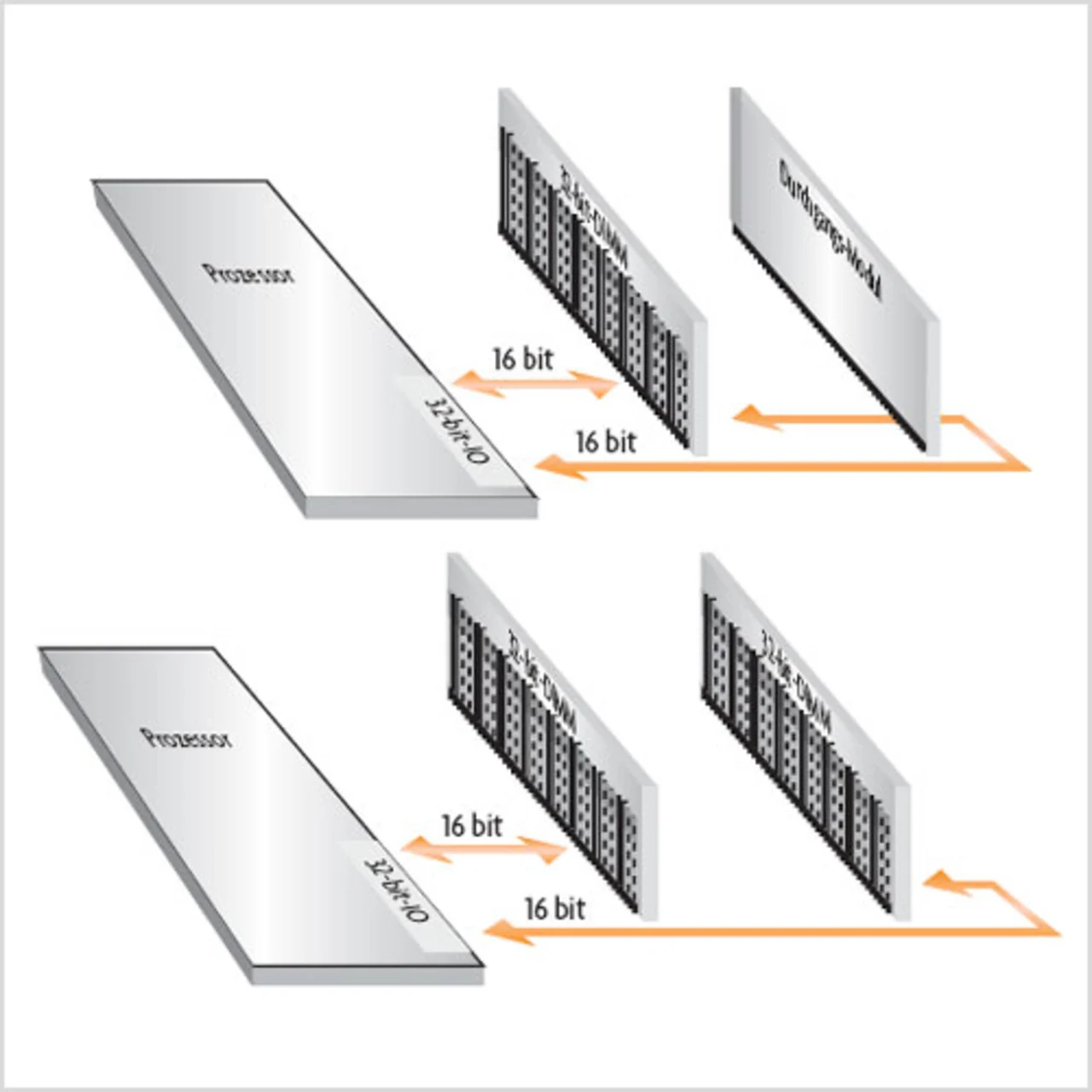

DPP nutzt eine Technik, mit der der Speicherkanal dynamisch so konfiguriert wird, dass alle Datenverbindungen eine Punkt-zu-Punkt-Struktur haben. Bei DPP-fähigen Systemen wird ein Teilabschnitt des Speicherbusses an jeden DIMM-Sockel des betreffenden Speicherkanals geführt. Der Speicher-Controller konfiguriert die Breite der DRAMs auf jedem Speichermodul abhängig davon, wie viele Steckplätze mit einem DRAM-Modul besetzt sind. DIMM-Sockel ohne DRAM-Modul werden mit passiven „Durchgangs-Modulen“ (Continuity Modules) bestückt, um die Punkt-zu-Punkt-Topologie aufrechtzuerhalten.

Bild 2 zeigt die logischen Darstellungen exemplarischer DPP-Architekturen. In einer DPP-Architektur mit nur einem aktiven Speichermodul (oben) ist der zweite, nicht genutzte Steckplatz mit einem kostengünstigen passiven Durchgangs-Modul bestückt, das zur Aufrechterhaltung der Punkt-zu-Punkt-Verbindung für die Hälfte der Signalleitungen zwischen dem aktiven Modul und dem Speicher-Controller dient. Wird die Konfiguration durch ein zweites aktives Modul erweitert (unten), stellt das zweite Modul die Daten für die zweite Hälfte der zum Speicher-Controller führenden Datenleitungen zur Verfügung. Das zweite aktive Modul tritt hierbei an die Stelle des Durchgangs-Moduls. Die aktiven Module werden so umkonfiguriert, dass jedes gegenüber den nicht konfigurierten Modulen die doppelte Anzahl adressierbarer Speicherstellen und die halbe Anzahl DQs aufweist. Die Speicherkapazität des Systems insgesamt wird hiermit also verdoppelt, ohne die schnelle Punkt-zu-Punkt-Signalisierungs-Topologie zu beeinflussen.

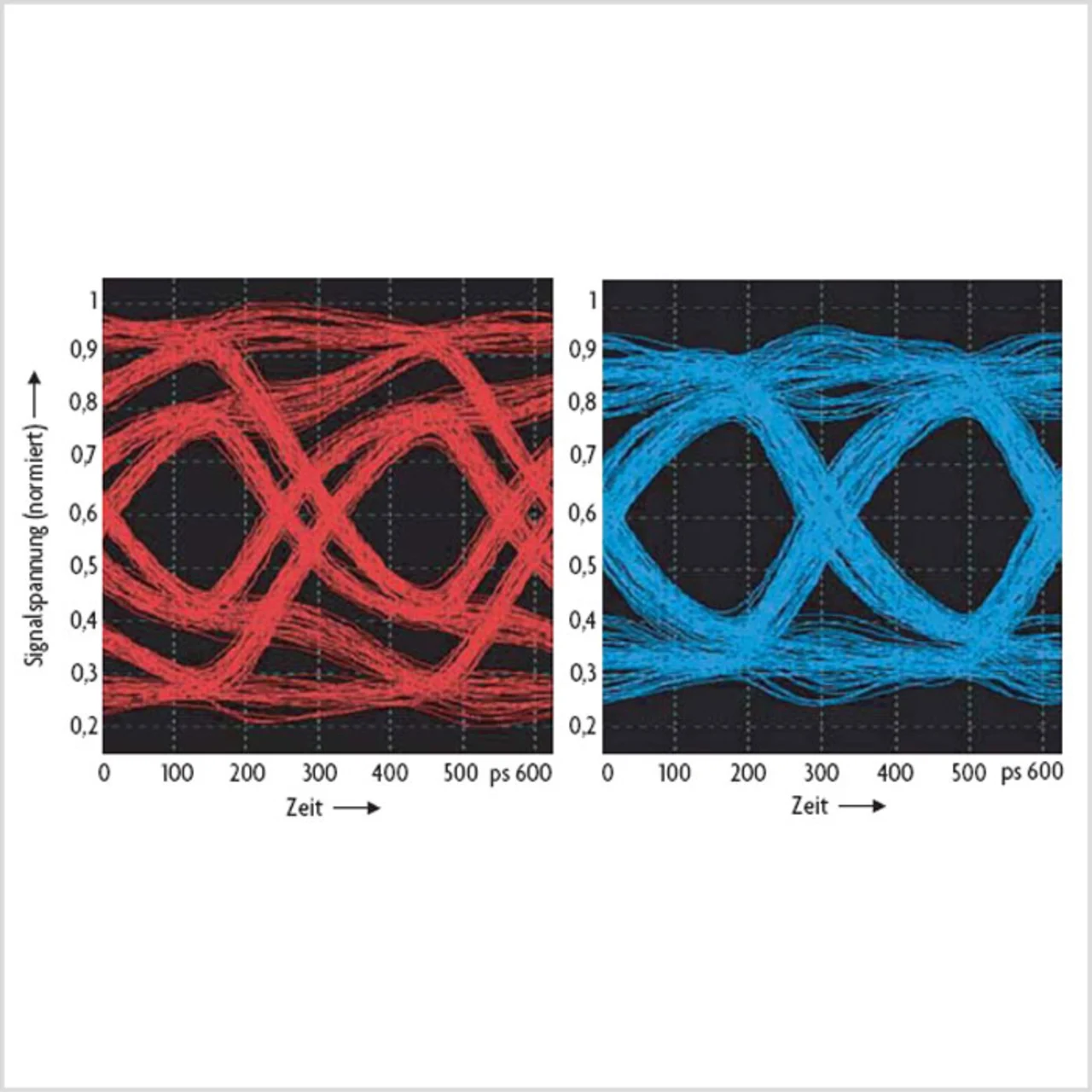

Bild 3 zeigt die Resultate einer Kanal-Simulation für eine herkömmliche Multi-Drop- (links) bzw. eine DPP-Topologie (rechts). Dabei gibt jedes Augendiagramm die Worst-Case-Konfiguration für eine Systemtopologie mit Unterstützung für zwei Module wieder. Bei einer Multi-Drop-Technologie ist die schlechteste Signalintegrität zu beobachten, wenn beide Modulsteckplätze besetzt sind. Anders bei einer DPP-Konfiguration: Hier stellt sich die ungünstigste Signalintegrität dann ein, wenn nur ein Modul gesteckt ist und die Signale das Durchgangs-Modul mit seinen zusätzlichen Steckverbindern passieren müssen. Sind in einer DPP-Konfiguration beide Module gesteckt, verbessert sich dagegen die Signalübertragung gegenüber dem gezeigten Fall, da der elektrische Pfad kurzgeschlossen wird und kein zusätzlicher Steckverbinder passiert werden muss. Wie Bild 3 deutlich macht, ist das Augendiagramm bei der Multi-Drop-Topologie so eng, dass in Sachen Spannung und Timing unzureichende Reserven vorhanden sind, um Daten erfolgreich mit 3,2 Gbit/s zu übertragen – selbst wenn der Speicherkanal für die Reduzierung des Übersprechens, der Störungen durch gleichzeitige Schaltvorgänge und der Impedanz-Fehlanpassungen optimiert ist. Der Wechsel von der Multi-Drop- zur DPP-Topologie bringt dagegen eine deutliche Vergrößerung der Spannungs- und der Timing-Reserven mit sich. Mit DPP lässt sich eine Konfiguration mit zwei Modulen mit einer Datenrate von 3,2 Gbit/s betreiben.

Sub-Page-Aktivierung

In den meisten DRAM-Designs ist die Page-Größe des einzelnen DRAM festgelegt, meist auf 1 bis 2 Kbyte. Beim Hinzufügen von Modulen zu einem DPP-System nimmt die Zahl der DRAM-Bausteine zu. Die Page-Größe des Systems steigt beim Hinzufügen von Modulen an, so dass jeder Aktivierungsbefehl eine größere Leistungsaufnahme verursacht. Vermeiden lässt sich dieser zusätzliche Leistungsbedarf mithilfe der Sub-Page-Aktivierung, bei der nur die Hälfte der Page aktiviert wird, wenn das DRAM für die halbe Breite konfiguriert wird. Analog dazu wird im „Quarter-Width-Modus“ nur ein Viertel der Page aktiviert. Eines oder zwei Zeilen-Adressbits werden zur Befehlsstruktur hinzugefügt, um die zu aktivierende Sub-Page auszuwählen. Dementsprechend werden eines oder zwei Spalten-Adressbits benötigt, um bei Spaltenzugriffen den jeweils benötigten Teil der Daten zu adressieren. Auf diese Weise gelingt es, die Page-Größe und die Spalten-Granularität des Gesamtsystems unabhängig davon zu erhalten, wie viele Module das System enthält.

DPP-Topologien bilden eine Ergänzung zum Modul-Threading, das in Teil 2 dieses Artikels genauer erläutert wird. Beim Hinzufügen von Modulen zu einem Speichersystem ist es sinnvoll, jedes Modul als einen oder mehrere Threads zu behandeln. Durch die Einrichtung von Speicher-Threads innerhalb der Grenzen eines Moduls kann jedes Modul eine andere Kapazität, eine andere Organisationsweise oder einen anderen Datendurchsatz haben, ohne dass dies Rückwirkungen auf die Funktionsweise anderer Module hat.

- Speed-Limit (fast) unendlich – Teil 1

- Neue Bus-Techologien für hohe Datenraten

- Das DDP-Konzept