Arbeitsspeicher der Zukunft

Speed-Limit (fast) unendlich – Teil 1

Fortsetzung des Artikels von Teil 2

Das DDP-Konzept

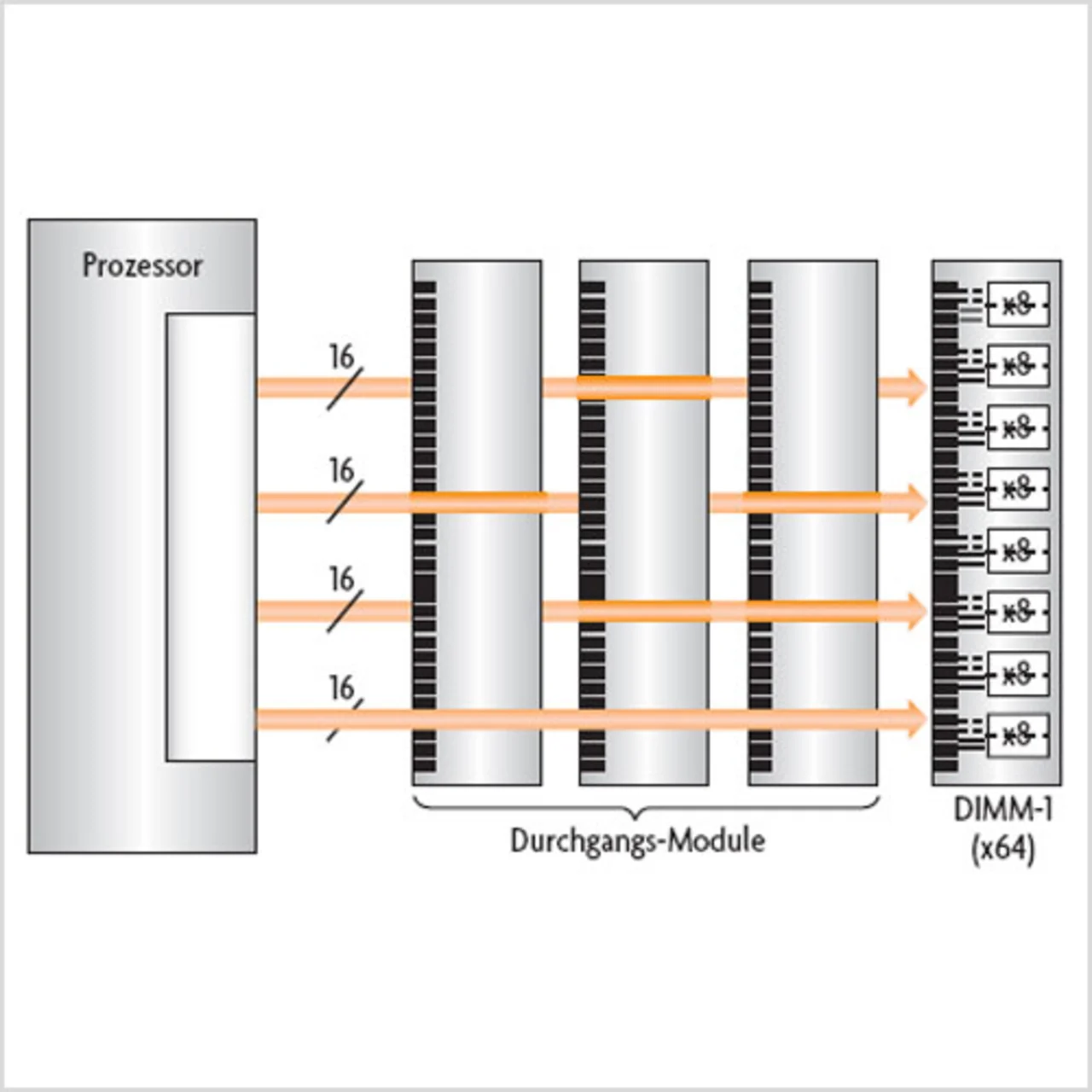

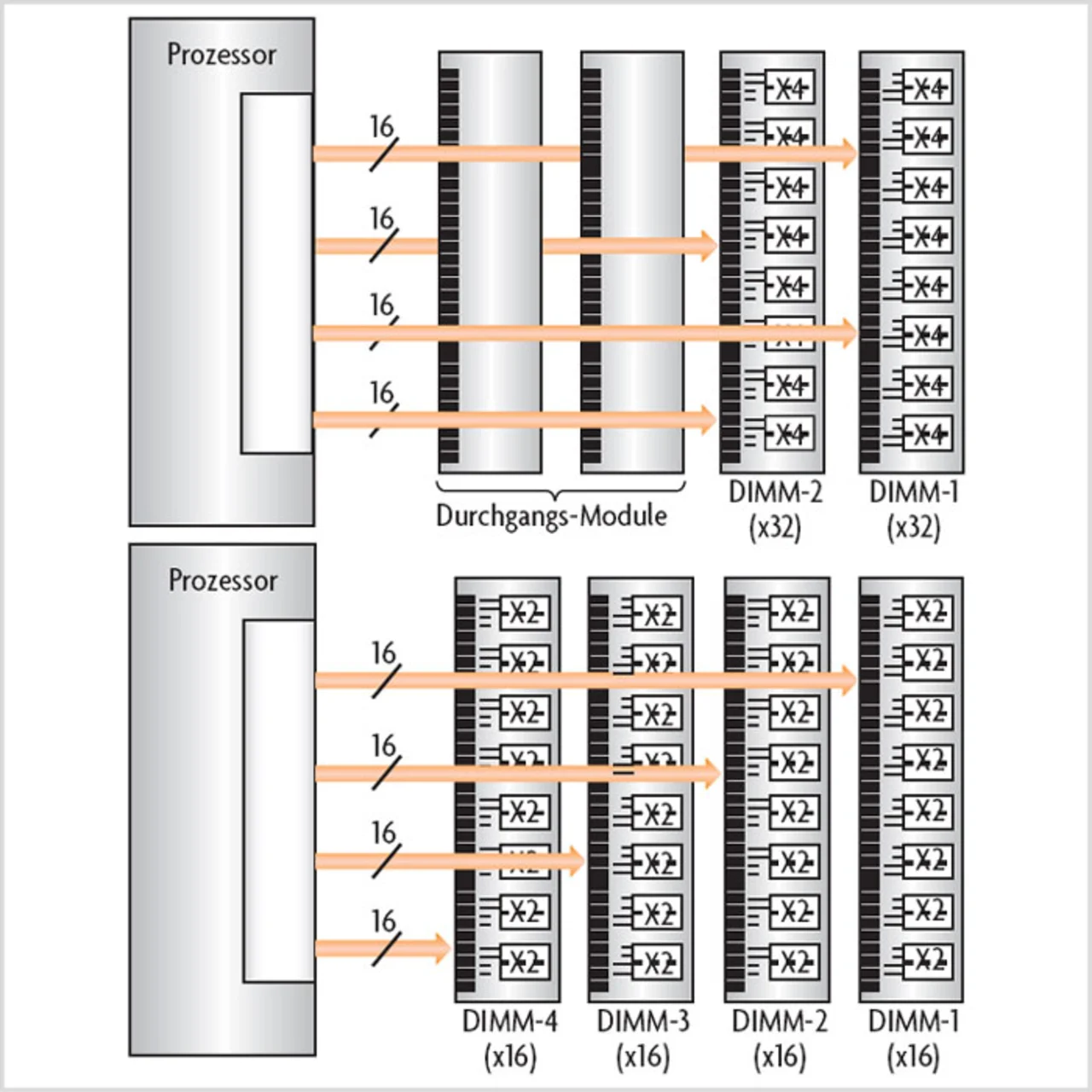

Das DPP-Konzept lässt sich mit den anhand zweier Module dargelegten Prinzipien auf eine Topologie mit vier Modulen ausdehnen. Bild 4 verdeutlicht die grundlegende Routing-Topologie und zeigt, welche Verschaltung hierfür erforderlich ist. Ebenso wie im Fall des Zwei-Modul-Szenarios ist die Gesamtzahl der an jedes Modul geführten Signalleiterbahnen proportional zur Anzahl der Speichermodul-Steckplätze. Im vorliegenden Fall werden zu jedem der vier Steckplätze direkt 16 bit geleitet. Während die Dual-Konfiguration zwei unabhängig voneinander funktionsfähige Gruppen von Signal-Leiterbahnen benötigt, sind bei der Vier-Modul-Konfiguration vier Gruppen erforderlich. Ist in dieser Topologie nur ein DRAM-Modul gesteckt, müssen zwei Gruppen von Datenbits ein Durchgangs-Modul überqueren, während eine Gruppe zwei Duchgangs-Module zu passieren hat. Ein Design mit nur einem Duchgangs-Modul erfüllt übrigens die Anforderungen dieser Topologie unabhängig davon, in welchen Steckplatz das Modul eingesetzt wird. Bild 5 zeigt links die Vier-Modul-Topologie mit zwei installierten DRAM-Modulen. Die DRAMs aus Bild 4 wurden in diesem Fall auf die Hälfte der ursprünglichen Breite (×4 anstatt ×8) konfiguriert. Dieses Szenario hat übrigens große Ähnlichkeit mit der Verwendung zweier Zwei-Modul-DPP-Topologien an ein und derselben 64-bit-Speicherschnittstelle.

Jobangebote+ passend zum Thema

Bild 5 zeigt rechts erneut das Vier-Modul-System, jedoch sind diesmal alle vier Speichermodule gesteckt. Hierbei wird jedes Modul vom Speicher-Controller so konfiguriert, dass es gegenüber einem unkonfigurierten Speichermodul nur ein Viertel der vorhandenen DQ-Datenleitungen nutzt. Jedes Modul stellt damit (vertikal aufgeteilt) ein Viertel der gesamten Speicherkapazität zur Verfügung.

Mit zunehmender Datenrate kommen die Signalintegritäts-Probleme auch für den C/A-Kanal (Command/ Address) modulbasierter Speichersysteme zum Tragen. Während die Daten-Signalisierung an ein einzelnes Modul akzeptabel sein kann, scheidet die Verwendung eines gemeinsamen C/A-Busses zur Steuerung mehrerer Module möglicherweise aus. Zu den traditionellen Lösungen für dieses Problem gehört es, registerbestückte Module zur Vereinfachung des Kanals und zur Minderung der Lastkapazität zu verwenden oder an jedes Modul einen eigenen C/A-Bus zu führen.

Die Verwendung von Registern bringt Mehrkosten und vermehrte Latenzen für das Speicher-Subsystem mit sich, während in Systemen mit eigenen C/A-Bussen Pins und Bandbreite ungenutzt bleiben, solange nicht alle Modulsteckplätze besetzt sind.

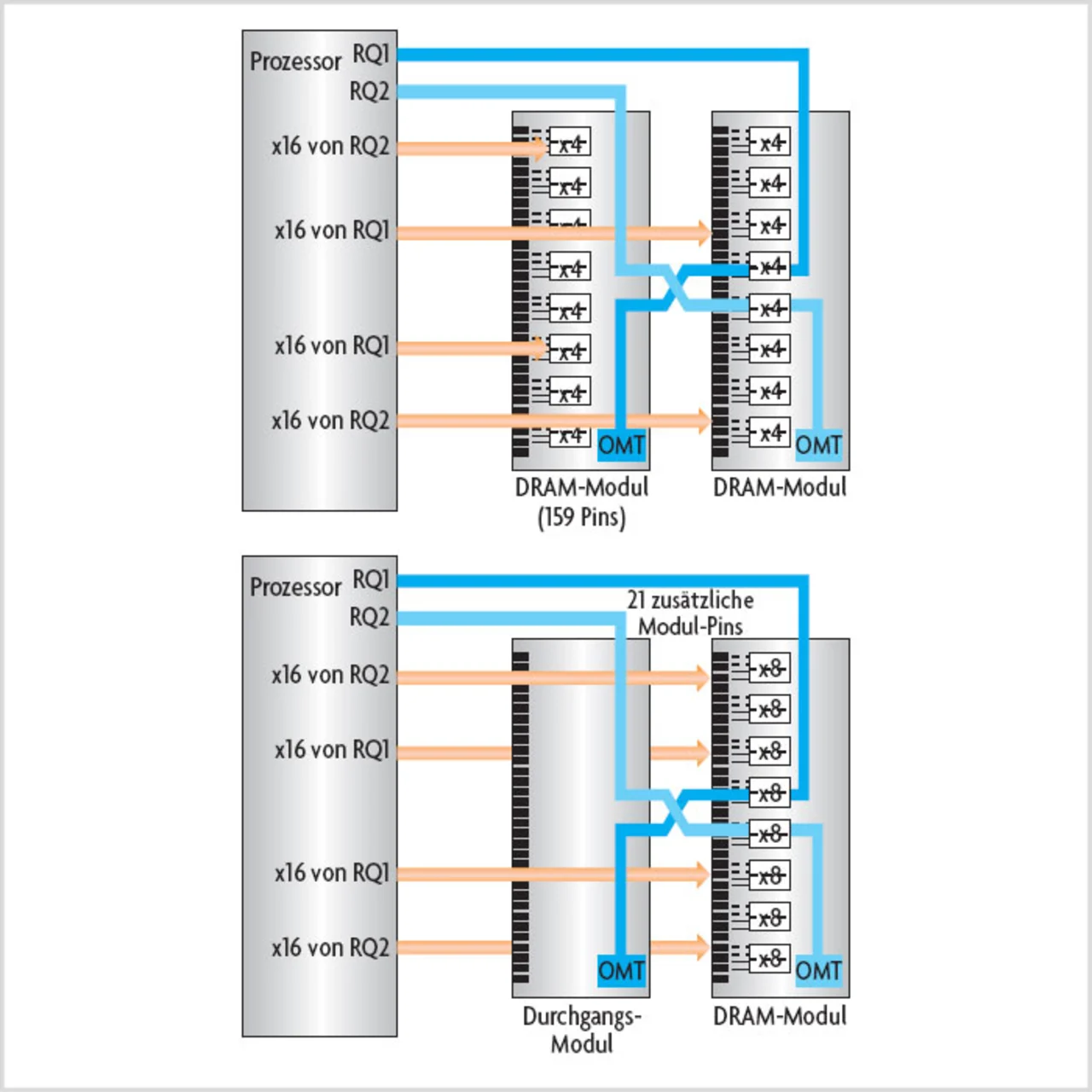

Zur Lösung der Probleme kann das Dynamic-Point-to-Point-Konzept auch auf den C/A-Bus angewandt werden. In Bild 6 ist oben das DPP-/C/A-Konzept exemplarisch für ein Zwei-Modul-System dargestellt. Dabei sind zwei C/A-Busse so geroutet, dass jeder genau die Hälfte jedes Moduls im System adressiert. Die Worst-Case-Belastung eines jeden C/A-Kanals ist damit genau so groß wie für ein komplettes Modul, allerdings müssen zwei Steckverbinder passiert werden, um das modulübergreifende Routing zu unterstützen. Wie der Fall mit einem einzigen Modul in Bild 6 unten deutlich macht, werden beide C/A-Kanäle auch dann genutzt, wenn nur ein Modul gesteckt ist, denn jeder Kanal adressiert nur einen Teil des vorhandenen Moduls.

Ein Durchgangs-Modul stellt für C/A 2 die Verbindung vom ersten zum zweiten Modulsteckplatz her und dient als Abschluss für die Signale von C/A 1.

Das Near-Ground-Signaling

Soll die Gesamt-Leistungsaufnahme des Speichersystems reduziert werden, müssen drei wichtige Komplexe verbessert werden: der Leistungsbedarf für die Taktung des Systems, für die I/O-Signalisierung und für die DRAM-Kernzugriffe. Das Near-Ground-Signaling (Signalisierungsverfahren mit extrem geringen Spannungspegeln) erlaubt hohe Datenraten mit deutlich weniger Energiebedarf für die I/O-Signalisierung, erheblich reduzierte Designkomplexität sowie die Wahrung einer guten Signalintegrität.

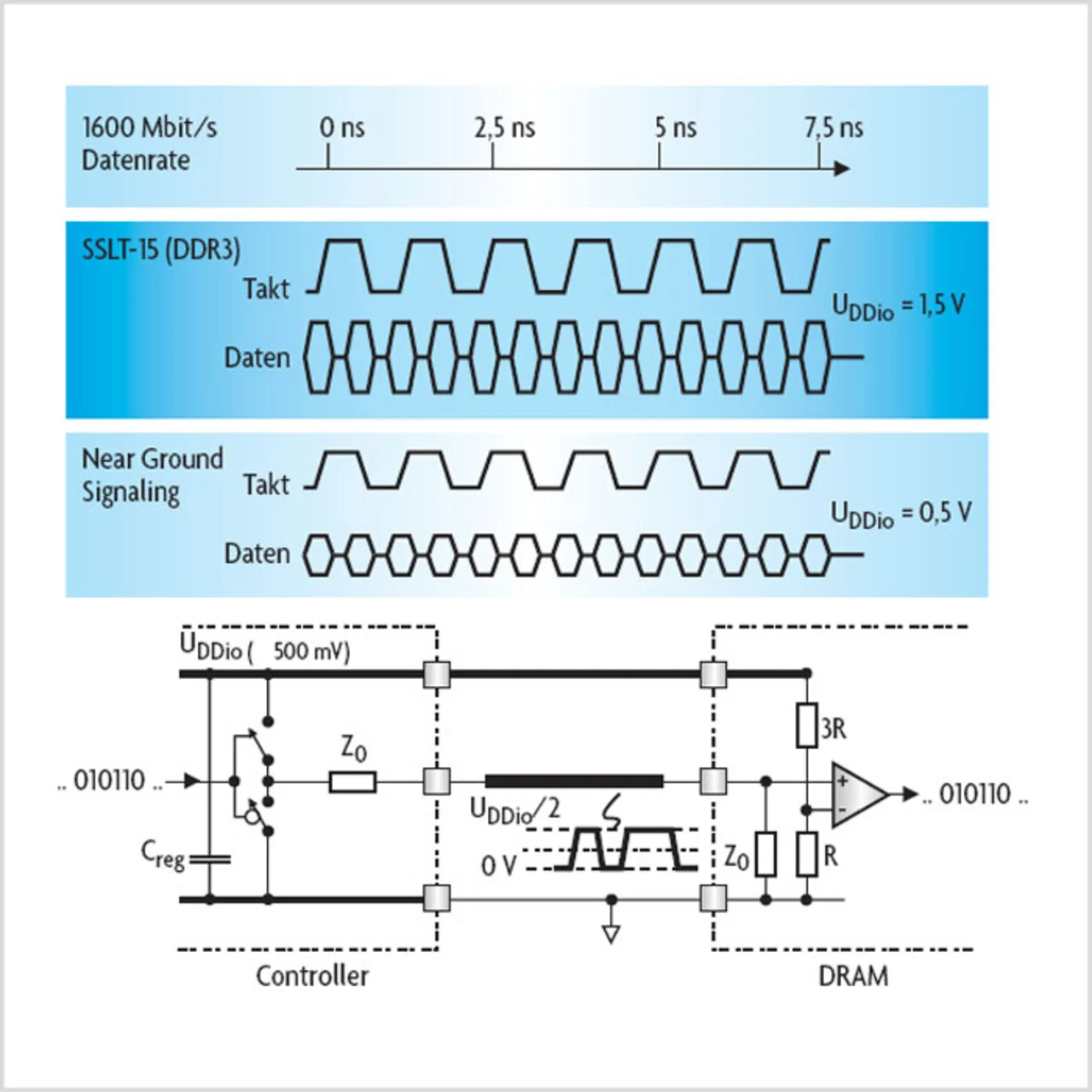

Während ein DRAM-Prozess möglicherweise 1,2 V oder gar 1,5 V für die zuverlässige Einhaltung einer angestrebten Datenrate von 3,2 Gbit/s benötigt, kann ein ASIC-Prozess diese Datenrate bequem mit 1,0 V oder sogar weniger erreichen. In den meisten Fällen ist es weniger energieeffizient, einen 1,0-V-ASIC-Prozess (z.B. mit 45 nm oder darunter) an eine 1,5-V-basierte Signalschnittstelle anzuschließen als an eine Schnittstelle auf Basis von 1,0-V-Signalen. In diesem Fall müssten Transistoren mit großer Oxidschichtdicke oder Stacked-Transistor-Ausgangsstufen verwendet werden, die beide weniger energieeffizient sind als die verfügbaren Bausteine mit dünnen Oxidschichten. Vermeiden lässt sich dieser Spannungsunterschied und die daraus resultierende Energie-Ineffizienz durch das Near-Ground-Signaling, das in Bild 7 illustriert ist.

Mit dem Near-Ground-Signaling kann die I/O-Spannung (UDDio) des Speicher-Controllers deutlich niedriger als die Maximalspannung von Schaltungselementen mit dünner Oxidschicht angesetzt werden (typisch 0,9 bis 1,0 V bei Prozesstechnologien mit 45 nm oder weniger). Das DRAM am anderen Ende des Kanals kann dagegen weiterhin die von seinen internen Schaltungen benötigte höhere Spannung (z.B. 1,2 V bis 1,35 V) verwenden, um eine zuverlässige Signalisierung mit 3,2 Gbit/s zu erreichen.

Ähnlich wie bei Pseudo-Open-Drain-Logik (PODL) erfolgt der Abschluss auch beim Near-Ground-Signaling an eine der Stromversorgungen. Anders als bei PODL wird hier jedoch die Terminierung an die GND-Leitung (0 V) vorgenommen. Da diese Leitung in einem Speicherkanal in der Regel die niedrigste Impedanz aufweist, kann dieses Terminierungskonzept auch zur Reduzierung der SSO-Störungen („Ground Bounce“) beitragen.

Das Near-Ground-Signaling bedient sich gegenüber der traditionellen SSTL- oder PODL-Technik eines geringeren Spannungshubs, was die I/O-bedingte Stromaufnahme auf beiden Seiten der Verbindung gegenüber DDR3 entscheidend senkt. Abgesehen vom niedrigeren Energiebedarf für die Signalisierung selbst, können auch kleinere I/O-Treiberschaltungen verwendet werden, was eine noch geringere Stromaufnahme in den Vortreiber- und Taktverteilungs-Schaltungen ergibt. Simulationsergebnisse deuten auf eine Ersparnis von etwa 1,25 mW (20 %) je I/O hin, sodass sich die Einsparungen entsprechend aufsummieren, wenn der Controller drei oder gar vier 64-bit-Speicherschnittstellen hat.

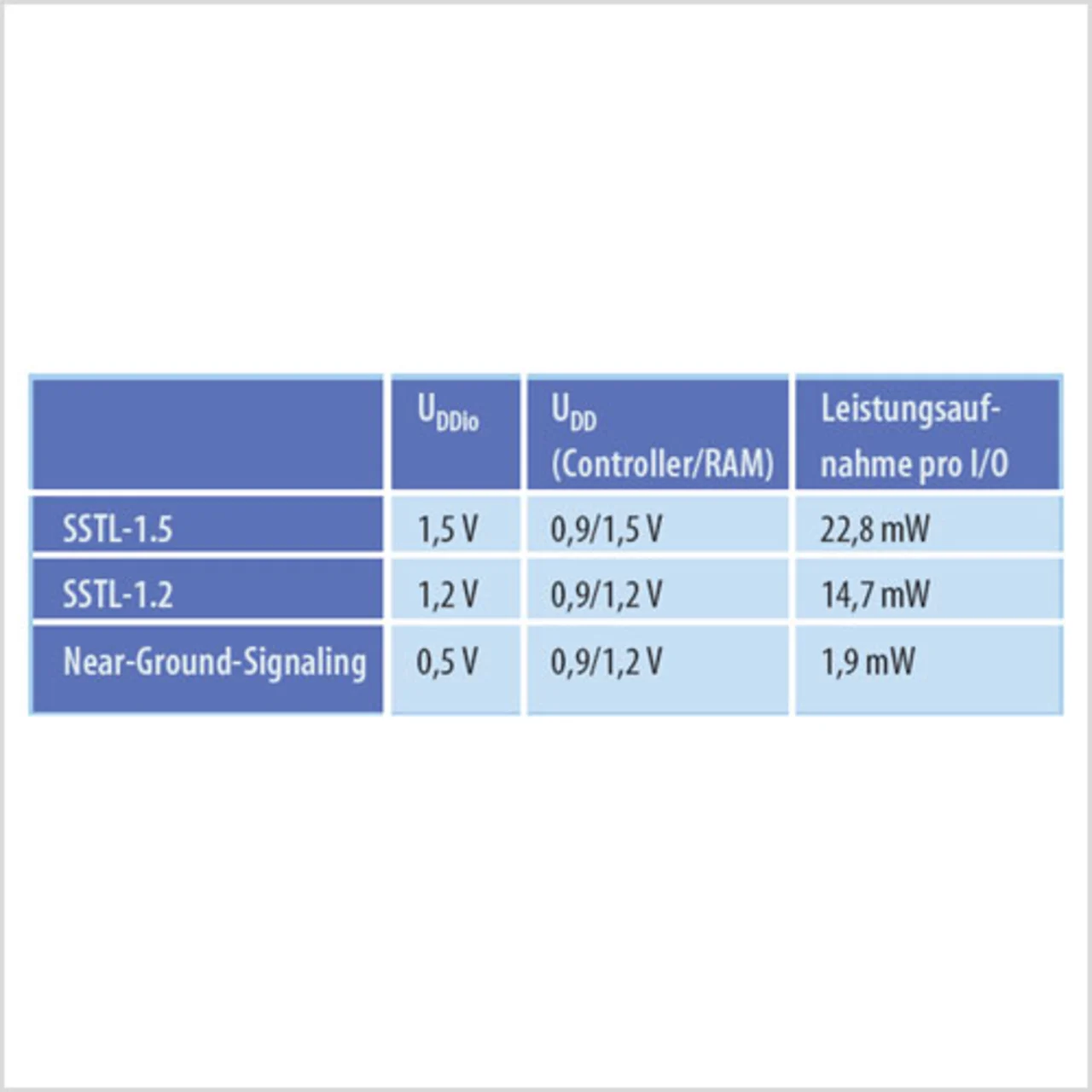

Vom Kostenstandpunkt aus betrachtet, macht das Near-Ground-Signaling auch die Verwendung von Transistoren mit dicken Oxidschichten im Speicher-Controller entbehrlich, was mindestens zwei zusätzliche Masken und zwei weitere Halbleiterverarbeitungs-Schritte einspart. Um für die Übergangsphase die optionale Abwärtskompatibilität zu DDR3 zu sichern, lässt sich ohne großen Aufwand eine bimodale I/OSchaltung für den Anschluss an Low-Voltage-DDR3-Schaltungen implementieren. Die Tabelle zeigt zusammengefasst die Ergebnisse der Leistungs-Simulation für einen Speicher-Controller und DRAM in 40- bzw. 65-nm-Technologie.

Nachteilig am Near-Ground-Signaling ist, dass im Empfangsteil des DRAM Pegelumsetzer-Schaltungen benötigt werden. In dieser Hinsicht ist es vorteilhaft, dass schnelle Pegelumsetzer auf Basis von NFETs in Gate-Schaltung mit einer Leistungsaufnahme von etwa 1 mW pro I/O-Leitung hergestellt werden können, die sich deaktivieren lassen, sobald keine aktiven Daten-Transaktionen mehr stattfinden.

B.S.E.E. Scott Best studierte Elektrotechnik an der Cornell University, Ithaca, N.Y. Er arbeitet als Senior Principal Engineer bei Rambus und hält mehr als 20 Patente in den Bereichen Schaltkreis-Design und Systemtechnik.

scott_best@rambus.com

M.Sc. Michael Ching studierte Elektrotechnik an der University of California in Berkeley. Er begann seine Karriere bei Intel, wo er Hochgeschwindigkeits-I/Os für Mikroprozessoren entwickelte. 1996 kam er zu Rambus, wo er diverse Positionen in den Bereichen Entwicklung und Marketing besetzte. Heute arbeitet er als Direktor für strategische Entwicklungen.

Michael_Ching@rambus.com