Angriff auf Intel geht in 2. Runde

Plus 50 % IPC und SVE: Arms neue CPUs für Infrastruktur-Markt

Nach dem spektakulären Eintritt ins Sever-Geschäft mit der Neoverse-N1-CPU stellte Arm nun die Nachfolgemodelle vor: Neben der N2-CPU gibt es analog zu den Cortex-A/X1-Derivaten eine neue High-Performance-CPU Neoverse-V1 – als echte Alternative zu Intels und AMDs besten Produkten.

Der Markt der Infrastruktur-CPUs wird immer noch von den x86-Herstellern Intel und (dank des Erfolges seiner Epyc-CPUs mit wachsendem Marktanteil) AMD dominiert wird.

Die Neoverse-N1-CPU haben wir Ihnen ausführlichst vorgestellt, den angestrebten Zuwachs an Rechenleistung gegenüber ihrer Basis Cortex-A76 in Höhe von 30 % hat sie um das Zweifache übertroffen.

Heute stellte Arm nicht nur seine Neoverse-N-Roadmap in Form der Neoverse-N2-CPU (Codename Perseus), sondern auf Basis einer CPU-Mikroarchitektur (Codename Zeus) auch eine ganz neue Produktkategorie vor, die über die Neoverse N-Serie hinausgeht: Die Einführung der neuen Neoverse V-Familie und der Neoverse-V1-CPU.

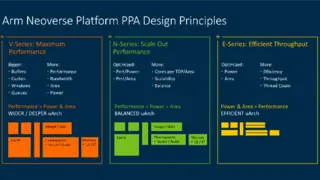

Anfang 2020 haben wir die neue Cortex-X1-CPU-IP von Arm präsentiert, die eine bedeutende Änderung des Geschäftsmodells von Arm darstellte: Anstatt nur eine einzige One-fits-all-CPU-Mikroarchitektur anzubieten, mit der die Lizenznehmer in einer breiteren Palette von Designs und Leistungspunkten auskommen mussten, führte Arm eine zweite Familie ein, wobei sich eine mit dem Cortex-X1 nun auf reine Höchst-Rechenleistung unabhängig von der Silizium-Fläche und der Leistungsaufnahme konzentriert, während das andere Design – der Cortex-A78 - sich auf die traditionellere PPA-Designphilosophie (Power, Performance, Area) von Arm konzentriert.

Die Zeus-Mikroarchitektur in Form der Neoverse-V1-CPU ist im Wesentlichen also das infrastrukturelle Gegenstück zu dem, was Arm mit der Cortex-X1 CPU im traditionellen IP-Angebot erreicht hat: Konzentration auf maximale Rechenleistung bei geringerer Berücksichtigung von Leistungsaufnahme und Siliziumfläche. Dies bedeutet, dass der V1 über wesentlich größere Caches und Kernstrukturen verfügt, die mehr Fläche und Leistung verbrauchen.

Im Ergebnis wurde gegenüber der Neoverse-N1-CPU eine nahezu unglaubliche IPC-Steigerung um 50 % erzielt, unglaublich deshalb, weil die Messung bei identischem Fertigungsprozess und identischer Taktfrequenz erfolgte. Bei den Produkten von Arms Lizenznhemern dürfen wir weitere Steigerungen erwarten, da diese vermutlich auf kleinen Prozessgeometrien gefertigt und höhere Taktfrequenzen erzielen werden.

Amazon Web Services implementierte den Neoverse-N1 in seinem Graviton2-SoC,das mit 2.5 GHz getaktet wird. Diese haben 64 CPU-Kerne, die Fertigung erfolgt in einem 7-nm-Prozess für mehr als 30 Milliarden Transistoren. Die C6g-, M6g- und R6g-Instanzen von AWS erreichen damit verglichen zu den bisherigen A1-Instanzen mit dem ersten Graviton-Prozessor eine bis zu siebenfache Geschwindigkeit.

Die Chips nutzen ein MB L2-Cache pro Core, zudem 32 MB L3-Puffer und sie weisen acht DDR4-3200-Speicherkanäle auf, zudem gibt es 64 PCIe-Gen4-Lanes für NVMe-SSDs oder XPUs. Die bisherigen Graviton1 sind 16-nm-Chips mit nur 16 Kernen basierend auf Cortex-A72. Pro Core weist Graviton2 die doppelte Gleitkomma-Leistung auf.

Wenn man nun annimmt, dass ein auf dem Neoverse-V1 basierendes SoC mit 3 Ghz getaktet würde, käme man auf eine Leistungssteigerung von 80% pro Thread. Die würde sogar ausreichen, um mit den derzeit besten Hochleistungs-Desktop-Chips von AMD und Intel mithalten zu können.

Neoverse-N2 ist Perseus

Neben der Plattform Neoverse-V1 hat Arm eine Roadmap für die N-Familie vorgestellt. Perseus wird zum Neoverse-N2 und wird im Vergleich zum N1 eine 40-prozentige Steigerung der IPC ermöglichen, behält jedoch weiterhin die gleiche Designphilosophie bei, nämlich die Maximierung der Rechenleistung bei geringstem Energieverbrauch und kleinster Siliziumfläche.

Arm sagt, dass sie dieses "Perseus"-Design bis Ende des Jahres in Lizenz vergeben werden und dass sich die Kunden bereits bei Beta-RTL engagieren - wir werden wahrscheinlich auf der nächstjährigen TechDay-Veranstaltung mehr über diese Produktgeneration hören.

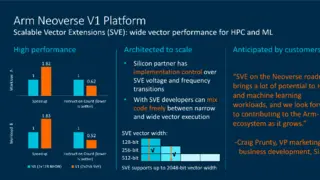

Endlich SVE

In meiner Analyse des Neoverse-N1 hatte ich u.a. das Fehlen von SVEs (Scalable Vector Extensions) kritisiert. Scalable Vector Extension oder kurz SVE ist der Name einer Spezifikation für SIMD-Einheiten innerhalb der Arm-Prozessorarchitektur. Die Spezifikation wurde als eine Erweiterung der 8. Generation ARMv8 dieser Prozessorarchitektur entwickelt und erlaubt es, SIMD-Befehle bis zu einer Breite von 2048 Bit in Schritten von 128 Bit zu definieren. SVE ist nicht kompatibel zu Neon (einer älteren SIMD-Einheit für Arm-Prozessoren), sondern definiert einen neuen Befehlssatz innerhalb des Arm64-Bit-Befehlssatzes.

Dabei definiert die Spezifikation nur den Befehlssatz und Register unabhängig von der tatsächlichen Implementierung. Die Breite der Ausführungseinheiten kann von 128 Bit bis 2048 Bit in 128 Bit-Schritten reichen, der Befehlssatz ist unabhängig von der physischen Implementierung, SVE-Code kann somit auf zukünftigen, weiterentwickelten SIMD-Einheiten (größerer Breite) ohne Codeänderungen oder Neukompilierung ausgeführt werden, d.h. der Code kann mit der unterschiedlichen Ausführungsbreite einer Mikroarchitektur skaliert werden, was mit den heutigen Neon- oder AVX-SIMD-Befehlen einfach nicht möglich ist.

SVE arbeitet wie Neon mit 32 Registern (unterschiedlicher Breite), benötigt aber zusätzlich Vector Control Register, welche die Vektor-Länge angeben, und Eigenschaftsregister. Endlich unterstützen jetzt sowohl der Neoverse-V1 als auch der N2 SVE, wobei der V1 zwei 256-Bit-Pipelines hat und der N2 ein 2x128-Bit-Design ist.

Fujitsus A64FX-Chip und die Custom-Core-Mikroarchitektur von Fujitsu waren bis dato die einzige CPU, die mit SVE verfügbar war, was bedeutet, dass die V1 und N2 die ersten eigenen Designs von Arm sein werden, die tatsächlich SVE implementieren.

Bedauerlicherweise wird zumindest Neoverse-V1 ein SVE nur der 1. Generation implementieren, möglicherweise wird die N2-CPU dann SVE der 2. Generation beinhalten. Der Hauptunterschied zwischen SVE2 und SVE liegt in der funktionalen Abdeckung des Befehlssatzes. SVE wurde für HPC- (High Performance Computing) und ML- (Machine Learning) Anwendungen entwickelt. SVE2 erweitert den SVE-Befehlssatz, um mehr Datenverarbeitungsbereiche (über HPC und ML hinaus) zu ermöglichen. Der SVE2-Befehlssatz kann auch die üblichen Algorithmen beschleunigen, die in Anwendungen wie Computer-Vision, LTE-Basisbandverarbeitung oder Web-Diensten zum Einsatz kommen.

Um Compilern eine bessere Vektorisierung für diese Bereiche zu ermöglichen, fügt SVE2 eine vektorbreiten-diagnostische Version der Neon-Instruktionen in den meisten Festkomma-DSP- (Digital Signal Processing) und Medienverarbeitungsfunktionen hinzu.

Bei zwei „typischen“, jedoch nicht weiter spezifizierten Workloads, hat Arm gegenüber einer Neoverse-N1-CPU mit 2x128-bit NEON-SMID-Pipelines beim Einsatz der V1 einen Geschwindigkeitszuwachs von 82 bzw. 83 % gemessen, während die Anzahl der Befehle um 38 bzw. 48 % gesunken ist.

Jobangebote+ passend zum Thema

Arms neue Neoverse-CPUs

Fazit

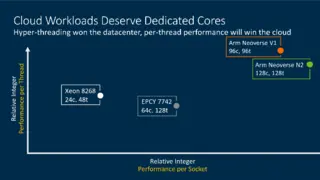

Während man bei der Neoverse-N2-CPU wohl Designs mit bis zu 192 Cores sehen wird, werden wir bei Neoverse V1 Designs mit weniger Cores sehen, da die CPUs einfach größer und leistungshungriger sind. Arm sieht die Bandbreite bei 64 bis 96 CPUs. Letztere sind die Spitzenprodukte, die sich gegen das Beste von Intel und AMD durchsetzen werden - und wenn sich die Leistungsprognosen bewahrheiten (wie es bei Arm üblich ist), dann steht uns ein brutaler Konkurrenzkampf bevor, wie wir ihn noch nie zuvor gesehen haben.

Das erste öffentlich bekannte Design, bei dem der Einsatz der neuen Neoverse V1-Kerne bestätigt wurde, ist der "Rhea"-Chip von SiPearl, der 72 Kerne in einem 7-nm-TSMC-Prozessknoten zu enthalten scheint.

Beim Neoverse-N2 nimmt Arm bei einem 8/16-Core-Design z.B. für Gateways und Router eine TDP von 20 bzw. 35 W an, in einer mittleren Konfiguration z.B. für SmartNICs mit 12/36 Cores werden 30 bzw. 80 W erwartet und am oberen Ende im Rechenzentrum 32 bis 192 Cores mit 80 bzw. 350 W TDP.

Interessant sind Vergleichsdaten mit Produkten von Intel und AMD, die Arm namentlich nicht nennen wollte, die wir jedoch trotzdem eindeutig identifizieren konnten. Bild 3 in der Bilderstrecke zeigt den Vergleich der Integer-Rechenleistung pro Thread sowie Integer-rechenleistung pro Sockel von einer 96-Core-Neoverse-V1 und 128-Core-Neoverse-N2-Konfiguration im Vergleich zu einem 24-Core-Intel-Xeon 8268 und einem 64-Core-AMD-Epyc 7742, bei beiden SKUs sind jeweils SMT und Turbo-Modus eingeschaltet.

Die heutige Ankündigung ließ viele technische Details offen, wobei Arm plant, zu einem späteren Zeitpunkt näher auf die Mikroarchitekturen der Designs einzugehen. Der DevSummit von Arm ist für den 6. bis 8. Oktober geplant - vielleicht erfahren wir dort auch etwas mehr.