ARM TechCon 2014

Freescale enthüllt Details über Hybrid-i.MX 6

Fortsetzung des Artikels von Teil 2

Geteilter Speicher und Low-Power-Domäne für Cortex-M4

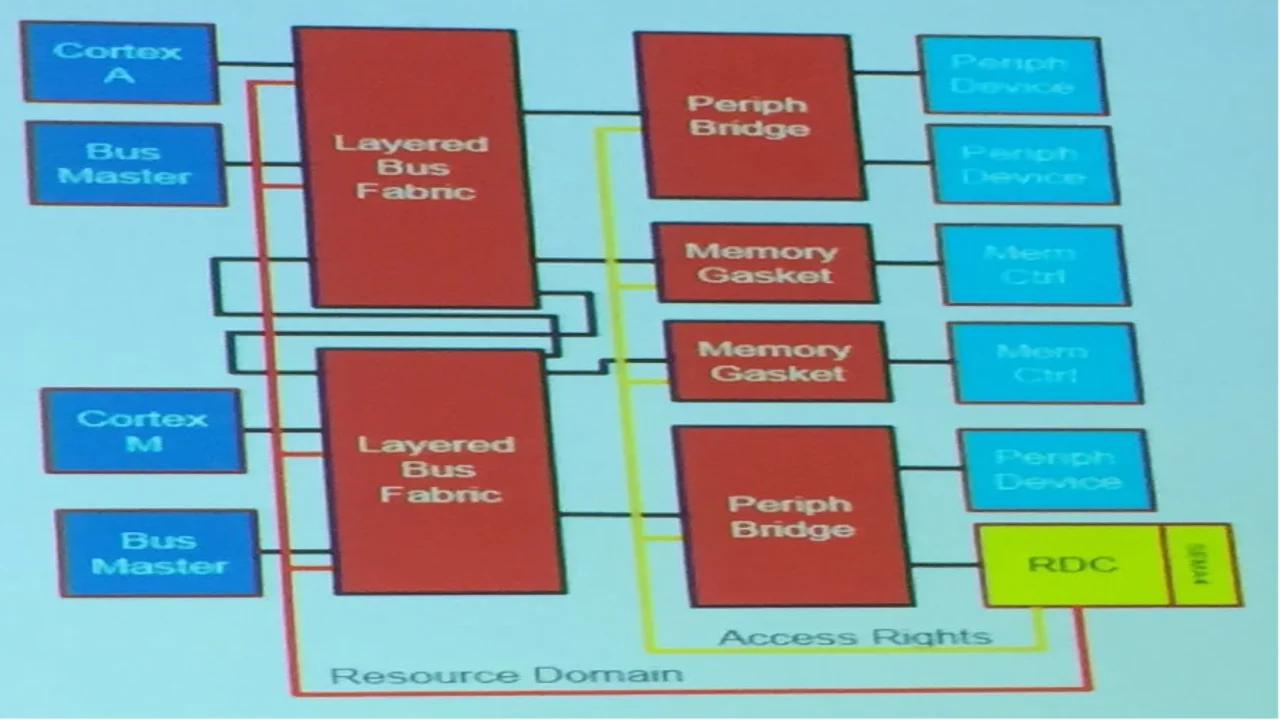

Die zwischen den CPUs geteilte Bus-Topologie ermöglicht auch die Nutzung von geteiltem Speicher. Die RDC-Hardware kann den Speicher dazu partitionieren und den Zugriff je nach Domäne beschränken. Ergänzend kann die zentrale Sicherheitseinheit (CSU) dazu genutzt werden, den Zugriff von Mastern und Slaves auf Speicheregionen zu beschränken.

Last but not least stellen sowohl die für den Cortex-A9 relevante Architektur ARMv7-A als auch die für den Cortex-M4 relevante Architektur ARMv6-7 Instruktionen für einen exklusiven Speicherzugriff bereits – diese heißen LDREX und STREX. Wichtig ist dabei zu beachten, dass der durch exklusive Zugriffe referenzierte Speicher so kunfiguriert werden muss, dass die Kohärenz zwischen den unterschiedlichen CPUs gesichert ist.

Neue Wege ist Freescale auch bei der Partitionierung des Chips in drei Power-Domänen gegangen. Es gibt für den Cortex-A9 und energiehungrige Peripherie jeweils eine sogenannte High-Power-Domäne, während der Cortex-M4 und weniger energiehungrige Peripherie sich eine Low-Power-Domäne teilen. Power-Domänen, die aktuell nicht genutzt werden, können mittels Software-Steuerung abgeschaltete werden (Power-Gating), um Leckströme zu verhindern.

In der Low-Power-Domäne gibt es vier verschiedene Energiesparmodi, die gemeinsam haben, dass der Cortex-A9 mittels Power-Gating abgeschaltet wird: System-Idle (Cortex-M4 läuft mit 200 oder 24 MHz), Low-Power-Idle (Cortex-M4 läuft mit 200, 24 oder 4 MHz), und Suspend sowie Standby, in den letzten beiden Fällen wird auch die Cortex-M4-CPU abgeschaltet – die Unterschiede liegen in der noch aktiven Peripherie wie Echtzeituhr und dem Datenerhalt in den Registern.

In Summe erscheint der Ansatz mit dem RDC das Leben im Vergleich zum Vybrid deutlich zu vereinfachen, zudem liefert der Cortex-A9 bei 1 GHz eine deutlich höhere Rechenleistung als der im Vybrid mit 500 MHz getaktete Cortex-A5 (2.500 gegenüber 785 DMIPS), der Cortex-M4 ist dank 40-nm-Fertigung mit 200 MHz mindestens 20 % schneller. Eine GPU für 2D/3D-Grafik und zwei Gbit-Ethernet-Ports zeigen spätestens, dass der i.MX 6 deutlich oberhalb des Vybrid 6xx platziert ist und in Automotive-, Konsumelektronik- und Industrieanwendungen zum Einsatz kommen wird, wo neben hoher Rechenleistung auch eine grafisch anspruchsvolle Benutzerschnittstelle gefragt ist.

Jobangebote+ passend zum Thema

- Freescale enthüllt Details über Hybrid-i.MX 6

- Naxchrichtenaustausch zwischen Cortex-A9 und Cortex-M4, Semaphore

- Geteilter Speicher und Low-Power-Domäne für Cortex-M4