ARM TechCon 2014

Freescale enthüllt Details über Hybrid-i.MX 6

Fortsetzung des Artikels von Teil 1

Naxchrichtenaustausch zwischen Cortex-A9 und Cortex-M4, Semaphore

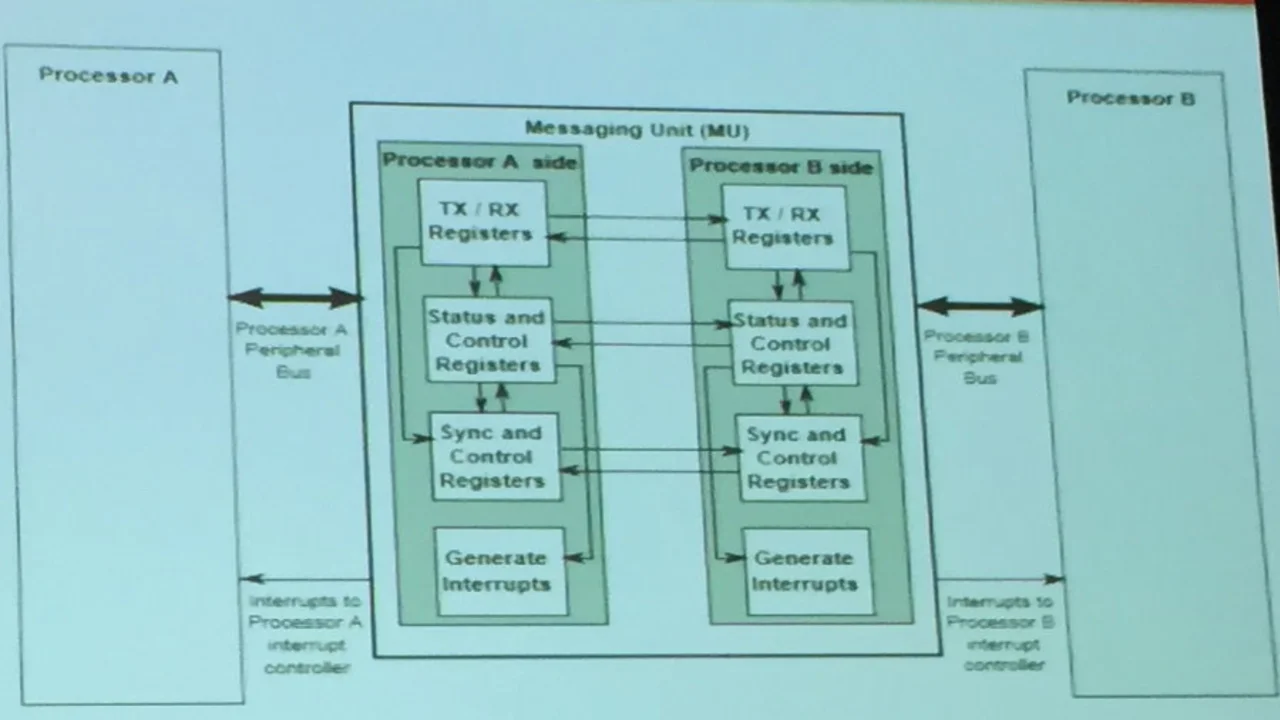

Eine sogenannte Nachrichten-Einheit (MU) enthält Register für das Senden und Empfangen von Nachrichten, die sich Cortex-A9 und M4 wechselseitig schicken können (Bild 2). Die IP dafür hat Freescale von seinen Basisband-Chips übernommen, die Steuerung erfolgt per Interrupt oder Polling. Auf jeder Seite gibt es 4 Sende-/Empfangsregister, dazu 12 Interrupt-Anforderungen (4 zeigen ein volles Empfangsregister an, 4 ein leeres Senderegister und 4 sind frei verwendbar). Dazu können pro Seite noch drei Flags für weitere Zwecke gesetzt werden.

Das SEMA4 genannte Semaphore-Modul ermöglicht einen sicheren Zugriff auf geteilte Ressourcen, es wurde von Vybrid bzw. Automotive-MCUs geerbt. Es gibt 16 Hardware-Semaphore, die nur von dem verriegelnden Prozessor entriegelt werden können. Falls eine Verriegelungs-Anforderung scheitert, kann zudem ein Interrupt ausgelöst werden, sobald das Semaphore entriegelt wurde. Nichts desto trotz sind entsprechende Software-Vorkehrungen notwendig, um sicherzustellen, dass nur CPUs mit verriegeltem Semaphore auf geteilte Ressourcen zugreifen.

Jobangebote+ passend zum Thema

- Freescale enthüllt Details über Hybrid-i.MX 6

- Naxchrichtenaustausch zwischen Cortex-A9 und Cortex-M4, Semaphore

- Geteilter Speicher und Low-Power-Domäne für Cortex-M4