ARM TechCon 2014

Freescale enthüllt Details über Hybrid-i.MX 6

Auf seiner eigenen Entwicklerkonferenz FTF hatte Freescale einen neuen i.MX-Prozessor mit Cortex-A9 und Cortex-M4 angekündigt, der heterogenes Multiprozessing (HMP) ermöglichen soll. Auf der TechCon folgten jetzt wesentliche technische Details.

Die Idee, unterschiedliche CPUs auf einem Chip zu kombinieren, ist nicht neu, beim i.MX 6 soll ein High-Level-Betriebssystem wie z.B. Linux oder Android auf dem mit 1 GHz getakteten Cortex-A9 laufen, während der mit 200 MHz getaktete Mikrocontroller-Core Cortex-M4 für echtzeitkritische Tasks auf einem RTOS wie MQX laufen sollen. Der Chip wird wie auch andere i.MX-Prozessoren in 40 nm gefertigt werden.

Die zahlreichen Vorteile beim hetrogenen Multprozessing (HMP) wie die flexible Verteilung von On-Chip-Ressorcen je nach Anwendungsfall werden mit der Herausforderung erkauft, dass die geteilten Ressourcen einen effektiven Mechanismus für die Isolation bzw. den Schutz vor dem jeweils anderen CPU-Cluster benötigen, damit es nicht zu Zugriffskonflikten kommt.

Die Zugriffe auf geteilten Speicher und Peripherie muß synchronisiert werden, die Software-Entwicklung ist komplizierter als bei SMP-Ansätzen, da Cortex-A9 und Cortex-M4 unterschiedliche Entwicklungssysteme aufweisen. Um „kooperative Software“ zu entwickeln, ist daher Hardware-Support unerläßlich. Dazu muss auch eine effektive Kommunikation zwischen den beiden Prozessoren ermöglicht werden.

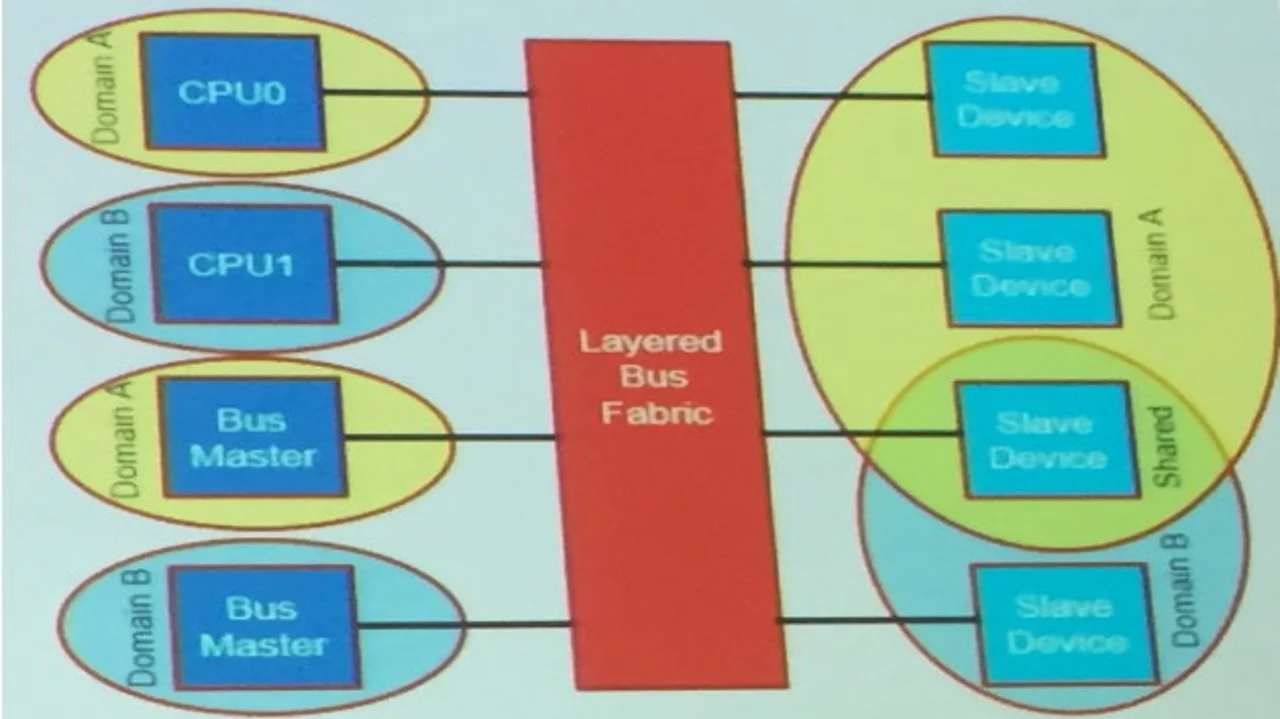

Freescale hat einen Ansatz gewählt, bei dem sogenannte Ressourcen-Domänen vergeben werden (Bild 1). Die Bus-Master werden dabei jeweils einer Ressourcen-Domäne zugewiesen, die Zugriffsrechte der Slaves ebenso wie die Zugriffsrechte auf Speicherregionen werden pro Domäne individuell definiert.

Zentrales Element in der Steuerung ist ein neues Ressourcen-Domänen-Controller (RDC) genanntes Element, der ein zentrales Programmiermodell für die Konfiguration von geteilten Systemressourcen und deren Isolation gegeneinander bereitstellt. Dazu gehören:

- Die Zuweisung von Master-Ressourcen (CPU und Bus-Master-Peripherie) zu einer Ressourcen-Domäne.

- Konfiguration von Lese-/Schreibrechten für Slave-Peripherie basierend auf einer Ressourcen-Domäne.

- Partitionierung des Speichers in Regionen, die pro Domäne separate Zugriffssteuerungen haben können.

- Konfiguration von Lese-/Schreibrechten für Speicheregionen basierend auf einer Ressourcen-Domäne.

- Integrierte Semaphore-Hardware zum sicheren Zugriff auf von mehreren Domänen geteilte Peripherie.

Jobangebote+ passend zum Thema

- Freescale enthüllt Details über Hybrid-i.MX 6

- Naxchrichtenaustausch zwischen Cortex-A9 und Cortex-M4, Semaphore

- Geteilter Speicher und Low-Power-Domäne für Cortex-M4