Einsatz im Weltall:

Strahlungstolerante FPGAs für Satelliten

Obwohl die Auflösung der Sensoren und damit die Menge der produzierten Daten in Satelliten immer größer wird, kann die Übertragungsbandbreite zur Bodenstation nicht wie benötigt ansteigen. Um die niedrigen Übertragungsraten besser nutzen zu können, müssen mehr Daten als bislang schon an Bord des Satelliten verarbeitet werden.

Halbleiter-Chips müssen beim Einsatz im Weltraum resistent gegen sogenannte SEUs (Single Event Upset) sein – Fehler, die ionisierende Teilchen in Halbleiter-Chips hervorrufen können und z.B. eine Zustandsänderung eines Bits in Speicherbausteinen oder Registern bewirken.

Da das Magnetfeld und die Atmosphäre der Erde eine abschirmende Wirkung für hochenergetische Teilchen aufweisen, treten SEUs in Meereshöhe nur relativ selten auf. Wobei das Auftreten von SEUs bei immer kleineren Fertigungsgeometrien häufiger wird, da mit kleiner Strukturgröße und höherer Taktfrequenz kleinere Energien reichen, um ein SEU zu provozieren. Satelliten sind einer erhöhten (Teilchen-) Strahlung ausgesetzt, weshalb die entsprechende Elektronik hier in höherem Maße betroffen ist.

Beim Durchqueren von Materie gibt ein ionisierendes Teilchen Energie an das umliegende Material ab, was als linearer Energietransfer (LET) bezeichnet wird. In Halbleitern führt das zu einer Änderung der Ladungsverteilung und kann somit – vereinfacht ausgedrückt – ein Umschalten bewirken.

Bislang wurden für den Weltraumeinsatz spezielle, strahlungsresistente ASICs hergestellt, die auf der einen Seite zwar hohe Rechenleistung, hohe Dichte und niedrige Leistungsaufnahme bieten, auf der anderen Seite jedoch extrem hohe Einmalkosten bei niedrigen Stückzahlen sowie lange Entwicklungszyklen und Fertigungsdauer haben – wirtschaftlich attraktiv sind strahlungsfeste ASICs nicht. Eine Alternative sind SRAM-basierte FPGAs. Allerdings erfordern die bei der Konfiguration potenziell auftretenden SEUs aufwendige Gegenmaßnahmen, wodurch sich Größe, Gewicht und Leistungsaufnahme der Bausteine erhöhen.

Strahlungsresistent mit Flash

Jobangebote+ passend zum Thema

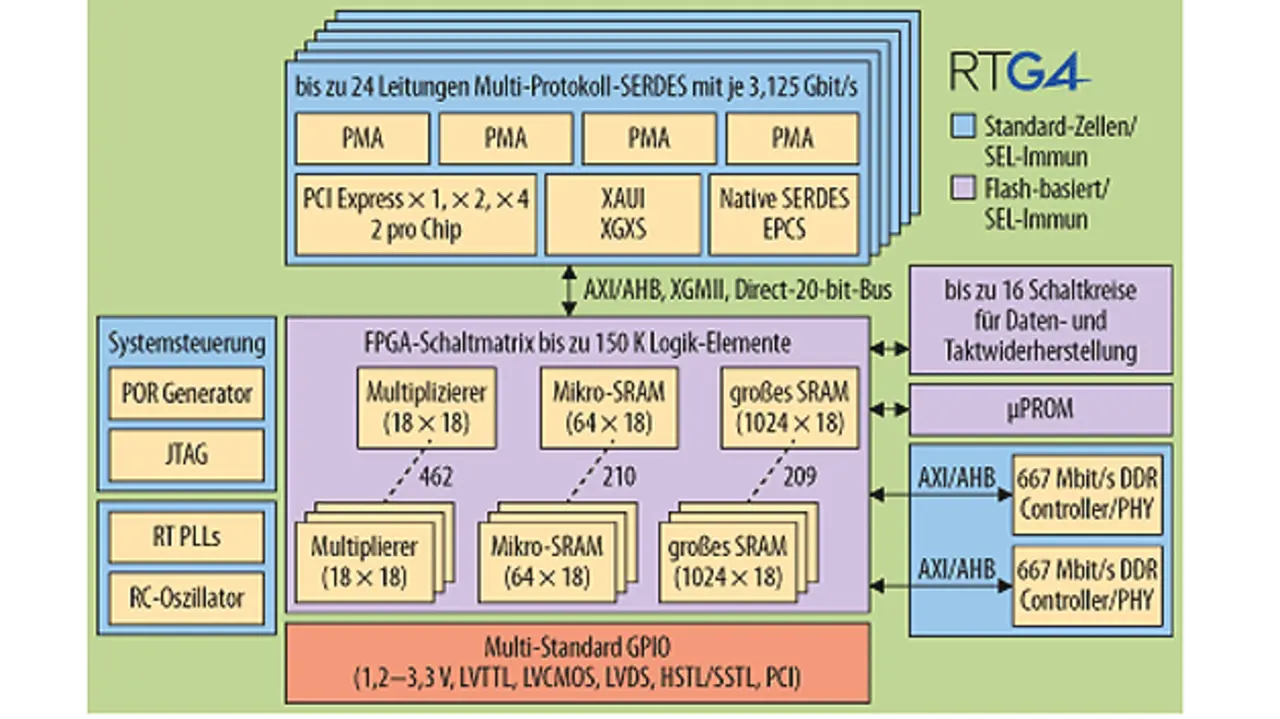

Die neuen RTG4 genannten FPGAs für den Weltraumeinsatz aus dem Hause Microsemi sind Flash-basiert und weiten den Einsatzbereich gegenüber den ProASIC3-Bausteinen deutlich aus. Es stehen statt 9 K Logik-Elementen (Lookup-Tabellen, LUTs) nunmehr bis zu 150 K LUTs zur Verfügung, dazu kommen 5 Mbit SRAM, SerDes mit maximal 75 Gbit/s Datendurchsatz (24 Leitungen a 3,125 Gbit/s) und maximal 462 18×18-bit-Multiplizierer mit maximal 126 Gigamultiplikationen pro Sekunde (Bild 1).

Zum Schutz von Halbleiter-Chips vor SEUs aufgrund kosmischer Strahlung sind drei Verfahren bekannt: Abschirmung, Codierung mit Fehlerkorrektur und dreifache Redundanz (TMR, Triple Modular Redundancy). Zur Abschirmung ionisierender Strahlung wird die zu schützende Komponente ummantelt. Diese Methode ist allerdings nur geeignet, um Teilchen relativ niedriger Energie abzufangen. Teilchen hoher Energie erzeugen beim Durchqueren der Abschirmung sog. Sekundärstrahlung. Der hauptsächliche Nachteil einer schirmenden Ummantelung ist jedoch deren zusätzliche Masse.

Beim zweiten Verfahren werden die gespeicherten Daten mittels geeigneter Methoden gegen Einzel- oder Mehrbitfehler gesichert, z.B. durch Codierung mit dem Reed-Solomon-Code (RS-Code). Im Falle eines SEU, der eine Änderung des Speicherinhaltes bewirkt, lassen sich so die korrekten Daten wiederherstellen.

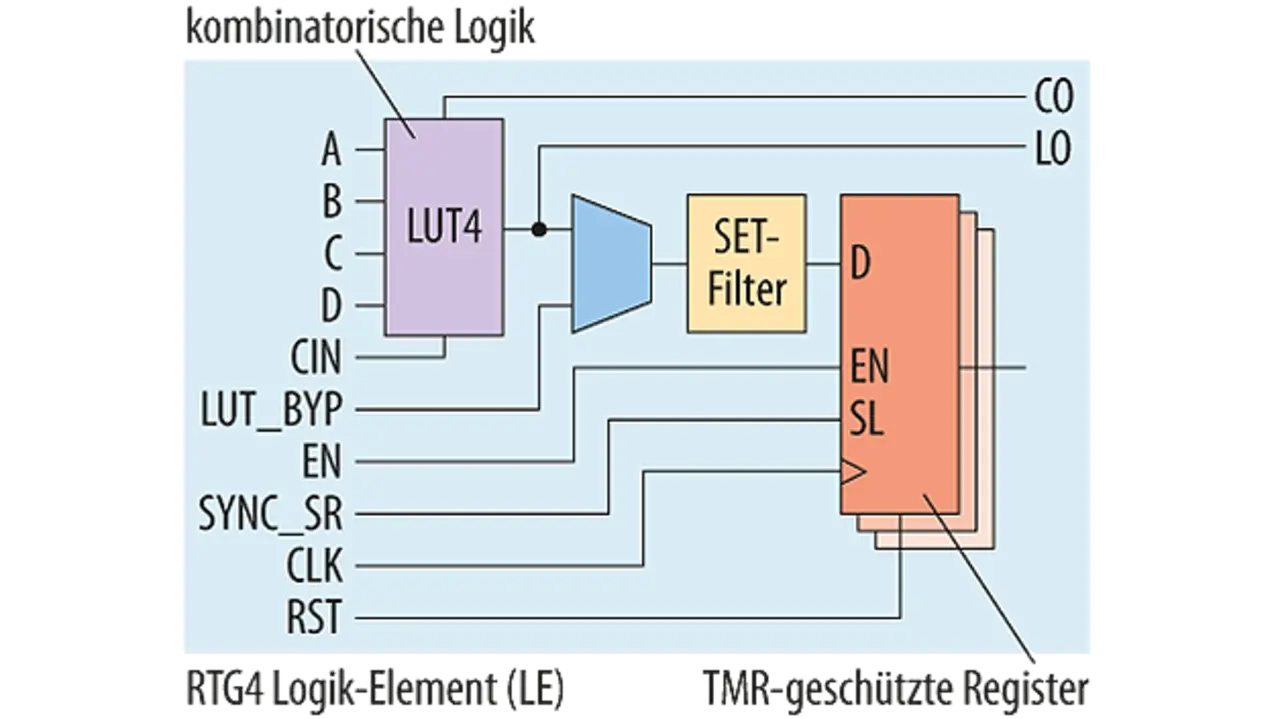

Die dritte – und bei den FPGAs der Reihe RTG4 eingesetzte – Methode basiert auf dreifacher Redundanz: Hierbei wird das abzusichernde Register durch drei identische Register und eine nachgeschaltete Entscheidungsstufe ersetzt (Bild 2). Letztere gibt immer den Ausgabewert weiter, den die Mehrheit der drei Register liefert. Ein SET-Filter (Single Event Transient) mildert durch Strahung verursachte Störimpulse der vorgeschalteten Logik ab. Microsemi verspricht eine SEU-Fehlerrate von weniger als 10-10 Fehler pro Bit und Tag und eine Strahlungsimmunität bis zu einer Energiedosis von 100 kRAD.

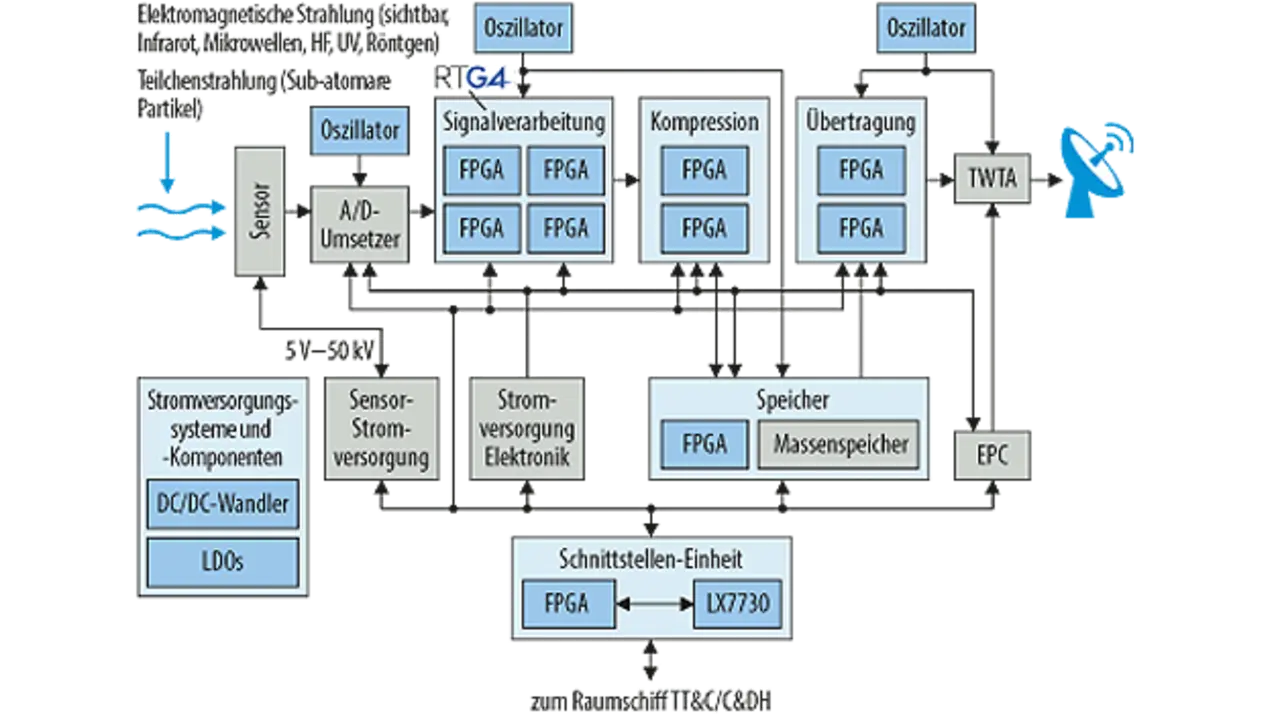

Bild 3 zeigt den Einsatzbereich der RTG4-FPGAs in einem für Sensor-Applikationen typischen Blockschaltbild. Die vom Sensor aufgefangenen Signale werden mittels eines A/D-Umsetzers digitalisiert, es folgt die Signalverarbeitung und deren anschließende Kompression, bevor sie dann gespeichert und/oder an die Bodenstation gesendet werden.

Microsemi sieht den Markt bei 100 Satelliten pro Jahr, die jeweils bis zu acht Instrumente beinhalten, von denen jedes 1 bis 12 FPGAs benötigt. Im besten Fall sind dies also 9600 FPGAs pro Jahr, eine im Vergleich zu anderen Märkten vernachlässigbare Menge mit allerdings extrem hohen Verkaufspreisen und Margen. Die Version RT4G150 ist bereits als Muster erhältlich, die Ausführung RT4G075 folgt erst Anfang 2016. In der Tabelle sind die Daten beider Derivate zusammengefasst.

| RT4G075 | RT4G150 | |

|---|---|---|

| Logik-Elemente (TMR-Register und LUT mit vier Eingängen) | 77.712 | 151.824 |

| Multiplizierer 18 x 18 bit | 224 | 462 |

| RAM [Mbit] (1,5-Kbit- und 24-Kbit-Blöcke mit ECC) | 2,8 | 5,2 |

| UPROM [Kbit] | 254 | 381 |

| DDR2/3 SDRAM Controller mit Fehlerkorrektur | 2 x 32 bit | 2 x 32 bit |

| PCI-Express-Endpunkte | 2 | 2 |

| PLLs | 8 | 8 |

| User-E/As (ohne SERDES) | 528 | 720 |

| SERDES-Leitungen (3,125 Gbit/s) | 16 | 24 |

Tabelle. Vergleich der zwei RTG4-Derivate RTG075 und RTG150. Die Version RTG150 verfügt über mehr Logikelemente, Muiltiplizierer, E/As und SERDES-Leitungen.