Vorhersage von Rechenleistung unabdingbar

Multicore-CPUs in sicherheitskritischen Echtzeitsystemen

Viele Multicore-Designs weisen Eigenschaften auf, die ihren Einsatz in sicherheitskritischen Echtzeitsystemen erschweren. Um ein Scheitern in der Integrationsphase zu vermeiden, müssen die Architektureigenschaften frühzeitig auf Echtzeitfähigkeit untersucht und der Prozessor im Hinblick auf vorhersagbare Rechenleistung konfiguriert werden.

Multicore-Prozessoren sind schon seit Jahren im PC-Bereich etabliert. Die Parallelisierung durch mehrere Rechenkerne auf einem Chip ermöglicht eine deutliche Beschleunigung von Systemen, die aus vielen unabhängigen Threads bestehen. Zudem tragen die niedrigeren Taktraten zu einer höheren Energieeffizienz bei. Nicht zuletzt wegen stark gesunkener Preise werden Multicores zunehmend auch in eingebetteten Systemen verwendet.

Im Desktop-Bereich ist eine hohe durchschnittliche Leistung ausschlaggebend; ein sicherheitskritisches, eingebettetes Echtzeitsystem hingegen muss nicht nur logisch korrekt sein, sondern auch ein korrektes Zeitverhalten aufweisen. Überschreitet eine Echtzeit-Task ihre Deadline, kann dies zu schweren Fehlern führen. Zum Nachweis, dass eine Task vor ihrer Deadline beendet ist, muss ihre längstmögliche Ausführungszeit bekannt sein, die sogenannte Worst-Case Execution Time (WCET). In einem Multitasking-System können Tasks auch unterbrochen oder blockiert werden. Dies wird bei der Antwortzeit der Task berücksichtigt, der Worst-Case Response Time (WCRT), bei der Unterbrechungseffekte zur WCET hinzuaddiert werden. Alle aktuellen Sicherheitsnormen, darunter DO-178B/DO-178C, ISO 26262, IEC 61508 und EN 50128, erfordern den Nachweis, dass genügend Ressourcen vorhanden sind, um korrekte Systemfunktion zu gewährleisten. Hierzu zählen der Nachweis sicherer oberer Schranken des maximalen Speicherverbrauchs und der maximalen Ausführungs- und Antwortzeiten. Bei Anwendungen gemischter Kritikalität unterliegt zudem die gesamte Anwendung der höchsten vorkommenden Sicherheitsanforderungsstufe, es sei denn, dass nachgewiesen werden kann, dass alle Sicherheitsfunktionen räumlich und zeitlich voneinander unabhängig sind.

Methodisch bestimmen

Wie kann nun das Zeitverhalten methodisch bestimmt werden? Bei direkten Zeitmessungen mit Logikanalysatoren bzw. Debuggern oder Hardware-Simulation werden Zeiten nur für jeweils eine konkrete Eingabe ermittelt. Eine vollständige Testabdeckung ist in der Regel nicht zu realisieren, ein sicheres Testende-Kriterium nicht vorhanden. Hinzu kommt, dass – z.B. aufgrund von Caches – bei allen modernen Prozessoren das Zeitverhalten einer Instruktion von den zuvor ausgeführten Instruktionen abhängt, sodass selbst eine MC/DC-Abdeckung zur Bestimmung der längstmöglichen Ausführungszeit unzureichend ist. Verfahren auf Basis von Code-Instrumentierung verändern den Code, was das Verhalten der Cache-Speicher signifikant verändern kann. Die gemessenen Zeiten der instrumentierten Software können weit vom Zeitverhalten des ursprünglichen Systems abweichen.

Jobangebote+ passend zum Thema

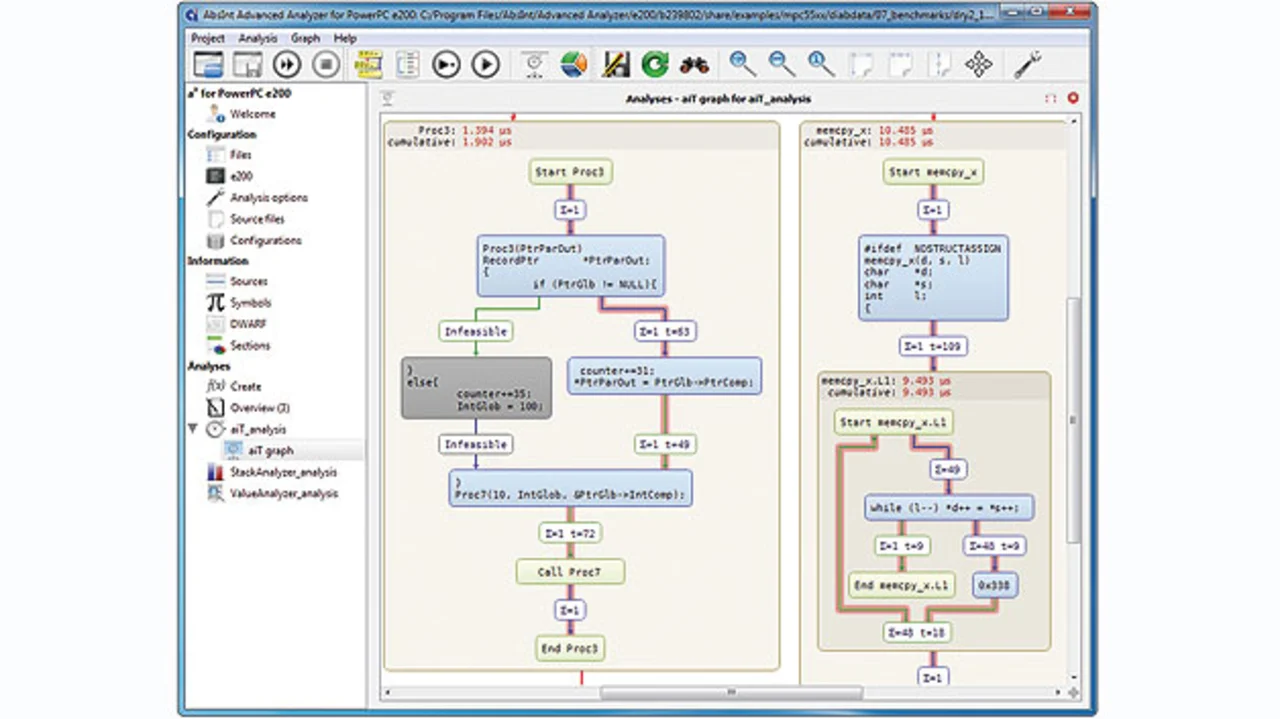

Eine Methode, Deadline-Überschreitungen auszuschließen, ist die sichere statische Analyse. Statische Analysen werden als sicher bezeichnet, wenn mathematisch bewiesen wurde, dass sie keine potenziellen Fehler übersehen. Solche Beweise sind durch eine abstrakte Interpretation möglich, eine formale Methode für statische Programmanalysen [1]. Statische-Analyse-Tools auf Basis der abstrakten Interpretation haben sich in den letzten Jahren zunehmend verbreitet und können als Stand der Technik zum Nachweis nichtfunktionaler Korrektheitseigenschaften angesehen werden. Räumliche Unabhängigkeit kann durch sichere statische Analysatoren nachgewiesen werden, die die Abwesenheit von Stack-Überläufen, ungültigen Zeigerzugriffen oder anderen Laufzeitfehlern beweisen können [2, 3]. Garantierte obere Schranken für die längstmögliche Ausführungszeit von Tasks können beispielsweise durch den Analysator aiT von AbsInt berechnet werden [4]. Bild 1 zeigt die Kontrollflussgraph-Visualisierung von aiT mit kritischem Ausführungspfad.

- Multicore-CPUs in sicherheitskritischen Echtzeitsystemen

- Statische Analyse liefert präzise Ergebnisse