Mikrocontroller für Digital Power

Stromversorgungen besser regeln

Fortsetzung des Artikels von Teil 1

Bausteinspezifische Peripherie

Die DSCs enthalten einen neuen 12-bit-A/D-Wandler (ADC) mit mehreren SAR-Cores (Successive Approximation Register), sie können somit mehrere Analogeingänge gleichzeitig abtasten. 12-bit-Ergebnisse ergeben sich damit in weniger als 300 ns. Die SAR-Cores verfolgen das Eingangssignal kontinuierlich, es ist keine Abtastzeit erforderlich. Erfasst der ADC ein Triggerevent, startet er automatisch den Wandlungsvorgang. Da die Abtast-/Wandlungszeit als Verzögerung in der Regelschleife angesehen wird, minimiert sich die Gesamt-Abtast-/Wandlungslatenz und verringert so die Verschlechterung des Phasenabstands.

Jobangebote+ passend zum Thema

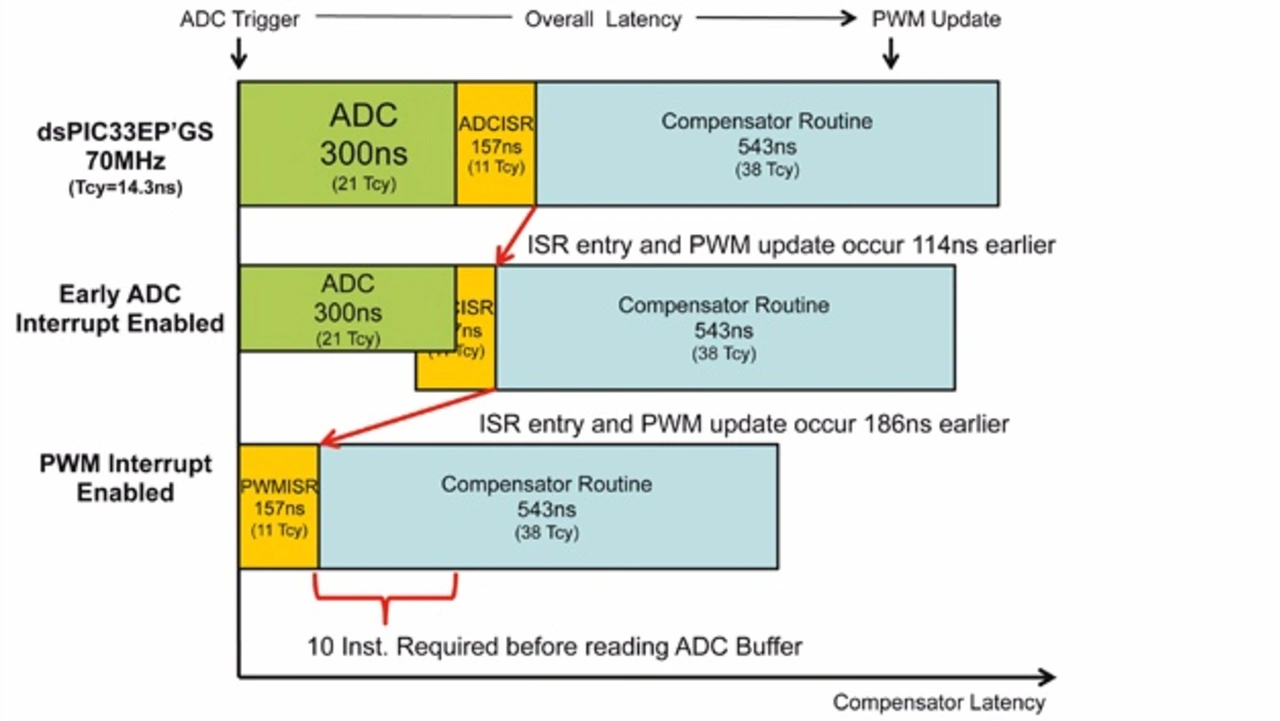

Eine Besonderheit des ADC ist dessen Fähigkeit, den Interrupt zu erzeugen, bevor die Wandlung abgeschlossen ist. Diese Early-Interrupt-Funktion verringert die Interrupt-Wartezeit vom Zeitpunkt, an dem der ADC die Wandlung durchgeführt hat, bis zum Start der Regelschleifensoftware (Interrupt). Das maximal wählbare Early-Interrupt-Timing (Bild 1) beträgt acht ADC-Takte (Tads). Beim schnellsten Durchsatz verringert sich damit die Zeitdauer um 114 ns, um in den Kompensatoralgorithmus zu gelangen. Dadurch lässt sich die Gesamtlatenz in der Regelschleifensoftware weiter verringern.

Des Weiteren kann das ADC-Modul mehrere digitale Komparatoren miteinbeziehen. Diese lassen sich so konfigurieren, dass sie einen Interrupt ausgeben, wenn das gewandelte Analogergebnis außerhalb (oder innerhalb) festgelegter Grenzwerte liegt. Dies mag nicht wie eine Funktion erscheinen, die sich direkt auf die Abtastfrequenz auswirkt – es ist aber definitiv möglich. Weniger MIPS werden verbraucht, wird Software von der CPU ausgelagert und nur bei einem Fehlerzustand ausgeführt. Damit ließe sich die Abtastrate der Regelschleife erhöhen. Dies hängt vor allem von der Software ab und nicht alle Anwendungen sind imstande, diese neue Funktion zu nutzen. Dies kann jedoch die CPU-Arbeitslast verringern, wenn z. B. Spannung oder Temperatur zu überwachen sind.

Um die Zeitdauer zwischen ADC-Trigger und Zurückschreiben des Regelausgangs weiter zu verkürzen, lassen sich die PWM-ISR anstelle der ADC-ISR (Interrupt Service Routine) und die ADC-Early-Interrupt-Funktion einsetzen. Im Allgemeinen triggert die PWM den ADC, um die Wandlung zu starten – nun erzeugt dieser aber auch gleichzeitig seinen eigenen Interrupt. Da sich der Kompensatoralgorithmus innerhalb der PWM-ISR befindet, beginnt die Software den Kompensatoralgorithmus auszuführen, bevor die aktuellen Rückkopplungsdaten vom A/D-Wandler zur Verfügung stehen. Zwischen der Softwareausführung und dem Ende der ADC-Wandlung vergehen in etwa 143 ns. Daher müssen mindestens zehn Befehle platziert werden, bevor der ADC-Ergebnispuffer gelesen werden kann – wenn der Mikrocontroller bei seiner maximalen Taktfrequenz arbeitet. Falls der Kompensatoralgorithmus so aufgebaut ist, dass diese Technik eingesetzt werden kann, verringert sich der Zeitaufwand, um die Kompensatorroutine aufzurufen, um 45 %. Vorgriff: Bild 4 beschreibt unten auch das Early-Interrupt-Timing mit einer PWM-Interrupt-Serviceroutine. Diese Methode sollte allerdings nur mit dem vorhersagbaren Timing der SAR-Cores angewendet werden.

Aufbau des Kompensatoralgorithmus

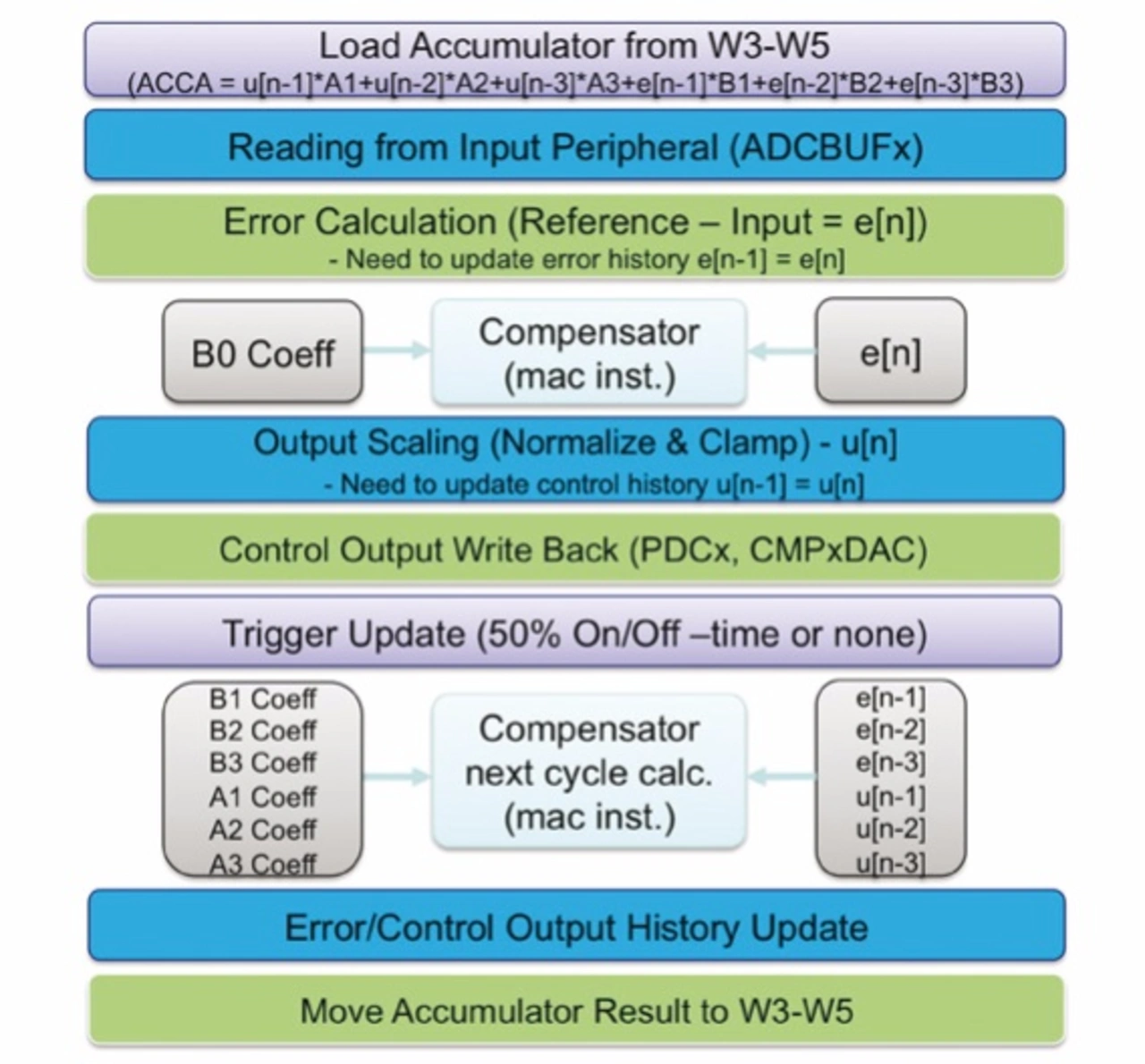

Der Aufbau des Kompensatoralgorithmus spielt eine wichtige Rolle bei der Zeitdauer, die zum Auffrischen der Regelausgangsvariablen erforderlich ist. Mit den alternierenden Arbeitsregistern lässt sich der Algorithmus so schreiben, dass die einzig erforderlichen Berechnungen vor dem Auffrischen des Regelausgangs die Multiplikation des aktuellen Fehlers mit dem Koeffizienten B0 und die Addition dieses Ergebnisses mit dem kumulierten Ausgang des vorherigen Zyklus ist. Natürlich sind die Rückwärtsnormalisierung und das Clamping noch vorhanden, dies verringert allerdings die Rückschreibdauer des Regelausgangs erheblich, ohne dafür einen speziellen Akkumulator zu benötigen. Bild 2 beschreibt, wie der Kompensatoralgorithmus ausgelegt werden kann, um die kürzeste Aktualisierungszeit zu erreichen. Die Regelausgang-Rückschreibzeit beträgt nun weniger als 300 ns nach Eintritt des Kompensatoralgorithmus. Der Nutzen daraus wird in den folgenden Abschnitten deutlich.

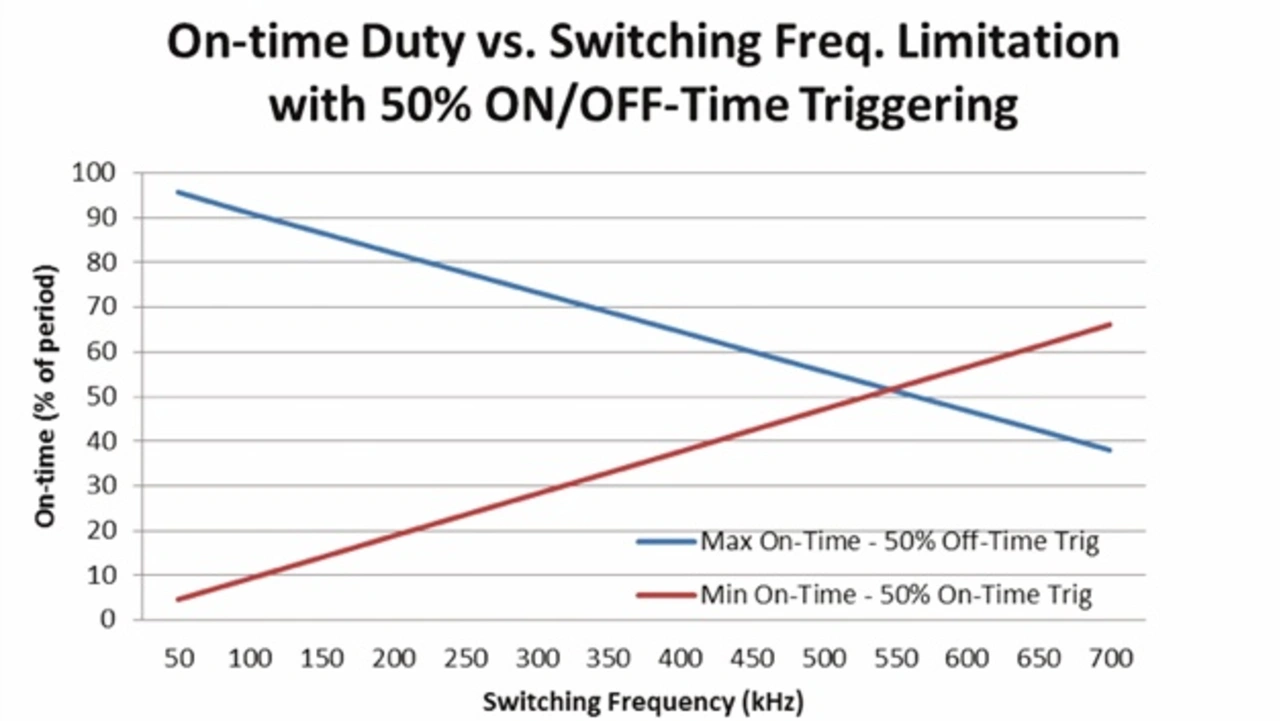

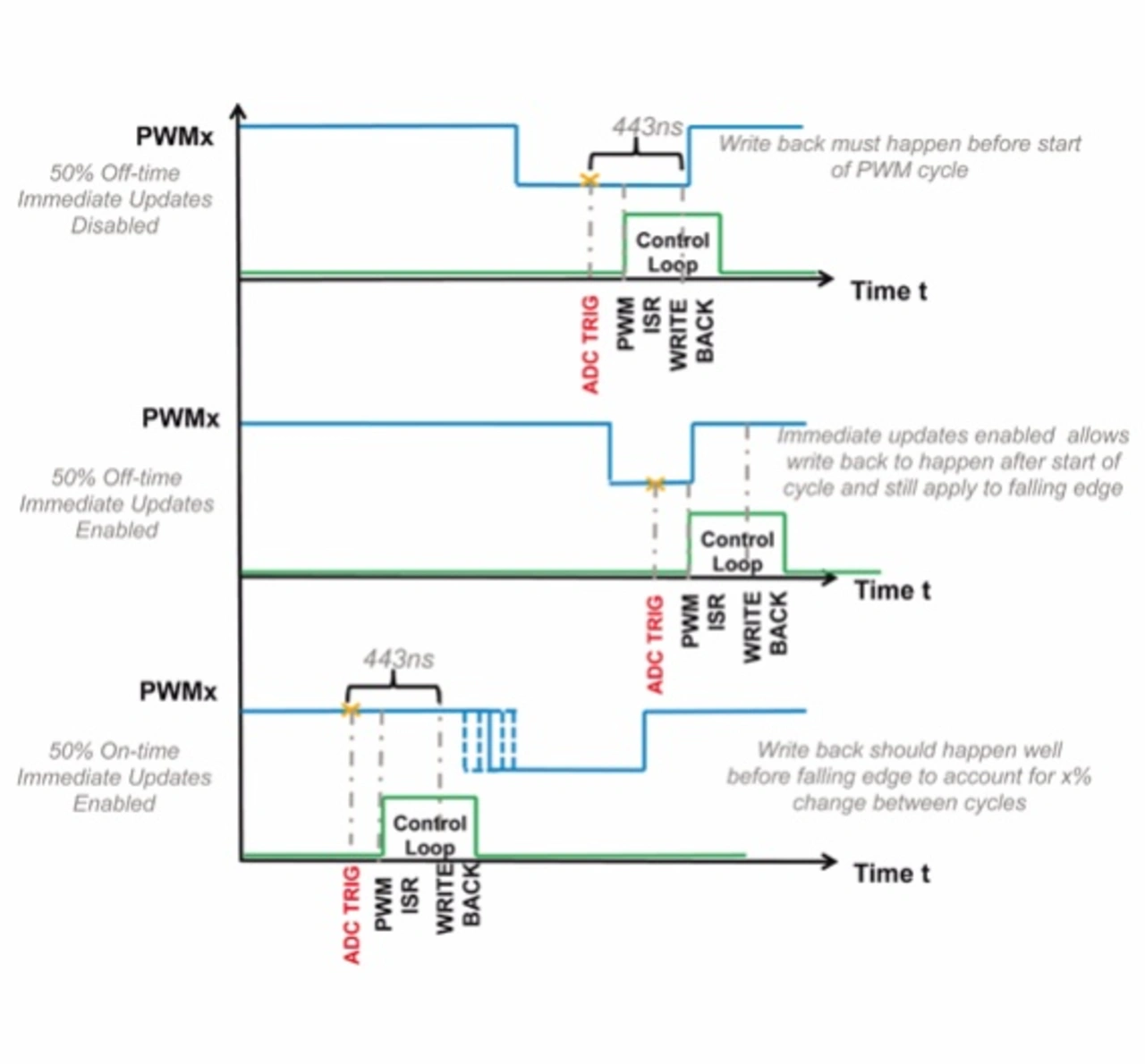

Wie wirken sich diese verschiedenen Funktionen nun auf die Phasenreserve aus? In Voltage-Mode- und Average-Current-Mode-Regelsystemen kann die Spannung am Ausgangskondensator oder der Spulenstrom bei 50 % der Auszeit abgetastet werden. Am häufigsten findet eine Abtastung bei 50 % der Einschaltzeit statt, um genügend Zeit für die Verarbeitung des Regelalgorithmus bereitzustellen, bevor der nächste PWM-Zyklus beginnt. Mit all den genannten Funktionen ist eine einfache Abtastung des Rückkopplungssignals während der Auszeit sowie ein Rückschreiben auf den Regelausgang möglich, bevor der nächste PWM-Zyklus beginnt. Bild 3 beschreibt beispielhaft die geschätzten Tastgrad-Grenzen über die Schaltfrequenz. Bild 4 zeigt ein Zeitdiagramm bei 50 % Auszeit. Der höhere Phasenreserve hängt vom Tastgrad ab. Wird ein Durchschnitt bei 50 % Tastgrad gebildet, steigt die Phasenreserve um die Hälfte – verglichen zu der Messung bei 50 % Einschaltzeit.

Die »GS«-DSCs bieten einen sofortigen Aktualisierungsmodus, der (falls aktiviert) die PWM-Parameter innerhalb des aktuellen Zyklus aktualisiert, wenn das SFR (Special Function Register) ebenfalls beschrieben wird. Dies trifft auf die Phase, Periode, Totzeit und den Tastgrad zu – jeweils mit einer Auflösung von 1 ns. Bei 50 % Auszeit wurde festgelegt, dass das Rückschreiben des Regelausgangs vor dem Start des nächsten PWM-Zyklus stattfinden muss. Dies begrenzt die maximale Einschaltzeit bei einer bestimmten Schaltfrequenz. Sind sofortige Updates aktiviert, ist dies nicht länger der Fall. Damit lassen sich die Grenzwerte für den Tastgrad und/oder die Schaltfrequenz weiter erhöhen, was die Phasenreserve weiter bessert. Bild 4 beschreibt das Timing für beide 50-%-Auszeit-Implementierungen.

Steigerung um 16°

Der Fall, bei der die Phasenreserve am größten ist, ist das Abtasten der Rückkopplungssignals bei 50 % Einschaltzeit, während gewährleistet ist, dass der neue Regelausgang bei der abfallenden Flanke des aktuellen PWM-Zyklus angelegt wird. Damit aktualisiert der DSC die aktive Flanke des PWM-Tastgrads auf Basis des Komparatorausgangs, der gerade im gleichen PWM-Zyklus aufgerufen wurde. Dieser optimale Fall lässt sich aber nicht in allen Anwendungen umsetzen, da Einschränkungen bei der Mindest-Einschaltzeit vorliegen. Bild 3 beschreibt die Mindest-Einschaltdauer als Prozentanteil der Schaltperiode über verschiedene Schaltfrequenzen. Findet beispielsweise Boost-PFC-Schalten bei 100 kHz statt, beträgt die geforderte Mindest-Einschaltzeit etwas weniger als 10 % der Periode. Da der Mindest-Tastgrad an der Spitze der AC-Netzspannung auftritt (bei einer Nenneingangsspannung von 220 V), beträgt die Tastgradanforderung etwa 22 %. Damit steht genügend Spielraum für die sofortige Aktualisierung bereit – mit großer Schwankungsbreite des Regelausgangs. Nimmt die Eingangsspannung weiter zu, erscheint die sofortige Aktualisierung wie das Ende eines Zyklus-Updates. Damit verringert sich die Phasenreserve. Dies tritt jedoch außerhalb der Nennbedingungen auf. Bild 4 beschreibt auch das Timing-Diagramm bei einem Anwendungsfall mit 50 % Einschaltzeit-Trigger.

In diesem Beispiel wurde ein synchroner Abwärtswandler mit allen hier beschriebenen Techniken belegt. Die Ergebnisse zeigen, dass sich die Abtastrate von jedem zweiten PWM-Zyklus (175 kHz) auf jeden PWM-Zyklus (350 kHz) erhöht, ohne mehr Rechenleistung zu beanspruchen. Der Kompensator wurde für ein schnelles Zurückschreiben auf die Regelausgangsvariable ausgelegt; der PWM-Interrupt wurde für die Verarbeitung der Regelschleife erzeugt, und 50 % Einschaltzeit mit sofortigen Aktualisierungen wurden freigegeben. Damit erhöhte sich die Phasenreserve um etwa 16°. Zu Beginn war die Schleifenverstärkung mit einem Phasenreserve von 46° geradeso stabil, nach der Optimierung war sie mit 62° Phasenreserve fast so gut wie ein analoger Regelkreis. Die hier beschriebenen Techniken zur Steigerung der Phasenreserve sind kein Allheilmittel, sie lassen sich aber in einer Vielzahl von Designs anwenden.

- Stromversorgungen besser regeln

- Bausteinspezifische Peripherie