ARM TechCon 2016

Cortex-M23 und –M33 sind erste ARMv8-M-CPUs

Fortsetzung des Artikels von Teil 3

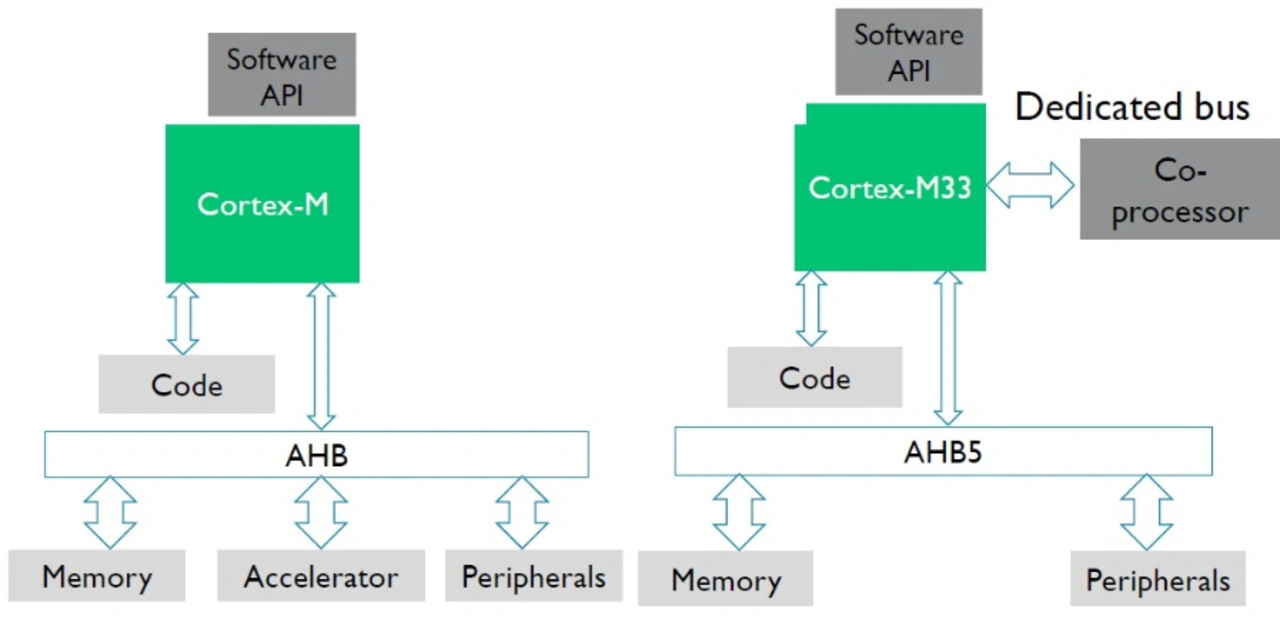

Koprozessor-Schnittstelle entlastet AHB-5-Bus

Einen echten Fortschritt bringt die neue Koprozessor-Schnittstelle. In Bild 6 links ist der bislang eingesetzte Ansatz der Cortex-M-CPUs dargestellt, wo sich Hardware-Beschleuniger, Speicher und Peripherie den AHB-Bus teilen. Da die Chips immer komplexer werden (mehr Speicher, mehr Peripherie-Blöcke, Beschleuniger für Verschlüsselung, mathematische Funktionen u.v.m.) wurde es Zeit, den AHB-Bus entlasten zu können. Durch die neue Schnittstelle, welche die Anbindung von bis zu 8 Beschleunigern direkt an die CPU erlaubt (Bild 6 rechts), wird dies realisiert. Das Ganze funktioniert so, daß es eine Transfer-Instruktion gibt, über welche eine ID (welcher Beschleuniger soll adressiert werden) und ein bis zwei 32-bit-Werte in Registern übergeben werden. Alternativ kann die weitere Codeausführung warten, bis der Koprozessor Ergebnisdaten zurückgeliefert hat, man kann aber auch einen Interrupt konfigurieren, der ausgelöst wird, wenn die Daten bereitstehen.

Jobangebote+ passend zum Thema

Microchip lizensiert Cortex-M23 und/oder M33

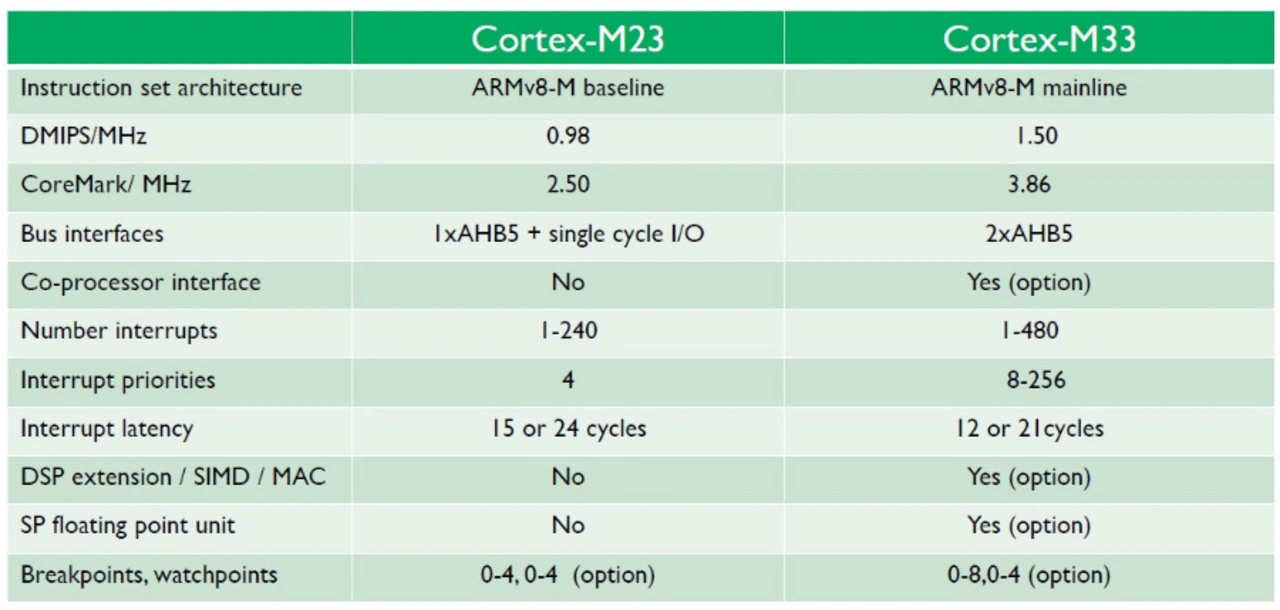

Bild 7 fasst die wichtigsten Eigenschaften der beiden neuen CPUs nochmals zusammen. Diese dürften in den Implementierungen von ARMs Lizenznehmer auch als gemischtes Doppel auf einem Chip auftreten. Der M23 könnte in einer Always-On-Domäne als Hauptprozessor zum Einsatz kommen und der M33 optional nur bei hoher Rechenlast für spezielle Aufgaben dazu aktiviert werden. Durch die TrustZone-Implementierung bei ARMv8-M sowie die Vereinheitlichungen beim Debugging sind beide CPUs für Multicore-Implementierungen geradezu prädestiniert.

Eine Überraschung wartete bei der Bekanntgabe der ersten Lizenznehmer für M23 und/oder M33: Neben den üblichen Verdächtigen ST Microelectronics, NXP, SiliconLabs und Analog Devices sind auch Renesas (für ihre Synergy-Familie), Nuvoton (ein in Deutschland vergleichsweise unbekannter taiwanischer Hersteller, der bislang auf Cortex-M0 und –M4 setzte) und – Überraschung – auch Microchip dabei. Der Hersteller aus Arizona setzte ja bis zum Kauf von ARM-Lizenznehmer Atmel mit seinen PIC32-MCUs auf die Konkurrenzarchitektur MIPS. Es ist schwer vorstellbar, daß Microchip langfristig zwei Architekturen unterstützt, insofern ist die Lizensierung der neuen Bausteine von ARM schon mehr als ein Fingerzeig.

Literatur:

[1] Riemenschneider, F.: Architektur ARMv8-M bringt Hardware-Security in Mikrocontroller. DESIGN&ELEKTRONIK Ausgabe 1/2016, S. 23 ff.

- Cortex-M23 und –M33 sind erste ARMv8-M-CPUs

- Zahlreiche Konfigurationsoptionen

- Cortex-M33 mit neuer Pipeline

- Koprozessor-Schnittstelle entlastet AHB-5-Bus