Microchip stellt SAM L10/L11-MCUs vor

arm Cortex-M23 plus On-Chip-Security für das IoT

Mit bislang unerreichter Sicherheit und Energieeffizienz sowie seiner bekanntermaßen führenden Touch-Technologie will Microchips neue Mikrocontroller-Familie L10/L11 das IoT erobern. Bei zahlreichen Anwendungen könnte dies auch tatsächlich gelingen.

Die neue MCU-”Familie” mit zwei Mitgliedern L10 und L11 unterscheidet sich dahingehend von anderen MCU-Familien, deren einzelne Derivate sich häufig nur durch Speichergröße und/oder mehr oder weniger Peripherien differenzieren, dass zwischen L10 und L11 ein ganz erheblicher Unterschied besteht: Während die arm Coretx-M23-CPU des L11 arms TrustZone-Technologie implementiert, fehlt diese beim L10. Dies macht natürlich einen signifikanten Unterschied hinsichtlich der von Microchip beworbenen Security-Eigenschaften aus.

Um nicht zu große Redundanzen in diesem Beitrag aufkommen zu lassen, verweisen wir hinsichtlich einer detaillierten technischen Beschreibung der CPU auf unseren diesbezüglichen Beitrag von ARMs Entwicklerkonferenz TechCon, auf welcher sie Ende 2016 enthüllt wurde. Hinsichtlich der Architektur ARMv8-M und ihrer TrustZone-Technologie verweisen wir auf einen weiteren technischen Beitrag´von der TechCon 2015.

Jobangebote+ passend zum Thema

| Eigenschaft | Cortex-M23- Optionen | Implementierung SAML10 | Implementierung SAML11 |

|---|---|---|---|

| Speicherschutzeinheit(MPU) | Keine, 4, 8, 12 oder 16 Regionen | Eine MPU mit 4 Regionen | Zwei MPUs mit jeweils 4 Regionen (eine für nicht sicheren Bereich, eine für den mittels TrustZone abgesicherten Bereich) |

| Security Attribute Einheit (SAU) | Keine, 4 oder 8 Regionen | Keine | Keine |

| Implementation Defined Attribution Unit (DAU) | Keine oder implementiert | Keine | Implementiert (TrustZone vorhanden) |

| SysTick-Timer | Keiner, 1 oder 2 | Einer | Zwei (einer für nicht sicheren Bereich, einer für den mittels TrustZone abgesicherten Bereich) |

| Vector Table Offset Register | Keine, 1 oder 2 | Einer | Zwei (einer für nicht sicheren Bereich, einer für den mittels TrustZone abgesicherten Bereich) |

| Reset von allen Registern | Ja oder Nein | Nein | Nein |

| Multiplizierer | Schnell (1 Taktzyklus) oder langsam (32 Taktzyklen) | Schnell | Schnell |

| Dividierer | Schnell (17 Taktzyklen) oder langsam (34 Taktzyklen) | Schnell | Schnell |

| Anzahl externe Interrupts | 0-240 | 43 | 45 |

| Befehle laden | 16-bit oder 32-bit | 32-bit | 32 bit |

| I/O-Port mit 1 Taktzyklus Zugriffszeit | Ja oder Nein | Ja | Ja |

| Clock-Gating | Ja oder Nein | Ja | Ja |

| Byte-Reihenfolge im Speicher | Little-Endian oder Big-Endian | Little-Endian | Little-Endian |

| Unterstützung von Halt-Debug | Ja oder Nein | Nein | Nein |

| Wake-Up-Interrupt-Controller (WIC) | Keiner oder implementiert | Keiner | Keiner |

| Anzahl Breakpoints | 0,1, 2, 3 oder 4 | 4 | 4 |

| Anzahl Watchpoints | 0, 1, 2, 3 oder 4 | 2 | 2 |

| Cross Trigger Schnittstelle (CTI) | Ja oder Nein | Nein | Nein |

| Micro Trace Puffer (MTB) | Ja oder Nein | Nein | Nein |

| Embedded Trace Macrocell (ETM) | Ja oder Nein | Nein | Nein |

| JTAG SW Debug-Protokoll | JTAG- oder Serial-Wire Schnittstellen zum DAP | Serial-Wire | Serial-Wire |

| Multi-Drop für Serial-Wire | Ja oder Nein | Nein | Nein |

Tabelle 1. Konfiguration des arm Cortex-M23 für die Mikrocontroller SAM L10 und SAM L11. Quelle: Microchip.

Die Implementierung des Cortex-M23 in den neuen Microchips-MCUs ist in Tabelle 1 dargestellt. Der entscheidene Unterschied ist die sogenannte “Defined Attribution Unit (DAU)”, welche darüber entscheidet, ob die TrustZone-Technologie aktiviert ist oder nicht. Bis auf den fehlenden Wake-Up-Controller (WIC, ist wegen Microchips PicoPower-Technologie nicht relevant, dazu später mehr) und die fehlende Security Attribute Unit (SAU) hat Microchip – wenn man von den Debugging-Optionen wie ETM für Echtezit-On-Chip-Tracing oder MTB für die Aufzeichnung von Trace-Informationen in einem RAM-Puffer mal absieht – fast die Maximal-Konfiguration implementiert, wobei beim L11 auf Grund der Trennung in einen sicheren und einen unsicheren Bereich diverse Eigenschaften wie MPU oder SysTick-Timer doppelt vorhalten muß.

Positiv ist die Tatsache, dass ein Instruktions-Fetch von 32 bit implementiert wurde. Damit können beim M23 alle 2 Taktzyklen über den 32-bit-Bus jeweils zwei 16-bit-Werte gemeinsam aus dem Flash-Speicher geladen werden, was natürlich besonders bei sequentiellem Code Vorteile bringt, da weniger häufig auf den stromfressenden Flash-Speicher zugegriffen werden muss. Desweiteren wurde auch die „Schnellzugriffsoption auf I/O“ implementiert, bei welcher in jeweils einem statt zwei Taktzyklen auf I/Os zugegriffen werden kann, weil parallel zum AHB-5-Bus ein weiterer Port installiert wird. Über den kann dann doppelt so schnell auf GPIOs und Register zugegriffen werden (eine LOAD/STORE-Anweisung kostet normal 2 Taktzyklen), für Speicherzugriffe eignet sich der Schnellzugriffs-Port dagegen nicht.

Besonders für Echtzeitanwendungen wichtig ist die ebenfalls von Microchip implementierte Möglichkeit, die Interrupt-Vektor-Tabelle vom Flash-Speicher ins RAM zu verschieben. Da z.B. die Löschung eines Flash-Blocks mehrere ms dauern kann und der Controller in dieser Zeit „blind“ für Interrupts ist, weil die Interrupt-Vektoren im für diesen Zeitraum blockierten Flash-Speicher liegen, ist er für diverse Echtzeitanwendungen unbrauchbar. Beim M23, wie er im L10/L11 implementiert ist, kann man die Vektor-Tabelle ins RAM verschieben, so daß auch während eines Flash-Schreib- oder Lösch-Vorgangs Interrupts verarbeitet werden können.

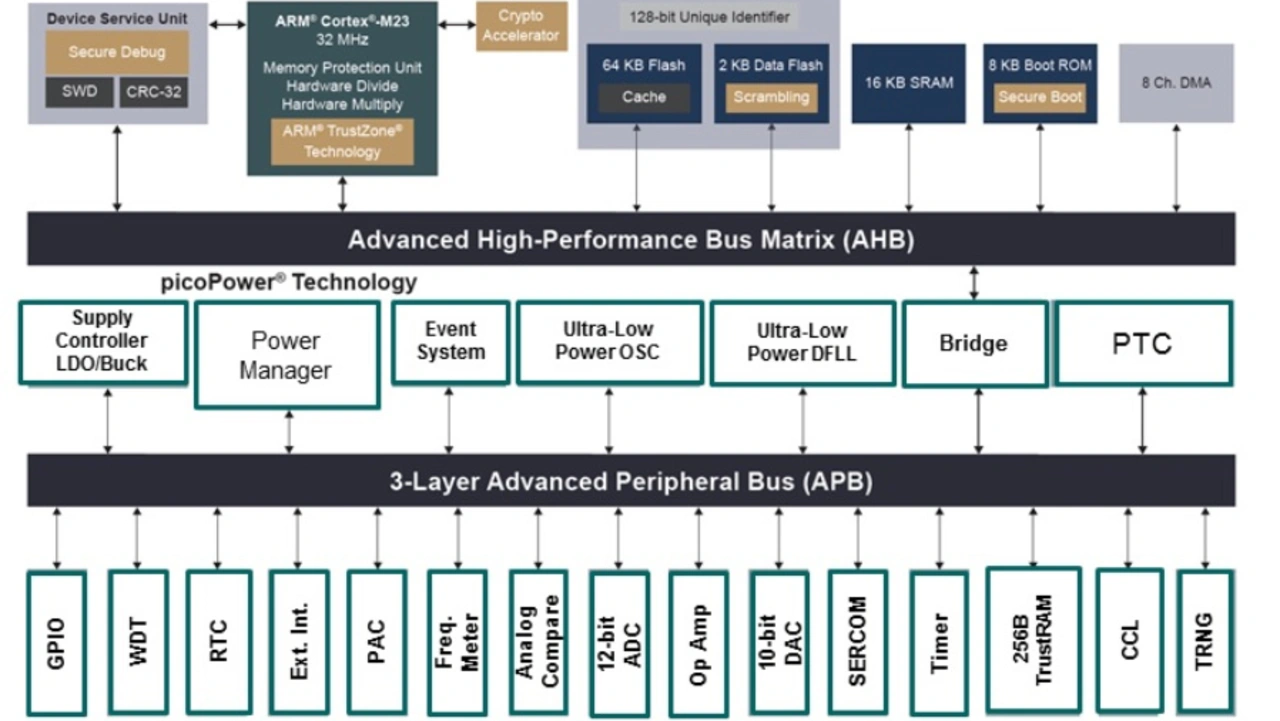

SAM L11 – alles für Security

Bild 1 zeigt das Blockdiagramm des SAM L11, alle gelb markierten Blöcke, die für erweiterte On-Chip-Sicherheit wichtig sind, fehlen auf dem L10. Neben der mit 32 MHz getakteten CPU finden sich je nach Derivat 16, 32 oder 64 KB Flash-Speicher, der über einen einstufigen Cache mit der AHB-Schaltmatrix verbunden ist, und 4, 8 oder 16 KB SRAM auf dem Chip. Dazu kommen im Fall des L11 noch 8 KB Boot-ROM für einen sicheren Boot-Loader, der bei Firmware-Upgrades wichtig ist, 2 KB Daten-Flash für die nichtflüchtige Speicherung von Daten sowie 256 Byte sogenanntes TrustRAM als sicherer Speicher für Kunden-Schlüssel.

Nicht weiter von Microchip detaillierte Anti-Tamper-Maßnahmen auf Chip-Ebene und ein Hardware-Beschleuniger für Verschlüsselungen ergänzen das Sicherheitspaket. Um zu verhindern, dass ein Angreifer illegal Informationen abruft oder verändert, sind die Chips so konzipiert, dass die Informationen nicht über externe Mittel zugänglich sind und nur von der embedded-Software abgerufen werden können, die die entsprechenden Sicherheitsmaßnahmen enthält.

Wenn man sich die Liste der möglichen Angriffe anschaut – physikalische Angriffe verschiedener Formen (Mikrosondierungen, Bohrer, Feilen, Lösungsmittel, etc.), Einfrieren des Gerätes, Anlegen von nicht spezifizierten Spannungen oder Überspannungen, Anlegen ungewöhnlicher Taktsignale, Induktion von Softwarefehlern durch Strahlung (z.B. Mikrowellen oder ionisierende Strahlung), Messung des genauen Zeit- und Energiebedarfs bestimmter Vorgänge – ist es natürlich generell schwierig, eine 100%-Sicherheit zu erzielen.

Manipulationssichere Chips können so ausgelegt sein, dass sie ihre sensiblen Daten (insbesondere kryptografische Schlüssel) auf Null setzen, wenn sie das Eindringen ihrer Sicherheitskapselung oder nicht spezifikationsgerechte Umgebungsparameter erkennen. Ein Chip kann sogar als "cold zeroisation" eingestuft werden, d.h. die Fähigkeit, sich selbst zu nullstellen, auch wenn seine Spannungsversorgung gestört ist. Ob dies beim SAM L11 der Fall ist, wissen wir nicht, nehmen es aber an.

Wir wissen ebenfalls nicht gesichert, welche Hardware-Verschlüsselung auf dem SAML11 implementiert wurde, nehmen jedoch an, dass es sich um die auch u.a. im PIC implementierte Engine handelt, die neben AES-Verschüsselung 128/192/256 (auch im GCM-Modus), Hash-basierte Verschlüsselung (SHA-1, SHA-256, MD-5, HMAC) und einen Zufallszahlengenerator bereitstellt. Auf dem L10 ist die Verschlüsselungs-Engine nicht implementiert.

Ansonsten wurde auch Microchips patentierte PicoPower-Technik mit SleepWalking implementiert. Konkret gemeint sind Verfahren wie Back-Biasing vom SRAM zur Reduzierung von Leckströmen im Schlafmodus oder Sleep-Modi, die nicht nur das Taktsignal abschalten (Clock-Gating), um die Schaltverluste zu stoppen, sondern auch den Strom aus den Subdomänen entfernen, um Leckstöme vollständig zu eliminieren.

Sleep-Walking ist eine Technologie, die es Peripheriegeräten ermöglicht, bei Bedarf ein Taktsignal anzufordern, um aus dem Schlafmodus aufzuwachen und Aufgaben auszuführen, ohne CPU, Flash-Speicher und andere Peripherien einschalten zu müssen. Dazu kommt Microchips proprietäres Event-System, das es ermöglicht, dass Peripheriegeräte zusammen arbeiten, um komplexe Aufgaben mit minimaler Gatter-Zahl und möglichst wenig Energie zu lösen. Die kapazitive Touch-Sensing-Peripherie kann zudem in allen Betriebsmodi betrieben werden und unterstützt das Aufwecken bei Berührung.

Der 12-bit-A/D-Wandler hat eine Abtastrate von 1 MSPS, der 10-bit-D/A-Wandler kommt auf 350 KSPS.

- arm Cortex-M23 plus On-Chip-Security für das IoT

- Typische Anwerndungen für den SAM L11