ARM TechCon 2016

Cortex-M23 und –M33 sind erste ARMv8-M-CPUs

Fortsetzung des Artikels von Teil 1

Zahlreiche Konfigurationsoptionen

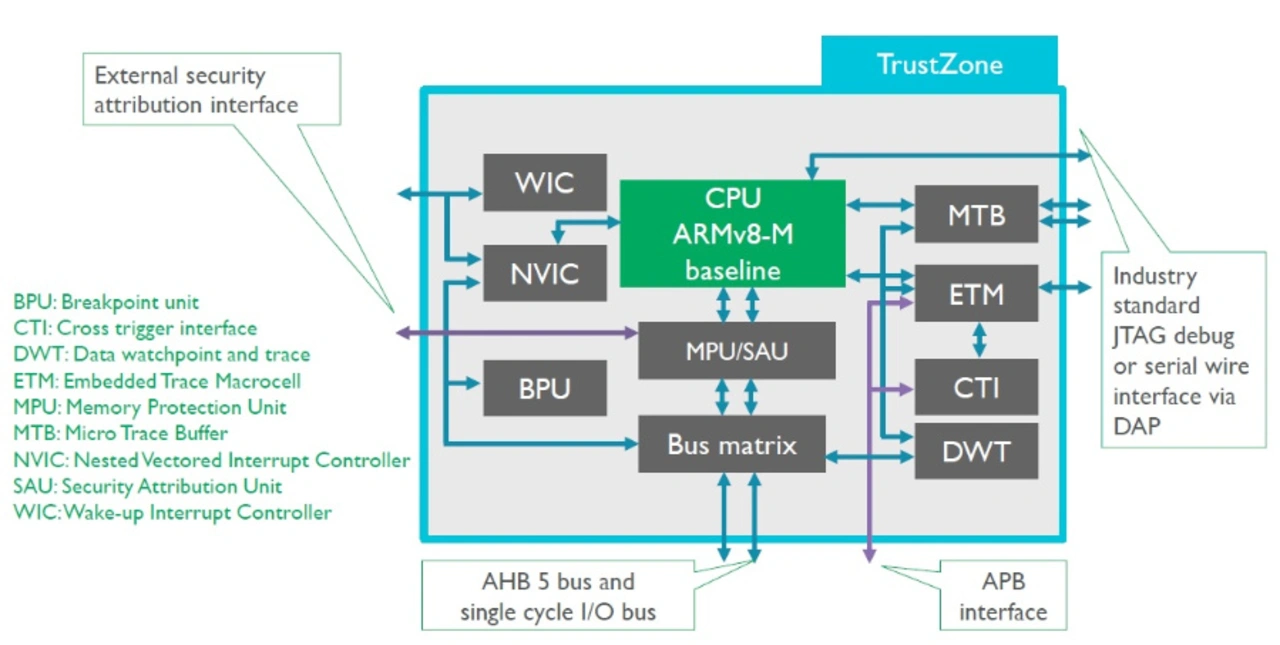

Bild 1 zeigt das Blockdiagramm des Cortex-M23. Alle Blöcke, die in grüner Schrift aufgezählt sind, können optional konfiguriert werden, dies beinhaltet auch die beiden MPUs (eine für sicheren und eine für unsicheren Zustand, siehe [1]) und auch die SAU. Dieser Security-Attribution-Einheit genannte Block definiert sichere und unsichere Speicherregionen in einer Auflösung von 32 Byte. Anders formuliert: Ob sich die CPU im sicheren oder unsicheren Zustand befindet, definiert sich ausschließlich über die zugegriffene Speicheradresse und deren Zustandsdefinition über die SAU. Ein MCU-Hersteller hat neben der softwaremäßig programmierbaren SAU auch hardwaremäßig auf Systemebene die Möglichkeit, bestimmte Adressraüme unüberschreibbar als sicher zu definieren – z.B. Verschlüsselungs-Peripherie oder bestimmte Bereiche des Flash-Speichers, in die er Firmware geladen hat.

Neu ist beim M23 gegenüber dem M0+, daß für das Debugging neben einem Micro-Trace-Puffer (MTB) auch eine Embedded Trace Macrocell (ETM), die man vom M3, M4 und M7 kennt, implementierbar ist. Während der MTB alle nicht-sequentiellen Anweisungen aufzeichnet (z.B. JMP, Interrupt, CALL) und damit im Fehlerfall der Programm-Fluss zu erkennen ist (der Vorteil für den Entwickler ist, daß er z.B. einen Breakpoint setzen kann und bei Erreichen des Breakpoints eine Trace-Aufzeichnung erhält, in der er genau verfolgen kann, welche Programmteile zuvor ausgeführt wurden, was z.B. hilfreich ist bei sporadischen Problemen, die durch fehlerhaften Code wie z.B. ein Befehls-Reihenfolge-Problem in Interrupt-Routinen verursacht werden), geht die ETM weiter.

Jobangebote+ passend zum Thema

Diese bzw. deren Weiterentwicklung Core-Sight unterstützt sowohl Programm- als auch Daten-Trace. CoreSight erlaubt zusätzlich das Tracen der Context-ID und ist zudem multicore-fähig. Zur Übertragung der Trace-Daten an den Debug-Host kommt ein relativ breitbandiger Trace-Port zum Einsatz, der in mehreren Modi mit unterschiedlichen Datenraten betrieben werden kann. Die zu übertragenden Trace-Daten werden vorher durch FIFO-Buffer serialisiert. Im Allgemeinen sieht das ETM-Konzept Komparatoren für Adressbereiche, Daten sowie den Zugriffsmodus (Lesen oder Schreiben) vor. Speziell für den Programm-Trace kann definiert werden, zu welchem Zeitpunkt in der Pipeline-Verarbeitung (Fetch oder Execute) ein Adresskomparator auf eine passende Adresse reagiert. Durch Verknüpfung der einzelnen Komparatoren können komplexere Trigger-Bedingungen zur Steuerung der Trace-Aufzeichnung definiert werden. Mit Hilfe von Zählern und eines Sequenzers zur Realisierung einer State-Machine mit maximal drei Zuständen lässt sich auch das sequenzielle Verhalten sehr gut rekonstruieren. Durch die Verfügbarkeit der ETM auch für die „kleinen“ ARMv8-M-CPUs hat der Entwickler nun (endlich möchte man sagen) die Möglichkeit eines einheitlichen Debuggings über alle CPUs.

Die sogenannte Cross-Trigger-Schnittstelle (CTI) ist nur bei Multicore-Implementierungen relevant. Mit ihr lassen sich z.B. im Fall eines Breakpoints alle CPUs gleichzeitig anhalten.

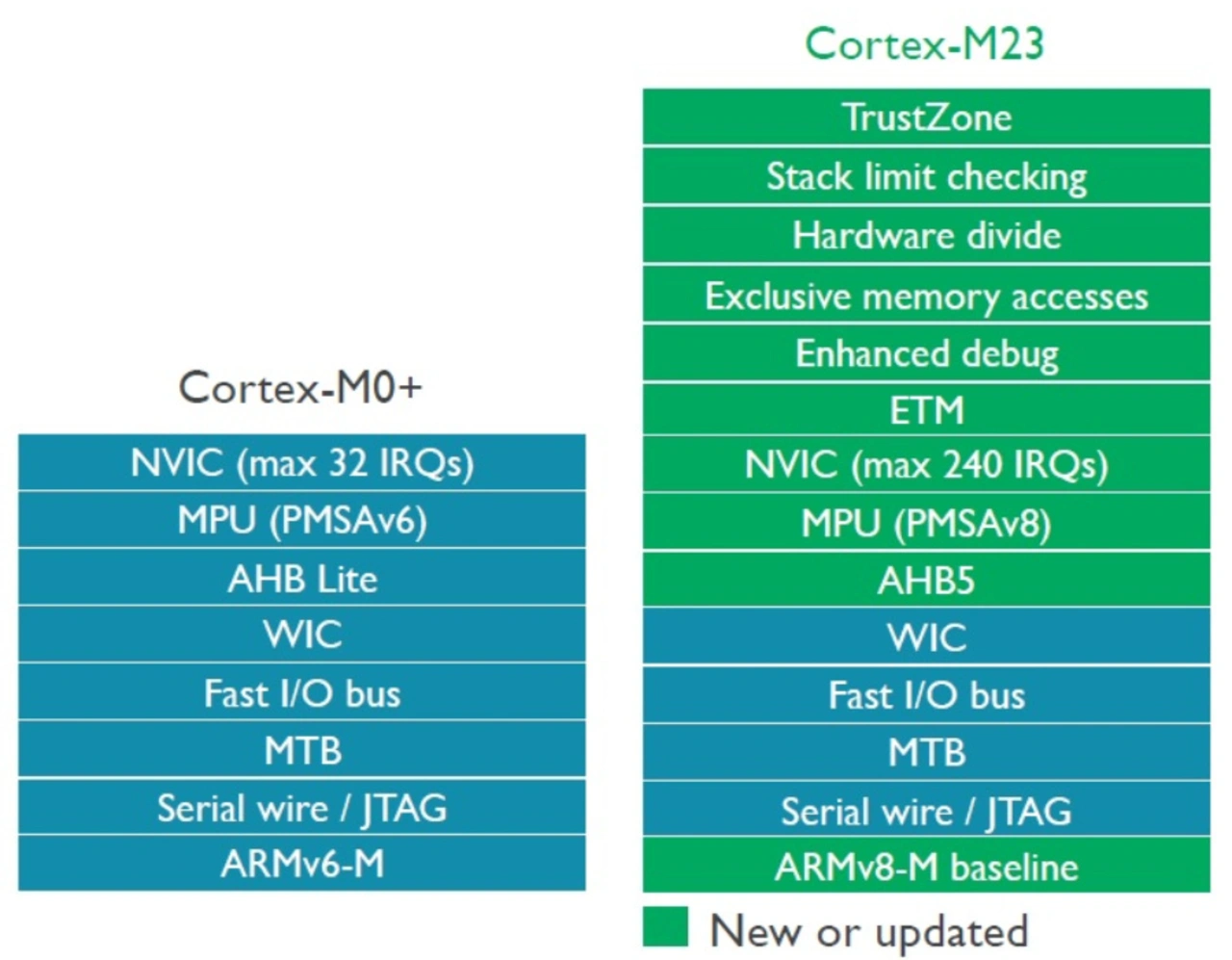

Bild 2 fasst alle Veränderungen/Verbesserungen des M23 gegenüber dem M0+ zusammen. Insbesondere durch den erweiterten Befehlssatz des Baseline-Profils ist die Rechenleistung allerdings sehr moderat gestiegen: Statt 2,46 Coremark/MHz stehen nunmehr 2,50 Coremark/MHz zu Buche.

- Cortex-M23 und –M33 sind erste ARMv8-M-CPUs

- Zahlreiche Konfigurationsoptionen

- Cortex-M33 mit neuer Pipeline

- Koprozessor-Schnittstelle entlastet AHB-5-Bus