Anwendungsbeispiel ARM-Cortex

MCU-Familie LPC1100 ersetzt 8- und 16-bit-Controller in Haushaltsgeräten

Fortsetzung des Artikels von Teil 1

Interrupt-Handling & Energieeffizienz und Systemkosten

Interrupt-Handling

Auf externe Ereignisse muss in Haushaltsgeräte-Applikationen in deterministischer Weise reagiert werden. Die Leistungsfähigkeit der Interrupt-Bearbeitung lässt sich durch die Angabe von "Latenz" und "Jitter" charakterisieren. Unter Latenz versteht man die Zeit zwischen dem Interrupt-Ereignis und dem Einsprung in die Interrupt-Verarbeitungs-Routine, während der Jitter als die Schwankungsbreite dieser Latenz definiert ist.

Im Cortex-M0 wurde die Latenz durch die enge Kopplung zwischen Interrupt-Controller und Core minimiert. Das Resultat ist eine konstante Latenz von 16 Zyklen für Interrupts der höchsten Prioritätsstufe. Der Interrupt-Controller unterstützt bis zu 32 verschiedene Interrupt-Quellen und umfasst auch einen nicht maskierbaren Interrupt-Eingang. Im LPC1100 finden sich spezielle Interrupt-Vektoren für alle möglichen Arten von Interrupt-Ereignissen. Damit wird jeder Interrupt automatisch und ohne Software-Aufwand an die jeweils richtige ISR (Interrupt Service Routine) verwiesen.

Zur Verringerung der Latenz bei verschachtelten Interrupts umgeht ein eingebauter Mechanismus die Notwendigkeit des Re-Stackings, wenn ein Interrupt höherer Priorität eintrifft, bevor mit der Verarbeitung der ISR für den vorigen Interrupt begonnen wurde. Zusätzlich wird das so genannte Tail-Chaining unterstützt. Es reduziert die Interrupt-Latenz durch Kombinieren der Exception-Austritts-Sequenz mit der darauf folgenden Exception-Eintritts-Sequenz, sodass ein direkter Einsprung in die ISR möglich ist.

Energieeffizienz und Systemkosten

In der Vergangenheit zählte die Energieeffizienz nicht zu den vorrangigen Anforderungen an Haushaltsgeräte, die schließlich meist für den Anschluss an das Stromnetz ausgelegt sind. Inzwischen aber bekommen die Energieeffizienz und die Standby-Leistungsaufnahme einen immer höheren Stellenwert.

Ungeachtet der hohen Verarbeitungsleistung des Cortex-M0 beträgt die durchschnittliche Stromaufnahme des LPC1100 lediglich ca. 150 µA/MHz. Da der M0-Core auf einer 32-bit-Architektur basiert, geht er außerdem effizienter mit der aufgenommenen Energie um als eine 8- oder 16-bit-Architektur. Bei gleicher Rechenleistung kann der LPC1100 um den Faktor 2 bis 4 langsamer getaktet werden als eine MCU auf 8- oder 16-bit-Basis, so dass die Leistungsaufnahme entsprechend geringer ist.

Bei abgeschaltetem Gerät profitieren auch die Stromspar-Betriebsarten wie der Deep-Sleep- oder der Deep-Power-Down-Modus von der hohen Verarbeitungsleistung des LPC1100, da der Baustein die anstehenden Aufgaben schneller ausführen und folglich länger in den stromsparenden Betriebsarten bleiben kann als typische 8- oder 16-bit-Architekturen. Bei der neuen LP-LPC1100-Serie wird eine entscheidende Senkung der Stromaufnahme im Deep-Sleep-Modus (2 µA) und im Deep-Power-Down-Modus (220 nA) zu verzeichnen sein.

Jobangebote+ passend zum Thema

Da das Marktsegment der weißen Ware stark von den Kosten diktiert wird, sollte ein Mikrocontroller außer Rechenleistung und Flexibilität auch einen konkurrenzfähigen Preis vorweisen können. Die Gesamtkosten eines Systems setzen sich aus mehreren Komponenten zusammen. In kleinen Systemen dominieren Core- und Speichergröße. Der Core des Cortex-M0 ist um den Faktor 3 kleiner als der des Cortex-M3. In kleinen Systemen mit einer begrenzten Zahl von Peripheriefunktionen und eingeschränkter Flash-Kapazität stellt dies einen entscheidenden Faktor für die Chipfläche insgesamt dar.

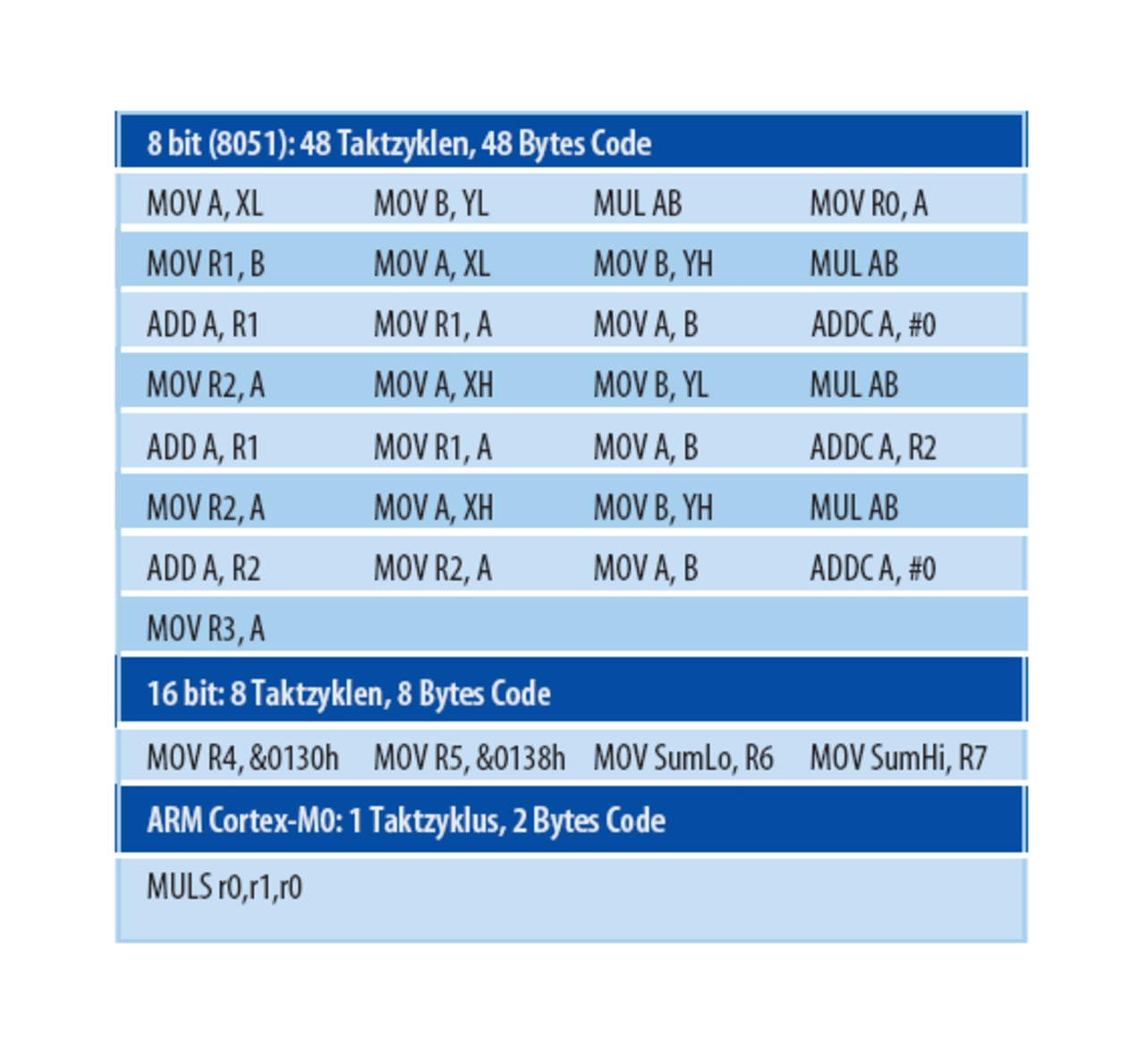

Ein weiterer Punkt für die Gesamt-Systemkosten ist die Größe des Flash-Speichers, der für den Applikations-Code benötigt wird. Da 32-bit-Befehle leistungsfähiger sein können als 8-bit-Befehle und deshalb mehrere 8-bit-Befehle ersetzen können (Tabelle), ist die Annahme gerechtfertigt, dass der Umfang des Applikations-Codes (mit Ausnahme der Konstantentabellen) weitgehend identisch ist:

Allerdings ergaben Tests, in denen 8-bit-Code auf den LPC1100 portiert wurde, dass der Applikations-Code sogar deutlich kleiner werden kann (manchmal 50 Prozent oder weniger). Hausgeräte-Applikationen können hiervon in vollem Umfang profitieren, da sich der Flash-Speicher kleiner dimensionieren lässt und die Kosten reduziert werden können.

- MCU-Familie LPC1100 ersetzt 8- und 16-bit-Controller in Haushaltsgeräten

- Interrupt-Handling & Energieeffizienz und Systemkosten

- Spezielle Peripherie