Verifikation von Energiespar-IC-Entwürfen

Fortsetzung des Artikels von Teil 5

CPF im Einsatz

Der als Beispiel dienende Schaltungsentwurf für die CPF-Simulationen hat die folgenden Energiespar-Funktionen:

- Der Großteil des SoC wird im Bereitschaftsbetrieb deaktiviert – mit Ausnahme des Timer-Moduls und des auf dem Chip integrierten RAMs.

- Ein Leistungsmanagement-Block überwacht die Versorgung und teilt dem Regler/Schalter-Block mit, wenn die Versorgungsspannung deaktiviert wird.

- Der Bereitschafts-Regler vergleicht diese Spannung mit der Batteriespannung und steuert die Umschaltung zwischen Netzteil und Batterie.

- Der Timer-Block wird niemals deaktiviert, und das integrierte RAM wird dazu verwendet, für den Prozessor kritische Daten zu erhalten.

Jobangebote+ passend zum Thema

Die Aufgabe des Verifikationsingenieurs besteht nun darin, während einer wiederholten Aktivierung und Deaktivierung des Energiespar-Modus (Batteriebetrieb) die normale Funktion der Timer und die Erhaltung der RAM-Inhalte zu überprüfen.

Die CPF-Datei für diesen IC-Entwurf beinhaltet die Steuerinformationen für die Schaltung der Versorgungsspannung und die Informationen über die Blöcke, die im Energiespar-Betrieb abgeschaltet werden sollen. Da die Isolations-und Erhaltungslogik bereits vom Entwicklerteam in das SoC eingearbeitet wurde, enthält die CPF-Datei diese Informationen nicht mehr.

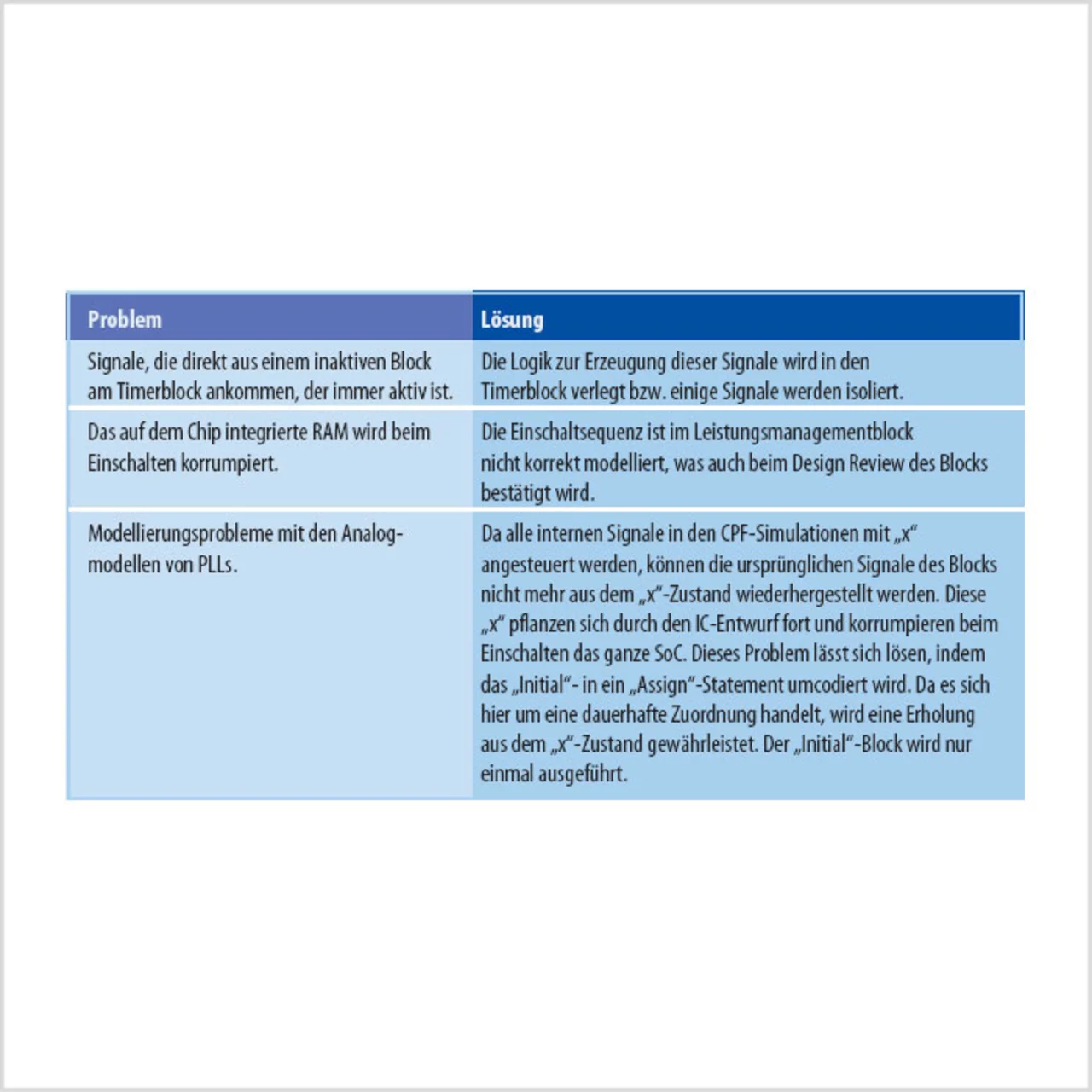

Die Tests für das Timer-Modul und das RAM werden mit CPF durchgeführt. Die Verifikationsinfrastruktur wird – abgesehen von wenigen zusätzlichen Bedingungen zur Prüfung von Isolation, Datenerhaltung und Leistungs-Sequenzen – nicht geändert. Tabelle 1 enthält die ziemlich kritischen Fehler, die sich mit der CPF-basierten Energiespar-Verifikation aufspüren lassen.

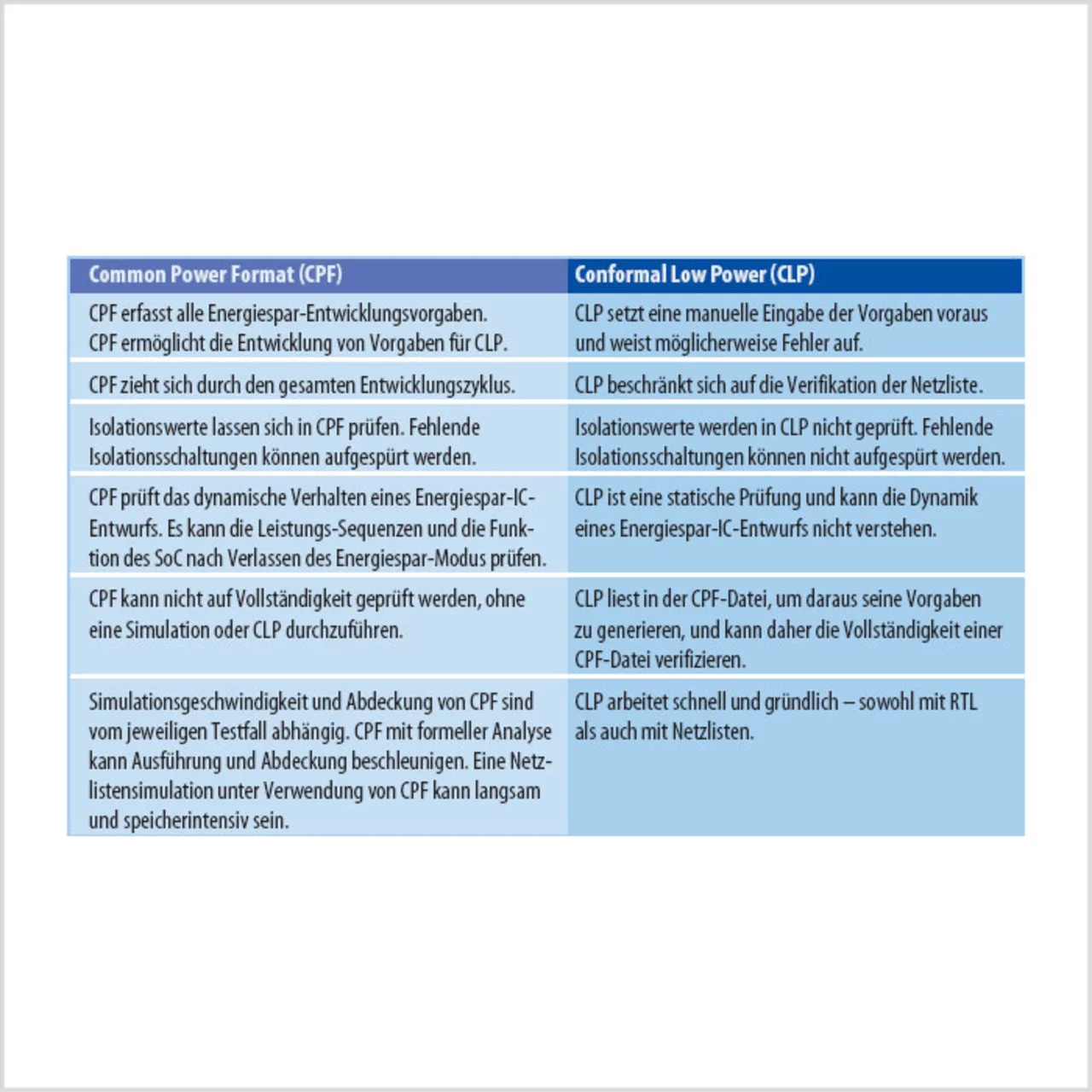

CLP (Conformal Low Power) ist ein leistungsfähiges Werkzeug, mit dem man eine SoC-Netzliste mit angeschlossener Leistungsversorgung statisch prüfen kann. So lässt sich verifizieren, ob die Leistungsvorgaben in der Netzliste denen der „Constraint“-Datei entsprechen und ob in der Netzliste Versorgungsspannungszonen mit entsprechenden Pegelumsetzern und Isolationszellen sauber voneinander getrennt sind. Leider aber unterliegt dieses Werkzeug gewissen Einschränkungen, die man mit CPF in den Griff bekommen kann. Die Unterschiede zwischen beiden sind in Tabelle 2 zusammengefasst.

Die in Tabelle 2 aufgelisteten Argumente zeigen, dass IC-Entwickler weder ohne das Eine noch das Andere auskommen. Daher ist es notwendig, dass sowohl CPF als auch CLP Bestandteil des Entwicklungszyklus sind, um eine vollständige Verifikation von Energiespar-IC-Entwürfen zu gewährleisten.

- Verifikation von Energiespar-IC-Entwürfen

- Elemente eines Energiespar-IC-Entwurfs

- Verifikation von Energiespar-IC-Entwürfen

- Verifikation von Energiespar-IC-Entwürfen

- Herkömmliche Verifikation

- CPF im Einsatz

- Grenzen von CPF-Simulationen

- Mikroprozessoren sind Energiesparweltmeister