Verifikation von Energiespar-IC-Entwürfen

Fortsetzung des Artikels von Teil 6

Grenzen von CPF-Simulationen

CPF als Sprache unterstützt eine Vielzahl von Energiespar-Konstrukten, aber die Unterstützung von CPF stößt im Simulator an einige Grenzen:

Prüfungen, ob die Versorgungsspannung angeschlossen ist, können mit CPF nicht durchgeführt werden. Da in CPF nur Schaltvorgänge auf Blockebene berücksichtigt werden, kann die Gesamtversorgung des IC-Entwurfs nicht verifiziert werden.

Auch Pegelumsetzer lassen sich mit CPF nicht prüfen. Dieser Test hängt von der Versorgungsspannung ab und kann daher auch nicht durchgeführt werden.

Jobangebote+ passend zum Thema

CPF und CLP ergänzen sich

Für IC-Entwürfe, die sich bei Strukturbreiten im Submikronbereich bewegen, werden neue Energiespar-Entwurfsmethoden entwickelt. Die Verifikation dieser Methoden ist ein wichtiger Punkt, der sich nicht ignorieren lässt. Herkömmliche Konzepte erweisen sich als mühsam und erfassen möglicherweise unter Leistungsaspekten nicht alle kritischen Szenarien. CPF-gestützte Simulationen – dynamisch oder statisch – stellen ein hervorragendes Werkzeug dar, wenn es gilt, diese Energiespar-Methoden zu verifizieren. Mit CPF sind IC-Entwickler in der Lage, Fehler schon früh im Entwicklungszyklus aufzuspüren, ohne dass größere Modifikationen der Testinfrastruktur erforderlich wären. Der Verifikationsingenieur kann sich so mehr auf seine eigentlichen Aufgaben konzentrieren, anstatt sich um die Modellierung des Energiespar-Schaltverhaltens auf der Testbench zu kümmern. CLP erlaubt eine statische Prüfung der Energiespar-Vorgaben eines IC-Entwurfs, während CPF diese dynamisch prüft. Das heißt aber nicht, dass CLP durch CPF überflüssig wird. Der IC-Entwickler benötigt beide, wenn er ein SoC umfassend auf die Energiespar-Ziele hin verifizieren möchte. hs

Autor: | |

| Prashant Bhargava |

Multiplikator Mikroprozessor

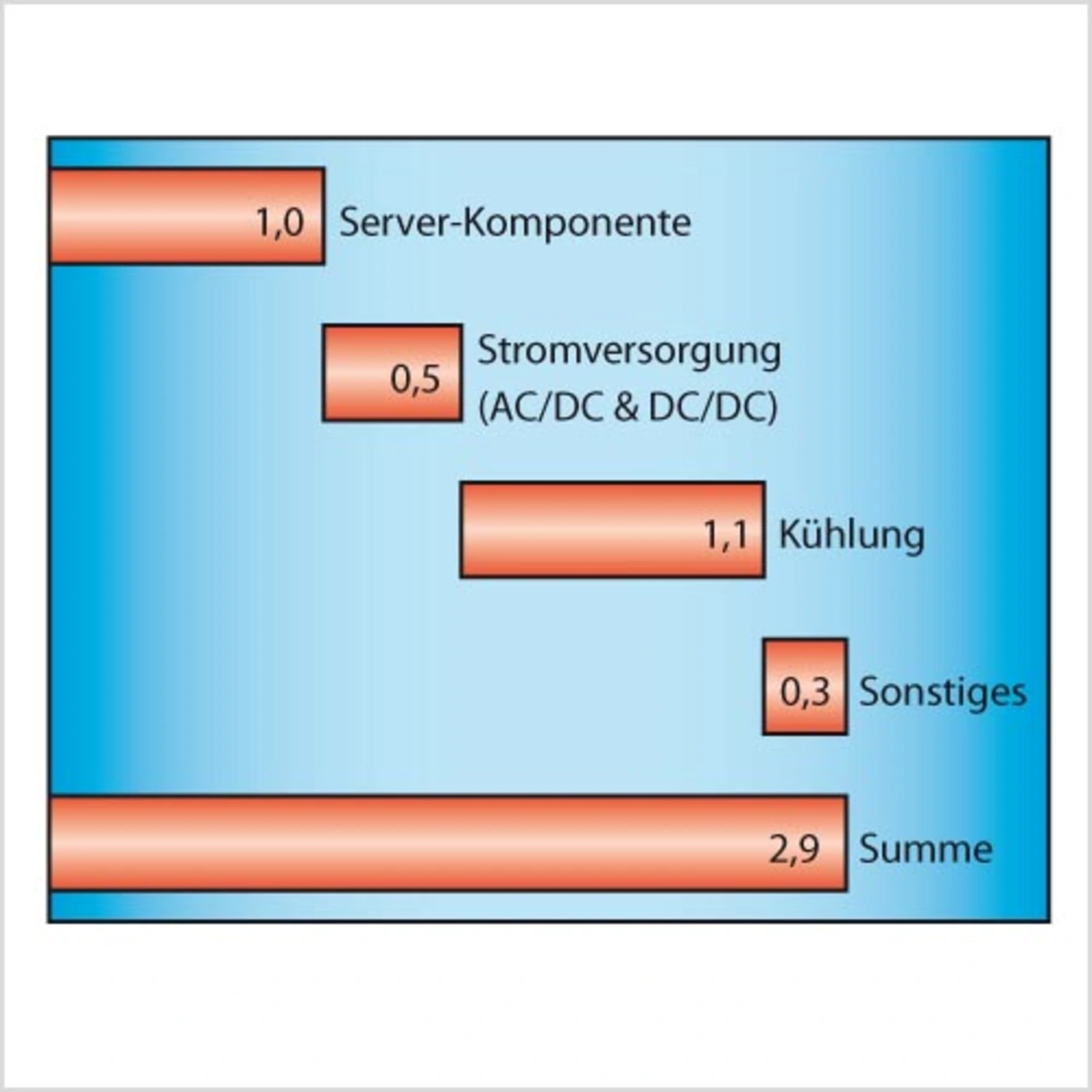

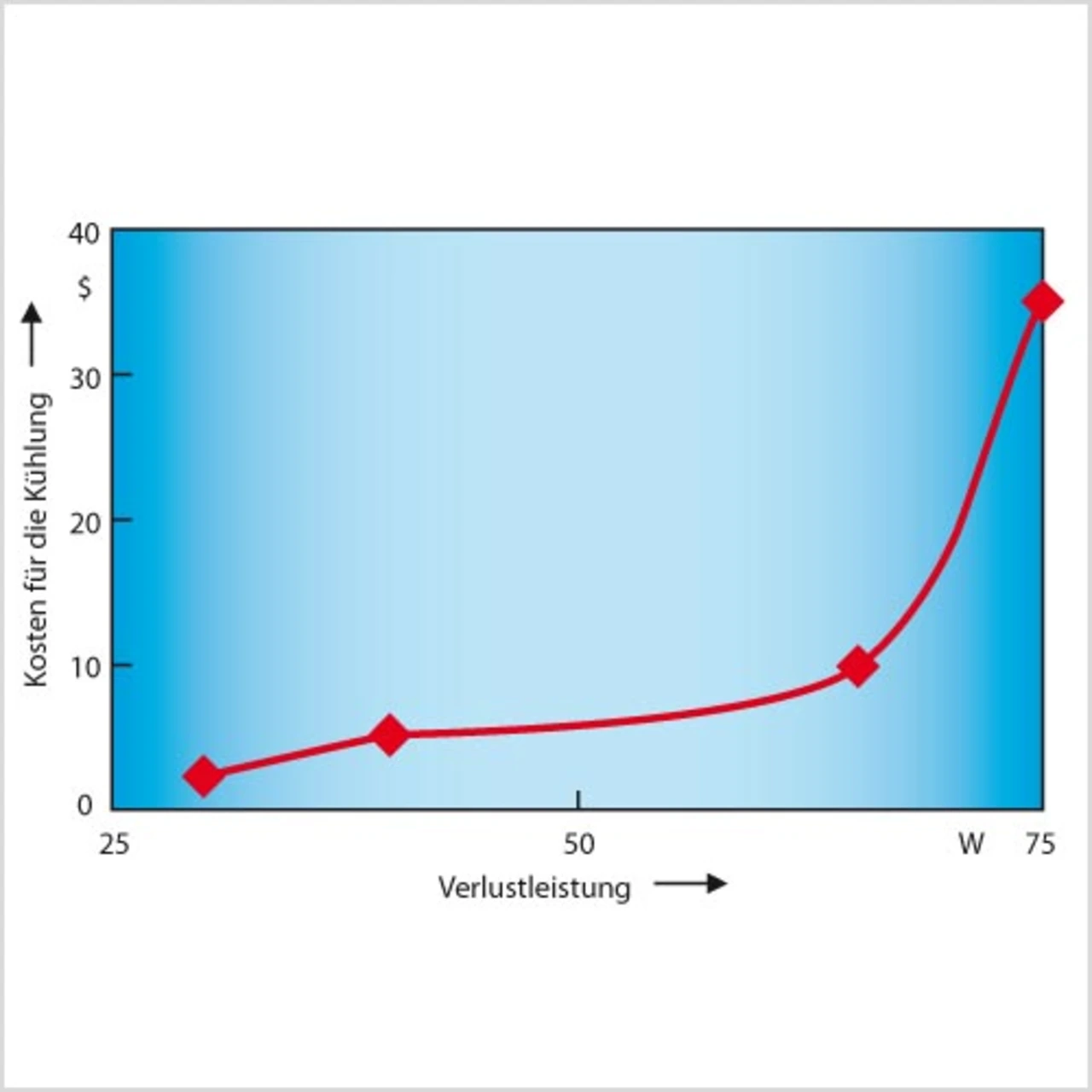

Mikroprozessoren dürfen nicht isoliert betrachtet werden. Damit sie ihre Funktionen ausüben können, sind sie auf periphere Bauteile und eine sie umgebende Infrastruktur angewiesen, die ebenfalls Energie aufnehmen. Bei Servern in Rechenzentren ist der Leistungsanteil für die Infrastruktur sogar fast doppelt so hoch wie für den eigentlichen Rechner. Mit der steigenden Verlustleistung der Prozessoren steigt auch der Aufwand für die Kühlung – jedoch exponentiell.

- Verifikation von Energiespar-IC-Entwürfen

- Elemente eines Energiespar-IC-Entwurfs

- Verifikation von Energiespar-IC-Entwürfen

- Verifikation von Energiespar-IC-Entwürfen

- Herkömmliche Verifikation

- CPF im Einsatz

- Grenzen von CPF-Simulationen

- Mikroprozessoren sind Energiesparweltmeister