Verifikation von Energiespar-IC-Entwürfen

Fortsetzung des Artikels von Teil 4

Herkömmliche Verifikation

Um die Energiespar-Logik auf herkömmliche Art und Weise – ohne CPF – zu verifizieren, müssten die Elemente der Testbench das Energiespar-Verhalten vortäuschen. In den meisten IC-Entwürfen werden so genannte „Wrapper“ für Isolation und Datenerhaltung vom Entwicklerteam eingefügt. Um seine Simulationen durchzuführen, muss der Verifikationsingenieur alle Register auflisten, die erhalten, und alle Signale, die isoliert werden müssen. Die Logik der Testbench müsste diese Register im Energiespar-Betrieb erhalten und beim Einschalten die entsprechenden Werte wieder herstellen. Im Aus-Zustand müssen alle Knoten innerhalb der deaktivierten Zonen auf „x“ gesteuert werden. Nun, man kann sich vorstellen, welche Art von Infrastruktur entwickelt werden müsste, um solche Simulationen bewältigen zu können. Ist die Schaltung umfangreich, so wird diese Aufgabe zum Alptraum.

Jobangebote+ passend zum Thema

Selbst wenn Simulationen auf Gatterebene alle für Isolation und Datenerhaltung benötigten Zellen in der Netzliste enthielten, würde immer noch vorausgesetzt, dass die Testbench das Verhalten beim Abschalten der Versorgungsspannung modellieren und alle deaktivierten Knoten mit „x“ ansteuern müsste. Circuit-Level-Simulationen können zwar Schaltvorgänge der Versorgungsspannung modellieren, wie Gate-Level-Simulationen sind sie aber erst spät im Entwicklungsprozess angesiedelt. Alle jetzt gefundenen Fehler (ECO) werden gerade noch vor dem Einrichten der Fertigungsbänder entdeckt. Die Korrekturdurchläufe führen dann zwangsweise zu Verzögerungen. IC-Hersteller können es sich nicht leisten, ein solches Risiko mit möglicherweise kostspieligen Folgen einzugehen.

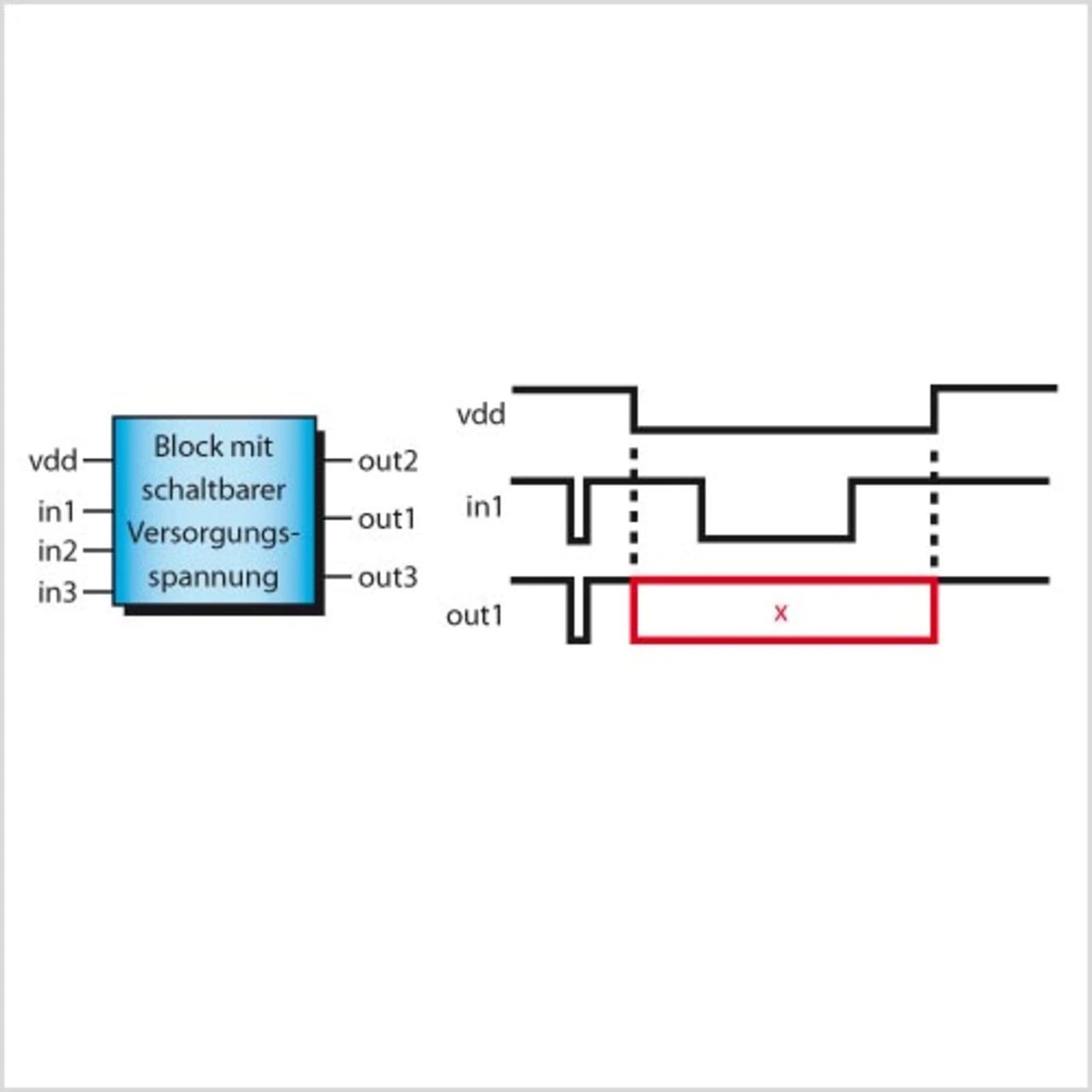

Mit dem CPF-basierten Konzept lassen sich die Nachteile der traditionellen Verifikation beseitigen, und man ist für eine leistungsbezogene Verifikation nicht mehr auf eine fertige Netzliste angewiesen. Für CPF-fähige Simulationen werden keine zusätzlichen Testaufbauten oder Entwurfsänderungen benötigt. Der Simulator liest in der CPF-Datei und simuliert den RTLCode so, als ob eine Isolation oder Zellen zur Datenerhaltung wirklich präsent wären. Selbst die internen Signale und Ausgangsstufen von deaktivierten Zonen werden automatisch auf „x“ gesteuert.

Nach dem Einschalten sollte die Schaltung in der Lage sein, aus diesem „x“-Zustand zurückzukommen (Bild 6). Der Verifikationsingenieur wird dadurch entlastet, und er kann sich darauf konzentrieren, die wirklichen Probleme seines Schaltungsentwurfs in den Griff zu bekommen, anstatt an einer Infrastruktur für die Verifikation zu basteln, wie das in der Vergangenheit erforderlich war.

Wird ein Problem entdeckt – beispielsweise eine fehlende Isolation –, dann muss der Verifikationsingenieur nicht auf eine Überarbeitung warten, er kann einfach die Isolationsvorgabe in CPF eingeben und weiterarbeiten.

Ein weiterer Vorteil von CPF liegt darin, dass es von Software-Werkzeugen zur formellen Analyse gelesen werden kann. Der gleiche Verifikationssatz kann für die formelle Analyse ebenso eingesetzt werden wie für die dynamische Verifikation, aber nun sehr viel schneller und gründlicher.

- Verifikation von Energiespar-IC-Entwürfen

- Elemente eines Energiespar-IC-Entwurfs

- Verifikation von Energiespar-IC-Entwürfen

- Verifikation von Energiespar-IC-Entwürfen

- Herkömmliche Verifikation

- CPF im Einsatz

- Grenzen von CPF-Simulationen

- Mikroprozessoren sind Energiesparweltmeister