Verifikation von Energiespar-IC-Entwürfen

Fortsetzung des Artikels von Teil 1

Elemente eines Energiespar-IC-Entwurfs

Und genau hier rettet den IC-Entwickler CPF. Mit CPF können die dynamische Natur von Einschalt- und Ausschalt-Sequenzen ebenso wie die Isolation auf RTL-Ebene verifiziert werden, und die dabei gefundenen Fehler lassen sich relativ einfach beheben.

Jeder Energiespar-IC-Entwurf basiert auf den folgenden Funktionen, und der Entwickler muss verifizieren, dass diese korrekt arbeiten und die Funktion der restlichen Schaltung nicht beeinträchtigen.

Jobangebote+ passend zum Thema

Isolation

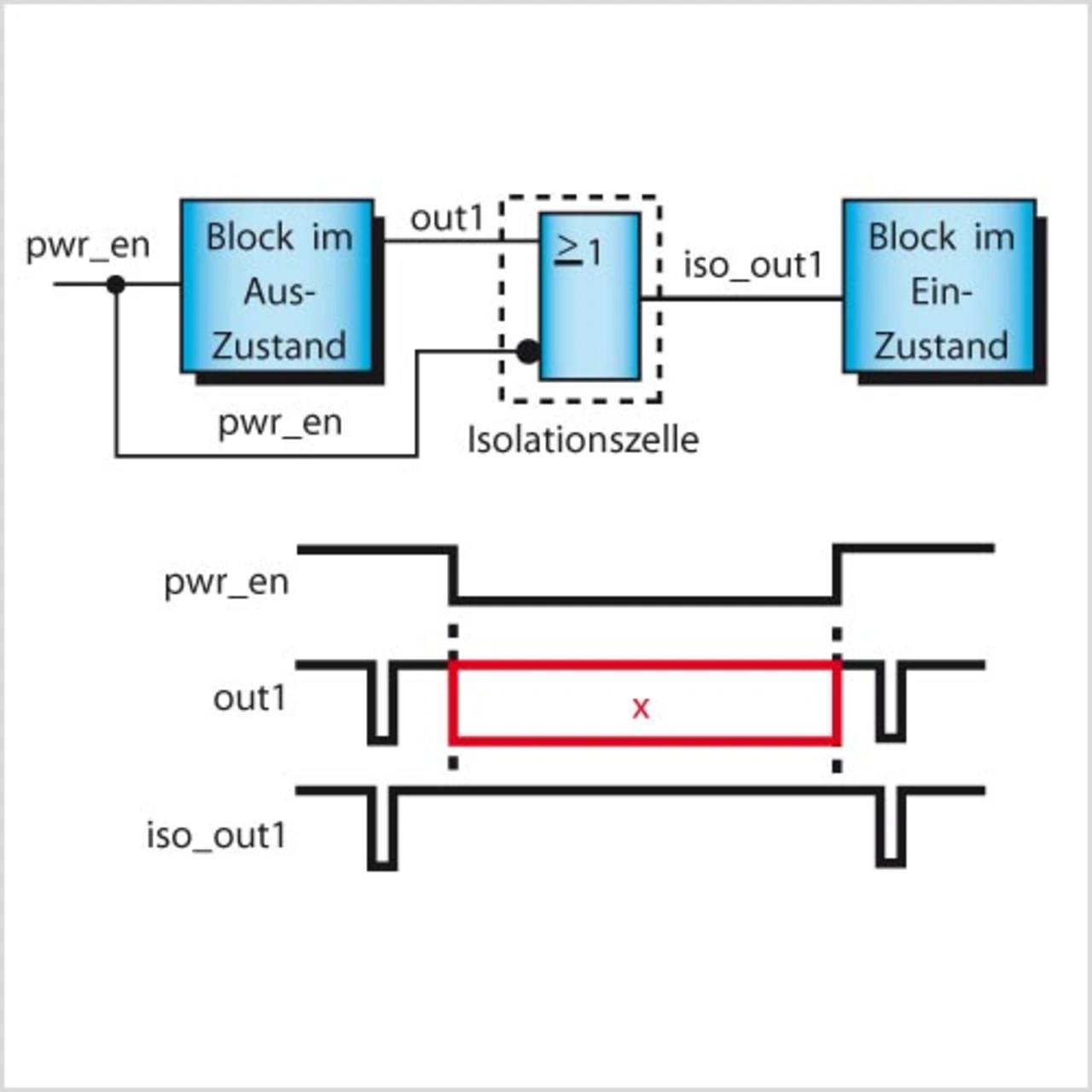

Unter dem Begriff „Isolation“ versteht man, dass die Werte eines von einem inaktiven Block stammenden Signals beim Auftreffen auf einen aktiven Block einen vordefinierten Pegel aufweisen, damit die Funktion des aktiven Blocks nicht beeinträchtigt wird (Bild 2).

Um dies zu gewährleisten, stehen drei Arten von Isolation zur Verfügung:

- High Isolation – hier wird das Signal auf einen High-Pegel (logisch 1) isoliert.

- Low Isolation – das Signal wird auf einen Low-Pegel (logisch 0) isoliert.

- Hold Isolation – hier wird der Signalpegel erhalten, der vor dem Eintritt in den Energiespar-Modus angelegen hat.

Ein Verifikationsingenieur sollte sicherstellen, dass die zur Isolation eingesetzten Zellen nicht an der abschaltbaren Versorgungsspannung hängen, da sie sonst ihren Zweck nicht erfüllen können.

- Verifikation von Energiespar-IC-Entwürfen

- Elemente eines Energiespar-IC-Entwurfs

- Verifikation von Energiespar-IC-Entwürfen

- Verifikation von Energiespar-IC-Entwürfen

- Herkömmliche Verifikation

- CPF im Einsatz

- Grenzen von CPF-Simulationen

- Mikroprozessoren sind Energiesparweltmeister