Sparsame Systeme mit FPGAs entwerfen

Fortsetzung des Artikels von Teil 3

Sparsame Systeme mit FPGAs entwerfen

Dieser Betriebszustand eliminiert demnach den dynamischen Energieverbrauch, der statische ist vernachlässigbar. Dieses Verfahren findet seit einiger Zeit Verwendung in ASICs und hat seit kurzem auch Einzug in FPGAs gehalten. Actels »Flash-Freeze«-Modus ist ein Beispiel dafür. In dieser Betriebsart lässt sich zum Beispiel bei »IGLOO nano«-FPGAs die Leistungsaufnahme auf 2 μW senken. Darüber hinaus können Entwickler den Flash-Freeze-Pin nutzen, um schnell in diese Betriebsart zu gelangen oder diese zu verlassen. Ein Mobiltelefon ist ein typisches Beispiel für ein System, das die Vorteile mehrerer Energiespar-Betriebsarten nutzt. So ist ein Mobiltelefon nur dann aktiv, wenn es gerade benutzt wird. Andernfalls befindet es sich im Standby, um die Batterie zu schonen.

Jobangebote+ passend zum Thema

Mehrere Versorgungsmodi nutzen

Beim »Selective Power-down« wird die Stromversorgung einiger Chipbereiche oder bestimmter ICs auf dem Board abgeschaltet. Dazu kommt eine Multi-Supply-Strategie zum Einsatz, bei der die Versorgungsnetze einiger Blöcke von anderen Versorgungsleitungen getrennt sind, um ein selektives Abschalten (Selective Power-down) zu ermöglichen. Power-downoder Sleep-Modi lassen sich auch in die FPGA-Architektur einbinden, um gerade nicht benutzte Funktionsblöcke abzuschalten.

Auch mit »Macro Optimization« lässt sich Energie sparen. Einige FPGAs werden in Versionen angeboten, die auf hohe Performance, hohe Logikdichte oder einen geringen Energieverbrauch optimiert sind. High-Performance-Makros tendieren dazu, mehr Energie zu verbrauchen als andere Versionen. Energie lässt sich sparen, wenn High-Performance-Makros nur dort Verwendung finden, wo sie unbedingt erforderlich sind. Zum Beispiel verbraucht ein schneller Addierer mehr Energie als ein langsamerer »Ripple«-Addierer. So kann zum Beispiel der Ripple-Carry-Addierer im dynamischen Betrieb nur etwa ein Zehntel der Energie des schnellen Addierers verbrauchen. Je nach Geschwindigkeit, die bei einem Design und für die Zielfunktionen erforderlich ist, kann die Low-Power-Option optimal geeignet sein. Dies trifft für fast alle Makrotypen einschließlich Multiplizierer, FIFOs und RAMs zu.

»Time Multiplexing« und »Minimum I/O Count Design«-Partitionierung sind Techniken, die helfen können, eine I/O-Bank ein- oder auszuschalten. Ebenfalls hilfreich ist es, die Zahl der verschiedenen verwendeten I/O-Verfahren zu minimieren und darüber hinaus sicherzustellen, dass die richtige Methode zum Einsatz kommt und die I/O-Treiberströme sowie die Slew-Rates reduziert werden.

Auch »Dynamic Voltage Scaling« spart Energie. Da die Energie proportional zum Quadrat der Spannung ist, lässt sich durch Reduzieren der Versorgungsspannung die Leistungseffizienz beachtlich verändern. Falls in einem System mehr Performance erforderlich ist, als Low-Voltage-I/Os liefern können, besteht eine ausgezeichnete Alternative darin, Low-Voltage-I/Os an nicht Performance-kritischen Pins und Higher-Voltage-I/Os für kritische Signale zu verwenden. Einige Low-Power-FPGAs, die heute angeboten werden, arbeiten komplett – Core und I/Os – an einer einzigen Spannung von 1,2 V.

Heute helfen zahlreiche Power-orientierte FPGA-Designtools bei der schnellen Realisierung energieeffizienterer Produkte. Zwei häufig anzutreffende Methoden sind Power-driven Layout und Power-Analyse. Ersteres lässt sich verwenden, um den Energieverbrauch im dynamischen Betrieb zu minimieren. Power-driven Layout-Werkzeuge untersuchen das Netz aus programmierbaren Verbindungsleitungen (Interconnects) zwischen Funktionsinstanzen und konzentrieren sich für eine Optimierung auf die Netze mit großen »Activity-Capacitance«-Produkten (f x C). Diese Tools untersuchen auch die Zahl an Zeilen- und »Spine«-Ressourcen für Taktnetze, weil diese Netze meist zu den größten und aktivsten gehören.

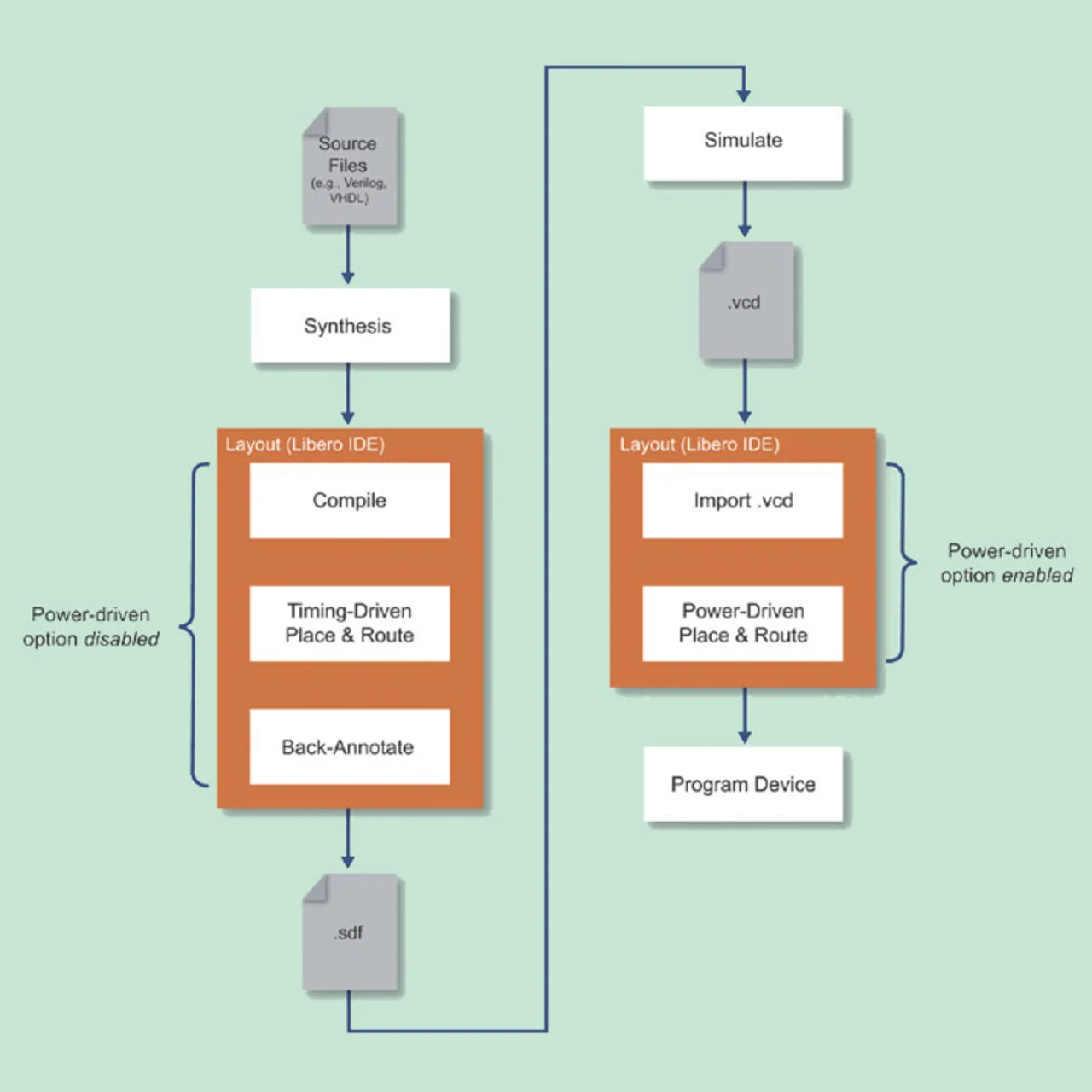

Typischerweise liefert ein aus der Post-Layout-Simulation gewonnenes und als Quelldatei für das Power-driven Layout verwendetes VCD-File (Value Change Dump) gegenüber einer standardmäßigen, allgemeinen Power-Abschätzung eine genauere Analyse, da es Informationen über die tatsächliche Schaltaktivität zwischen Netzen innerhalb des Designs liefert. Um dies zu bewerkstelligen, würde man zuerst das Layout des Designs in einem Timingdriven-Modus durchführen und dann zurückverweisen.

Anschließend würde man die Simulation durchführen, um das VCD-File zu generieren, diese Datei in das Projekt importieren und sich das Layout erneut im Power-driven Modus vornehmen (Bild 2).

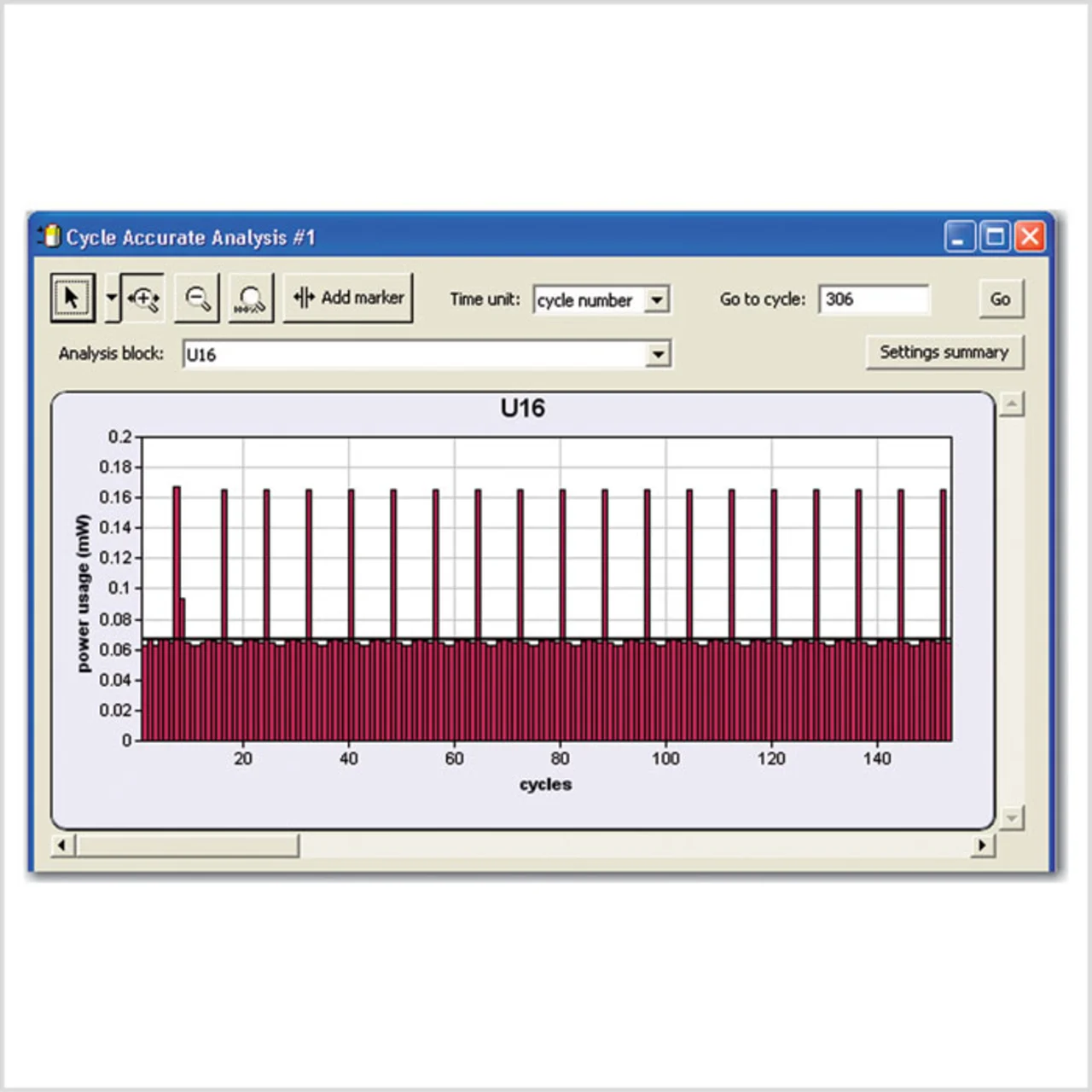

Werkzeuge zur Leistungsanalyse untersuchen und optimieren die Hierarchie eines Designs im Hinblick auf den Energieverbrauch. Solche Tools analysieren alle Subkomponenten innerhalb einer Designhierarchie und zeigen den Energieverbrauch an. Durch eine sorgfältige Untersuchung dieser Informationen und entsprechende Änderungen am Design lassen sich beachtliche Energieeinsparungen erzielen. Auf der obersten Ebene (Top Level) oder innerhalb der selektierten Instanzen wird die jeweilige Leistungsaufnahme der Netze, Gatter, Speicher, I/Os, Taktbereiche oder bezogen auf die Versorgungsspannung angezeigt (Bild 3). Auf diese Art lassen sich die Brennpunkte eines Designs erkennen, damit Entwickler entsprechende Maßnahmen zur Verringerung des Energieverbrauchs ergreifen können. (mc)

Fred Wickersham

ist Product Marketing Manager Software Tools bei

Actel

Telefon 08 16 59/58 40

www.actel.com

Siehe auch:

Reine Nervensache – Timingabschluss beim FPGA-Design

FPGA-Systeme architekturneutral entwerfen

- Sparsame Systeme mit FPGAs entwerfen

- Sparsame Systeme mit FPGAs entwerfen

- Sparsame Systeme mit FPGAs entwerfen

- Sparsame Systeme mit FPGAs entwerfen

- 5