Sparsame Systeme mit FPGAs entwerfen

Fortsetzung des Artikels von Teil 1

Sparsame Systeme mit FPGAs entwerfen

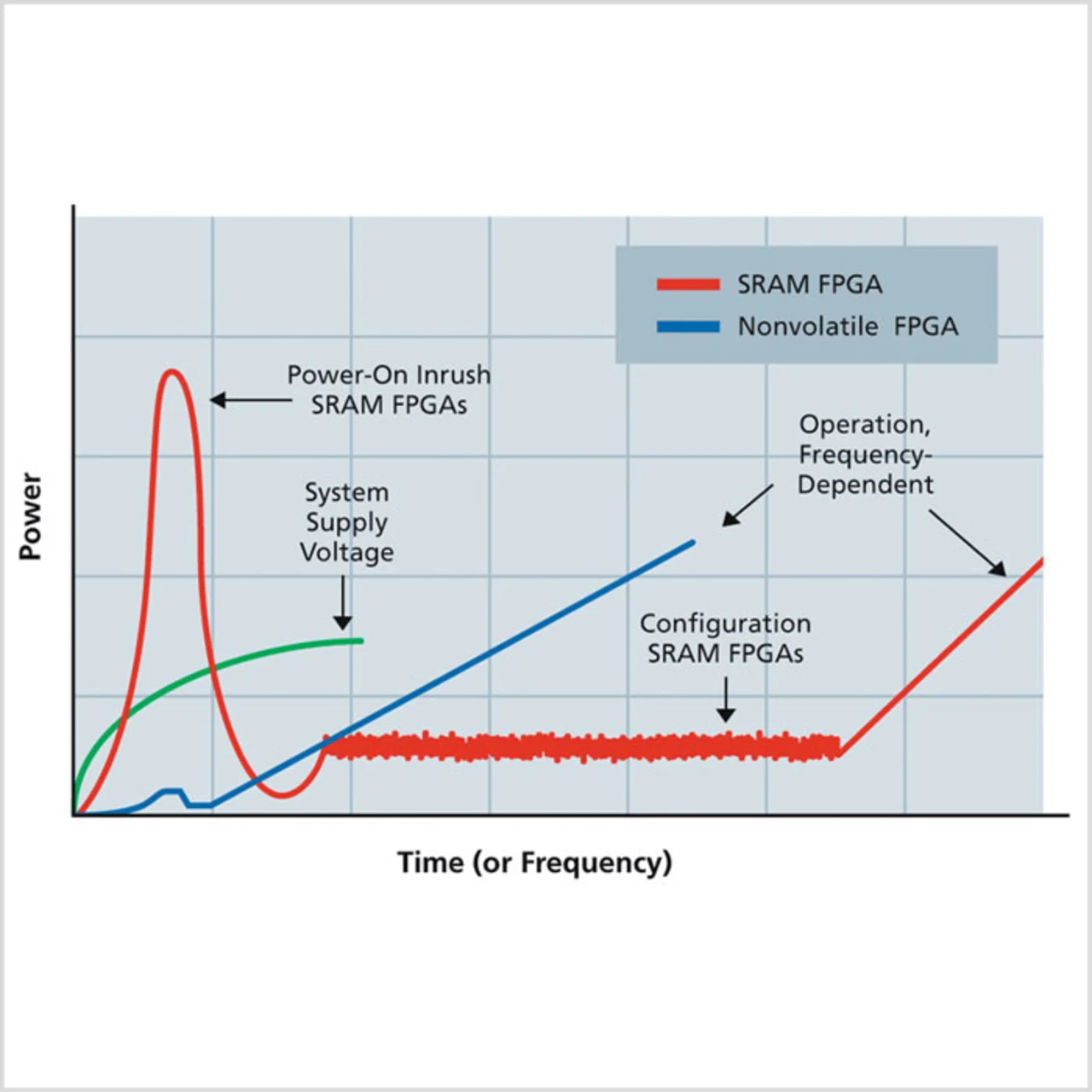

Entwickler, die flüchtige, SRAM-basierte FPGA-Lösungen einsetzen, müssen drei weitere Stromkomponenten berücksichtigen. Einschaltstrom (Inrush Current), Stromaufnahme bei der Konfiguration (Configuration Current) und Stromaufnahme im Sleep-Mode (statisch). SRAM-FPGAs müssen wegen ihres flüchtigen Verhaltens bei jedem Einschalten neu konfiguriert werden. Die dazu erforderlichen Daten befinden sich meist in einem externen PROM, das zusätzlichen Strom benötigt und außerdem den Einschaltvorgang eines Systems verzögert.

Jobangebote+ passend zum Thema

Die Auswirkungen machen sich bei Systemen, die häufig ein- und ausgeschaltet werden, besonders bemerkbar. Dies muss bei der Abschätzung der Batterielaufzeit berücksichtigt werden. So müssen Systementwickler bei der Dimensionierung der Stromversorgung oder bei der Auswahl der Batterie für SRAM-basierte, programmierbare Bausteine sowohl den Konfigurations- wie auch den Einschaltstrom des FPGAs berücksichtigen. Echte Flash-FPGAs sind nicht flüchtig, benötigen keine Einschalt- und Konfigurationsströme und verbrauchen im statischen Betrieb weniger Energie als SRAM-FPGAs. Diese Eigenschaften vereinfachen die Entwicklung und ermöglichen Systeme mit geringerem Energieverbrauch (Bild 1).

Eine andere Maßnahme, die FPGAHersteller wählen, um die Transistor-Leckströme zu minimieren beziehungsweise zu vermeiden, besteht in der Entwicklung von Zellen mit zwei Schwellspannungen (VT). Bei dieser Multi-VT-Technik möchte man den Leckstrom des gesamten Designs reduzieren, indem man die Zahl der »Low«-VT-Zellen mit höheren Leckströmen auf ein Minimum begrenzt und gleichzeitig die Anzahl an »High«-VT-Zellen mit geringen Leckströmen maximiert. Jene Technik kam in der Vergangenheit schon in ASICs und ASSPs zum Einsatz, inzwischen nutzen sie auch FPGA-Hersteller.

Kleinere Dice

In der Welt des IC-Designs steht die Minimierung der Die-Fläche aus Kosten- und anderen Gründen ständig im Mittelpunkt. Heute kann die Liste der Entwicklungsanforderungen um das Thema »Energieverbrauch« erweitert werden. Denn je kleiner ein Die ist, desto kleiner ist der Energieverbrauch im statischen Betrieb. Durch die Auswahl des kleinstmöglichen Dies, der die Funktionen und andere Anforderungen einer Applikation erfüllt, lassen sich die Entwicklungsziele hinsichtlich des Energieverbrauchs einfacher erfüllen.

Wichtig ist auch, dass ein FPGA gewählt wird, mit dem sich Ressourcen wie RAMs, PLLs und I/O-Technologien optimal nutzen lassen. Außerdem ist zu berücksichtigen, ob Low-Power-Betriebsarten des FPGAs und andere Möglichkeiten zur Energieeinsparung bei dynamischen Ressourcen wie PLLs, RC-Oszillatoren und I/O-Bänken vorhanden sind. Berücksichtigt man zum Beispiel, dass sich mit niedrigeren Referenzspannungen über die Lebensdauer eines Systems Energie einsparen lässt, ergeben sich durch die Wahl von FPGAs mit I/Os, die 1-V-, 2-V- und/oder 1,5-V-LVCMOS-Standards unterstützen, Vorteile.

Die Energie, welche ein FPGA im dynamischen Betrieb verbraucht, ergibt sich zum Großteil aus den Lade- und Entladevorgängen kapazitiver Elemente wie Logik-Ressourcen und dem Netzwerk aus programmierbaren Verbindungsleitungen (Interconnects). Der dynamische Energieverbrauch eines Ressource-Elements i lässt sich aus der Gleichung Pi = fi x Ci x Vi² berechnen. Darin sind fi die Frequenz (Schaltaktivitäten), Ci die kapazitive Last und Vi die Spannung der Ressource.

- Sparsame Systeme mit FPGAs entwerfen

- Sparsame Systeme mit FPGAs entwerfen

- Sparsame Systeme mit FPGAs entwerfen

- Sparsame Systeme mit FPGAs entwerfen

- 5