Effiziente Abbildung von Audio-Algorithmen in Programmierbarer Logik und ASICs

Rock ’n’ Roll im FPGA #####

Fortsetzung des Artikels von Teil 2

Rock ’n’ Roll im FPGA

Jobangebote+ passend zum Thema

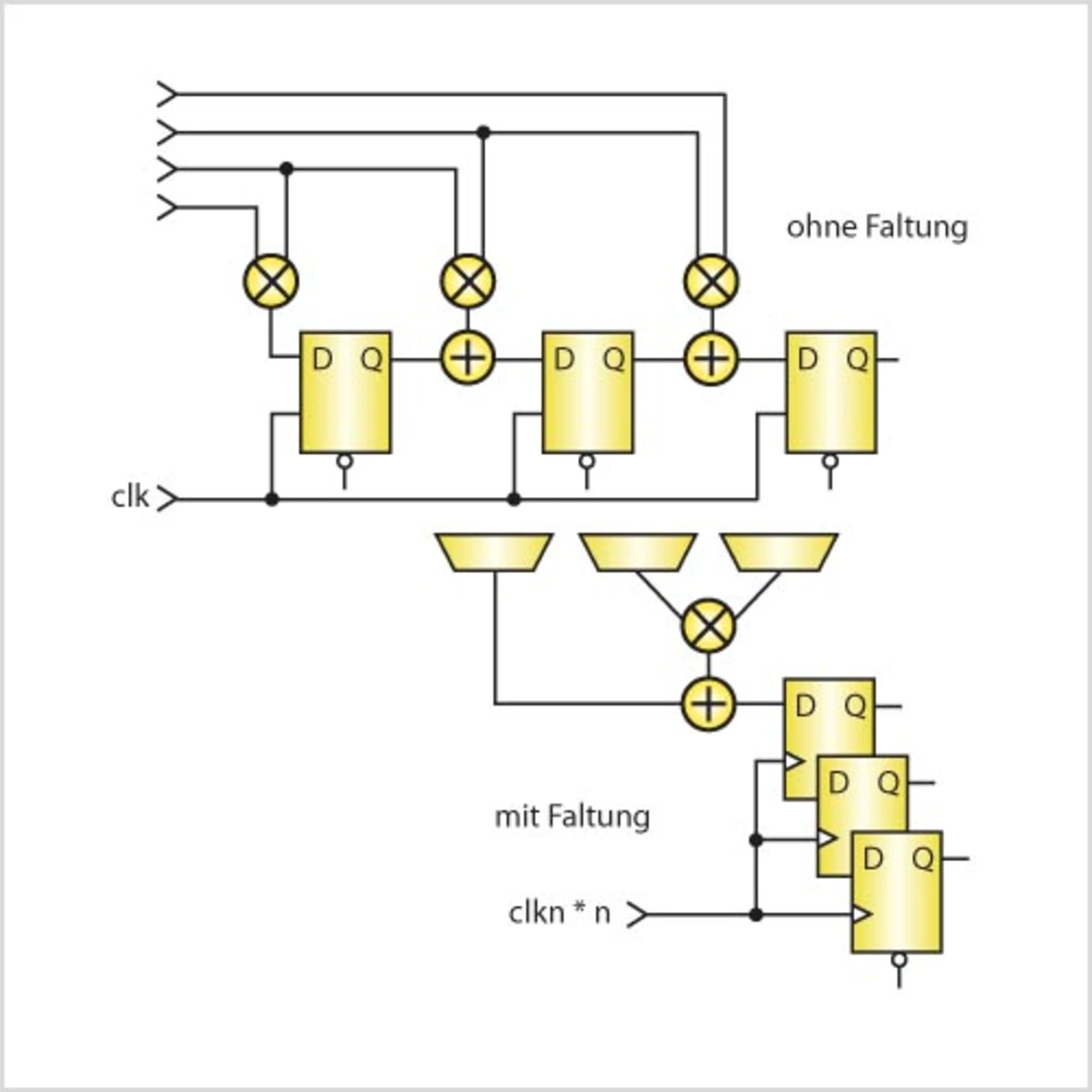

Die Optimierung mit Hilfe der „Folding“-Option

Synplify DSP stellt mit der Option „Folding“ die Möglichkeit zur Verfügung, die Anzahl der genutzten Multiplizierer praktisch beliebig zu minimieren (Bild 4). Speziell solche Schaltungen, die mit niedrigen Sample-Frequenzen betrieben werden, können von dieser Optimierung profitieren. Die Idee ist einfach: Im Normalfall wird für jede Multiplikation ein Hardware-Multiplizierer genutzt, auch wenn die Abtastfrequenz im Kilohertzbereich liegt. Das FPGA kann jedoch mit Taktraten in mindestens zweistelligem, üblicherweise sogar dreistelligem Megahertzbereich betrieben werden. Wird nun der Hardware-Multiplizierer mit der FPGA-Systemfequenz betrieben, kann in einem Zeitmultiplex-Verfahren eine serielle Abarbeitung der Multiplikationen erfolgen.

Ein praktisches Beispiel: Liegt die Sample-Frequenz der Schaltung bei 3 MHz und das FPGA kann mit maximal 120 MHz betrieben werden, so kann jeder einzelne Hardware-Multiplizierer im gleichen Zeitraum 40 Rechenoperationen durchführen, wenn die Systemfrequenz zur Multiplikation genutzt wird. Die notwendige Hardware wird also um den Faktor 40 reduziert. Die Verarbeitung von Audiosignalen erfolgt jedoch nicht mit Sample-Frequenzen im Megahertz Bereich. Die üblichen Abtastraten betragen – wie schon erwähnt – 44,1, 48, 96 oder 192 kHz. Daraus resultiert, dass ein Sample-Rate-Konverter (oder eine beliebige andere Schaltung, die mit geringen Abtastfrequenzen arbeitet) soweit „zusammengefaltet“ werden kann, dass nur noch sehr wenige Hardware- Multiplizierer benötigt werden. Eine Implementierung ist also auch in den kleinsten verfügbaren „Low-cost“-FPGAs möglich. Solche Bauteile werden von allen FPGA-Herstellern zu günstigen Preisen angeboten und stellen durchaus eine Alternative zu Digitalen Signalprozessoren dar. Es besteht natürlich auch die Möglichkeit, besonders rechenintensive Algorithmen aus einem DSP heraus in ein FPGA zu verlagern und so den Prozessor zu entlasten.

Da das Folding-Feature in Synplify DSP auch Multi-Rate-Systeme unterstützt, kann die Anzahl der benötigten Multiplizierer sogar noch weiter reduziert werden als in einem System mit einer einzigen Sample-Frequenz. Das Oversampling lässt sich mit Hilfe von zwei FIR-Filtern realisieren, und diese beiden Filter werden mit unterschiedlichen Sample-Frequenzen betrieben. Das Filter, das für die höhere Abtastfrequenz zum Einsatz kommt, wird mit dem vom Anwender spezifizierten Folding-Faktor gefaltet. Das Filter mit der geringeren Sample-Frequenz wird mit einem entsprechend höheren Faktor gefaltet – letzterer errechnet sich aus der Differenz der Sample-Frequenzen beider Filter, multipliziert mit dem vom Anwender definierten Folding- Faktor. Ist zum Beispiel die Abtastfrequenz des einen Filters achtmal so hoch wie die Sample-Frequenz des anderen Filters, dann wird der „schnellere“ Filter um den Faktor 8, der „langsamere“ um den Faktor 64 gefaltet. Hierdurch können auch solche Schaltungen platzoptimiert werden, die mit sehr hohen Abtastraten arbeiten und normalerweise eine Faltung nicht erlauben. Wird beispielsweise ein System mit einer Sample-Frequenz von 200 MHz betrieben und es wird ein Faltfaktor von 2 eingeführt, so steigt die Systemfrequenz auf 400 MHz. Eine solche Taktrate ist auch mit den durchsatzstärksten FPGAs nur schwerlich zu erreichen. Die Alternative: Es wird ein Folding-Faktor von 1 definiert. Die Schaltungsteile, die mit der höchsten Abtastrate betrieben werden, sind vom Falten ausgenommen. Alle Schaltungsteile eines Multi-Rate-Systems, die mit geringeren Sample-Frequenzen betrieben werden, profitieren aber von der Faltung und damit von der platzoptimierten Abbildung. Der Anwender muss den Faktor der Faltung nur für das Gesamtsystem vorgeben. Das Propagieren des Foldings über alle Abtastfrequenzen hinweg funktioniert dann automatisch.

- Rock ’n’ Roll im FPGA #####

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA