Effiziente Abbildung von Audio-Algorithmen in Programmierbarer Logik und ASICs

Rock ’n’ Roll im FPGA #####

Fortsetzung des Artikels von Teil 4

Rock ’n’ Roll im FPGA

Jobangebote+ passend zum Thema

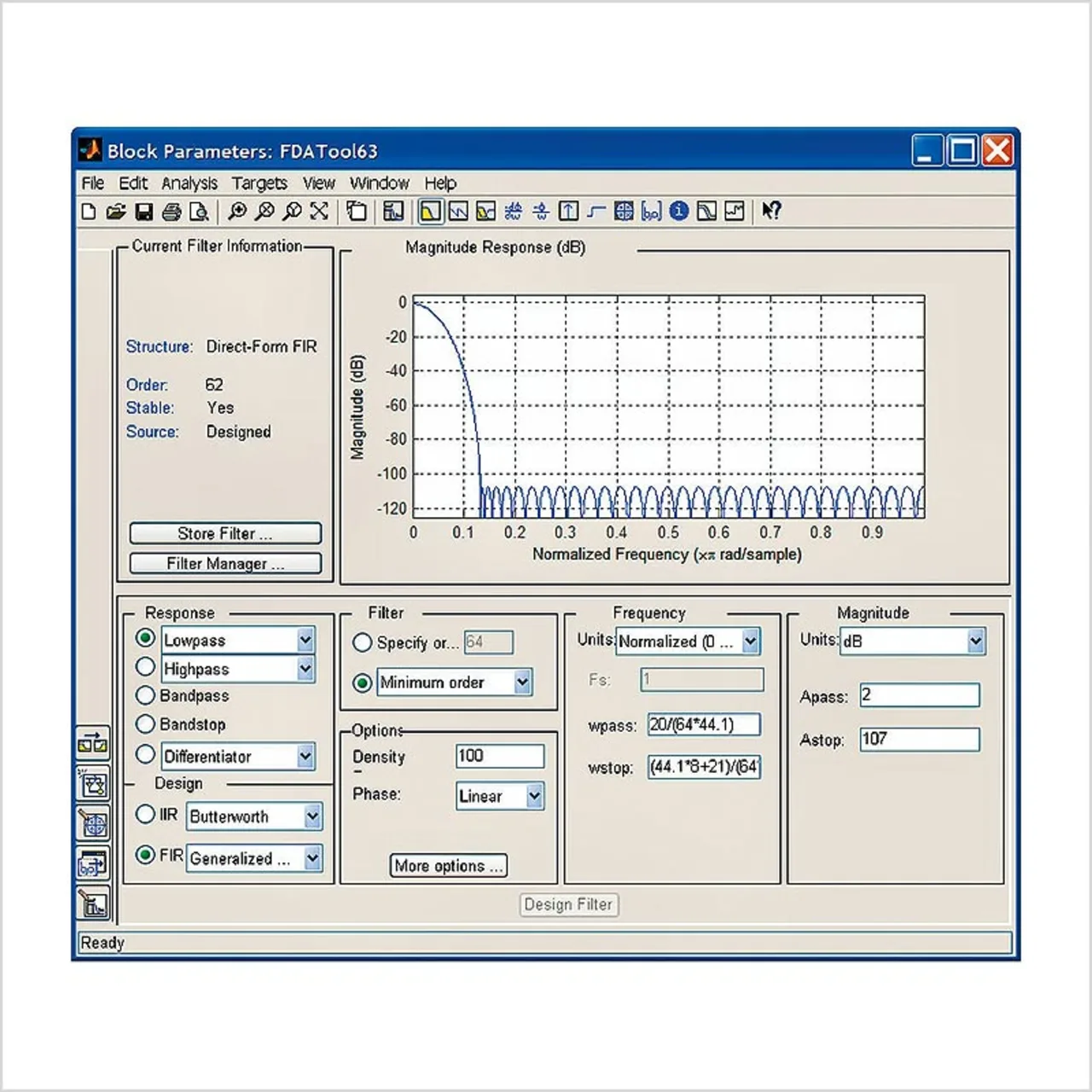

Die Implementierung mit Hilfe von „Filter Design and Analysis“

Die Schaltung wird in Simulink unter Nutzung des Synplify DSP Blocksets und des Simulink-“Filter Design and Analysis“-Tools (FDA) implementiert (Bild 3). Das FDA-Tool erlaubt die Generierung und Verifikation von beliebigen FIR- und IIR-Filtern. Es ist Bestandteil der Simulink „Signal Processing Toolbox“, auf die Synplify DSP für die Implementierung von Filterstrukturen zurückgreift. Alle Schaltungsbestandteile, die zwischen einer PortIN- und einer PortOUT-Beschreibung definiert sind und aus dem Synplify DSP Blockset oder dem FDATool stammen, generieren VHDLoder Verilog-Code.

Zur Spektralanalyse und Verifikation des Zeitverhaltens dienen FFTund SCOPE-Elemente aus Simulink Blocksets. Diese Blöcke dienen ausschließlich der funktionalen Verifikation inklusive Floating-nach-Fixed-Point-Konvertierungseffekten (Quantisierung) und werden nicht in Hardware abgebildet.

Der erste Teil der Algorithmen-Implementierung besteht aus zwei FIRFiltern: das erste Filter hat 512 Taps, das zweite 64. Der aus dem Oversampling resultierende RTL-Code beinhaltet dementsprechend 576 Multiplikationen, was eine Abbildung im FPGA aus kommerziellen Gründen nicht interessant erscheinen lässt. Ein hochkomplexes FPGA schlägt auf der Kostenseite mit mehreren tausend Euro zu Buche. Nur die komplexesten programmierbaren Logikbausteine verfügen über ausreichende Multiplikations-Ressourcen, um die Schaltung implementieren zu können (Altera Stratix-3 EP3SE110: 896 18×18-Multiplizierer, Xilinx Virtex-5 XC5VSX95TXC: 640 25×18-Multiplizierer). Alle Multiplikationen, die nicht in dedizierten Hardware-Strukturen (DSP-Blöcke) abgebildet werden, müssen aus Logikressourcen (LUT, Register) aufgebaut werden. Daraus resultiert eine hohe Auslastung der Bauteile bei gleichzeitig geringer maximaler Taktrate.

- Rock ’n’ Roll im FPGA #####

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA