Effiziente Abbildung von Audio-Algorithmen in Programmierbarer Logik und ASICs

Rock ’n’ Roll im FPGA #####

Fortsetzung des Artikels von Teil 3

Rock ’n’ Roll im FPGA

Jobangebote+ passend zum Thema

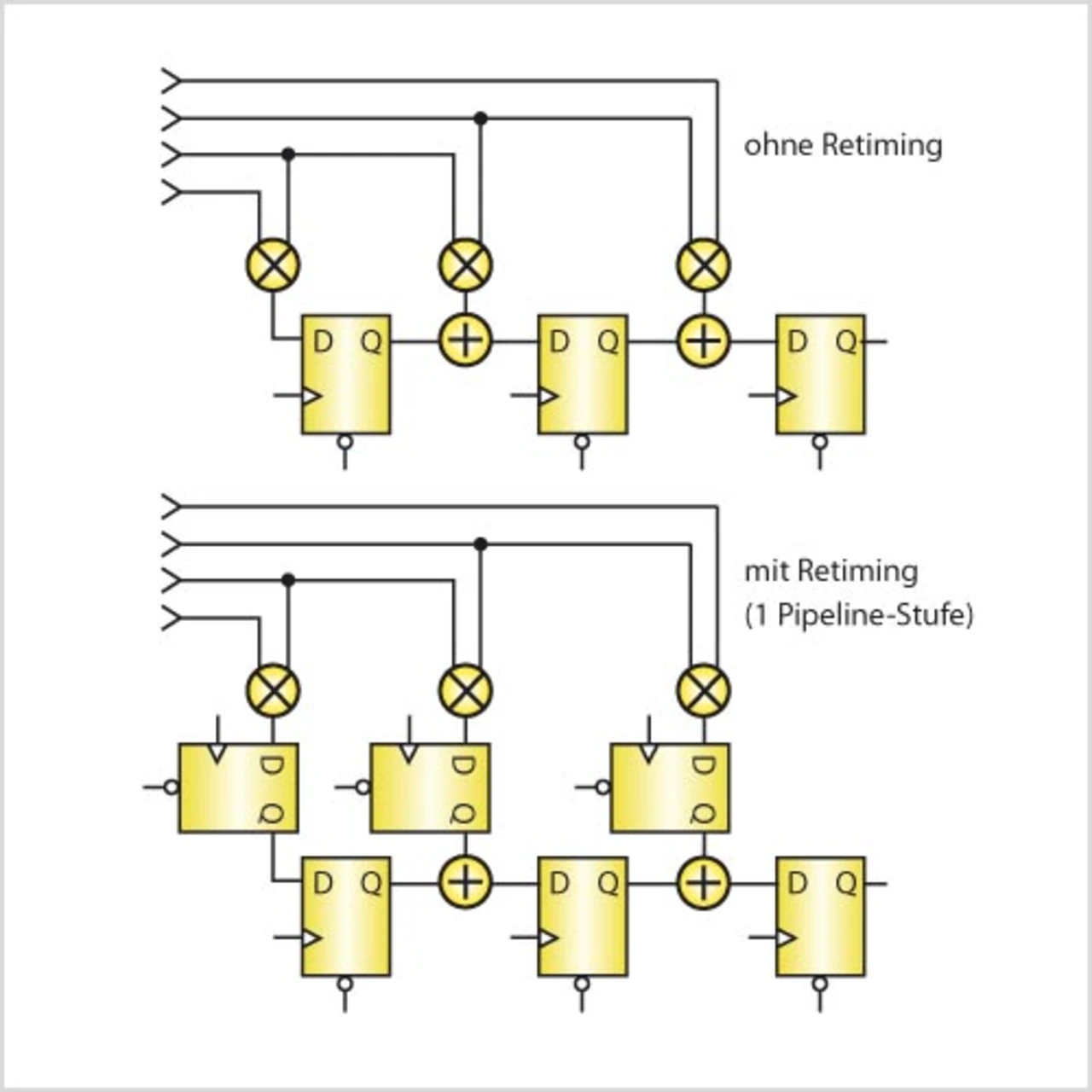

Das Folding-Feature ist mit einer weiteren Optimierungsmöglichkeit kombinierbar, dem „Retiming“ (Bild 5). Genügt ein Gesamtsystem nicht den Anforderungen an die Zielfrequenz, können so viele Pipeline-Stufen eingefügt werden, bis die gewünschte Taktrate erreicht wird. Das ist besonders in solchen Schaltungen wichtig, die einen erheblichen Folding-Faktor aufweisen und dementsprechend mit einer hohen Systemfrequenz betrieben werden müssen. Natürlich lässt sich das Retiming auch für solche Schaltungen nutzen, die wenig oder gar nicht gefaltet werden, sich aber an der Leistungsgrenze des FPGAs befinden. Das Einfügen von Pipeline-Stufen ermöglicht es, die Anzahl an kombinatorischen Gattern zwischen zwei Registern (Logic Levels) so weit zu reduzieren, bis die kombinatorischen Gatterverzögerungen die Taktfrequenz nicht mehr „ausbremsen“. Synplify DSP führt bei der Generierung des RTL-Codes eine Timing- Analyse durch, die sowohl die gewünschte Sample-Frequenz als auch den Faltfaktor und die Zielarchitektur des FPGAs berücksichtigt.

So wird eine Schaltung, die auf ein „schnelles“ FPGA abgebildet wird (z.B. Xilinx Virtex-5 oder Altera Stratix-3), mit weniger Pipeline-Stufen optimiert als eine identische Schaltung, die in einem „langsamen“ Low-cost-FPGA (z.B. Lattice ECP-2 oder Xilinx Spartan-3) implementiert wird. In FPGAs stehen große Mengen an Registern zur Verfügung, die für diese Optimierung genutzt werden können. Anders als die Anzahl der Multiplizierer oder LUTs (Look-up Tables), die schnell knapp werden können, sind Register in mehr als ausreichender Menge vorhanden und müssen im Normalfall nicht mit Bedacht genutzt werden. So lässt sich mit geringem Aufwand eine erhebliche Steigerung der Systemfrequenz erzielen. Selbstverständlich resultiert aus dem Einfügen von Pipeline-Stufen eine erhöhte Latenz des Systems. Wird ein Retiming-Faktor von z.B. 8 eingeführt, so erscheint das Ergebnis der Berechnung acht Taktzyklen (der Systemfrequenz, nicht der Sample-Frequenz) später am Ausgang des FPGA. Das muss beim Einbetten einer Schaltung in ein Gesamtsystem berücksichtigt werden.

Besonders wichtig ist, dass die zuvor beschriebenen Optimierungen das (in Matlab/Simulink beschriebene) Modell nicht beeinflussen. Der Algorithmus wird in Simulink implementiert und verifiziert. Die Verifikation erlaubt es, die Funktion des Algorithmus zu validieren und den Einfluss von Quantisierungseffekten darzustellen. Das Blockset der Synplify-DSPSoftware erlaubt es, die Floating-nach Fixed-Point-Konvertierung sowohl mittels Truncation (Eliminieren irrelevanter Bitstellen) als auch Rounding (bei Underflow) oder Saturation (bei Overflow) durchzuführen. Sobald die Simulation zeigt, dass der Algorithmus wie gewünscht funktioniert, kann der RTL-Code generiert werden. Das Optimieren des VHDL- oder Verilog-Codes verändert unter Umständen die Latenz, nicht aber die Funktion der Schaltung.

- Rock ’n’ Roll im FPGA #####

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA

- Rock ’n’ Roll im FPGA