PCI Express als Hard- und Soft-IP

Fortsetzung des Artikels von Teil 2

PCI Express als Hard- und Soft-IP

Elektronisches Zündsystem auf IGBT-Basis

Jobangebote+ passend zum Thema

Konkret zeigt E-Vison die Simulationsmöglichkeiten auf, TietoEnator spricht über die Problematik bei High-Speed-Layouts und wie man sie bewältigen kann und LeCroy erklärt, wie man die Hardware mit Oszilloskopen bzw. mit Protokoll-Analyzern überprüfen kann. Die nächsten Seminare finden im September statt (http://www.latticesemi.com/corporate/events/index.cfm).

Laut Werner zeigen die Industriekunden, die PCI in der Vergangenheit eingesetzt haben, zurzeit viel Interesse an PCIe. Sie seien aus Kompatibilitätsgründen gezwungen, auf PCIe umsteigen. Denn nur dann können sie auch weiterhin mit Standard-PC-Motherboards arbeiten. Werner: »Bei neuen PC-Motherboards stehen nur noch selten PCI-Slots zur Verfügung. Hier wird meist der PCIExpress x1-Core verwendet.«

Kunden, die eine schnelle Datenerfassung benötigen, stürzen sich seiner Aussage nach vorwiegend auf den PCI-Epxress-x4-Core, da hier ein sehr schneller Datendurchsatz erreicht werden kann, abhängig vom verwendeten Motherboard. Anwendungen mit diesen Leistungsanforderungen sind beispielsweise in der Medizintechnik sowie in der Messinstrumententechnik zu finden.

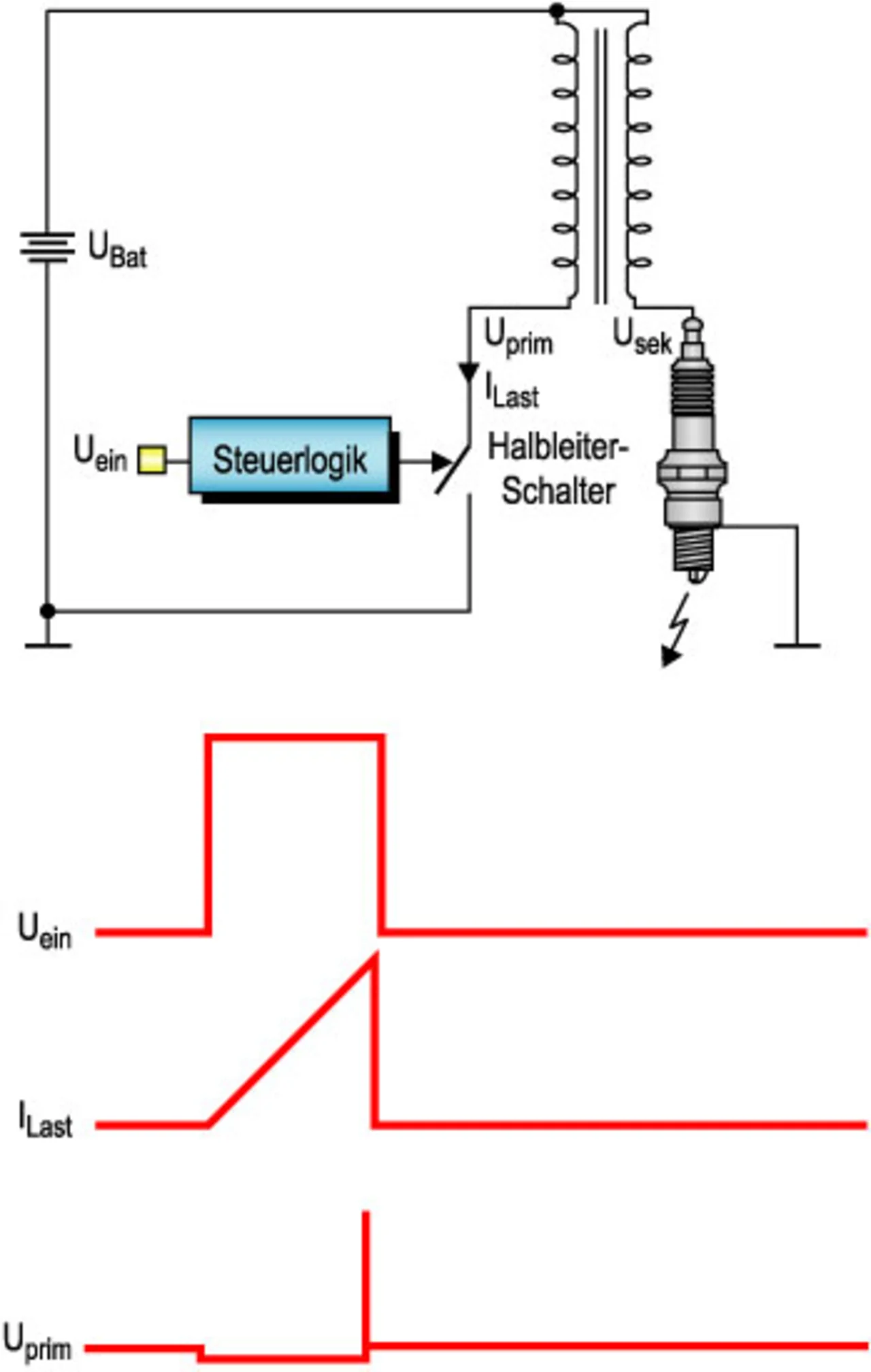

Das elektronische Zündsystem erzeugt den Funken, mit dem in einem Benzinmotor das Kraftstoff-Luft-Gemisch entzündet wird. In den meisten Fällen werden zu diesem Zweck induktive Zündsysteme (Inductive Discharge Ignition, IDI) benutzt. Bei Motoren mit höheren Drehzahlen setzt man dagegen auf andere Lösungen, die jedoch komplexer und deshalb auch teurer sind als konventionelle, induktive Systeme. Ein IDI-Zündsystem besteht aus einer Zündspule, einem elektronischen Schalter und einer Zündkerze (Bild 5). Die Zündspule ist im Prinzip ein Transformator mit einem Windungsverhältnis im Bereich von 1:100. Nach dem Einschalten des primärseitigen Schalters fließt in der Primärwicklung ein Strom, der ein Magnetfeld in der Primärinduktivität erzeugt. In dieser Phase wird die Stromstärke auf der Primärseite durch den Spannungsabfall am Hochspannungsschalter (Uein) bestimmt. Die gespeicherte Energie beträgt 1/2 x L x I2; es baut sich ein magnetisches Feld auf. Sobald der primärseitige Schalter öffnet, bricht der Strom in der Primärwicklung – und damit das magnetische Feld – abrupt zusammen, wodurch die gespeicherte Energie in Form einer hohen Spannungsspitze freigesetzt wird. Der Maximalwert dieser Spannung wird meist auf einige hundert Volt an der Primärwicklung begrenzt, um die Sekundärspannung genau zu regeln. Diese Spannung liegt, um das Windungsverhältnis vervielfacht, an der Sekundärwicklung an, sodass eine genügend hohe Spannung (30 bis 40 kV) entsteht, um den Elektrodenabstand der Zündkerze mit einem Lichtbogen zu überbrücken. Der gesamte Vorgang läuft unter der direkten Kontrolle eines Mikrocontrollers ab, um zu gewährleisten, dass die Zündfunken zum richtigen Zeitpunkt und im richtigen Zylinder erzeugt werden.

Xilinx bietet laut Chuck Tralka, Senior Director im Product Marketing für High-Performance FPGAs bei Xilinx, eine ganze Reihe von skalierbaren PCIe-Lösungen an und zwar sowohl in Form von Software-IP als auch in Form von fest verdrahteten Hardware- IP-Implementierungen. Die Lösungen beinhalten Software/Treiber-Entwicklungs-Kits, Referenz- Designs und IP von einer wachsenden Anzahl von Drittunternehmen. Tralka: »Daraus ergibt sich ein Ecosystem von unabhängigen Design-Service- und IP-Anbietern.«

Für eine Hardware-Implementierung stehen bei Xilinx die Virtex-5-FPGAs (65 nm) zur Verfügung, die mit einem PCIe-Endpunkt-Block ausgestattet sind. Darin sind Transaction-, Data- Link- und Physical-Layer-Funktionen implementiert. »Damit steht eine vollständige PCIe-Endpunkt-Funktionalität zur Verfügung, die nur minimale FPGA-Logik braucht«, so Tralka weiter. Daneben bietet Xilinx aber auch PCIe-Lösungen für seine Spartan- und älteren Virtex-Familien an. Außerdem stehen noch eine Vielzahl von Entwicklungs- und Evaluierungs- Plattformen für PCIe-Designs zur Verfügung, einschließlich dem Virtex5 LXT FPGA-Entwicklungs-Kit für PCI-Express. Tralka: »Damit sind die Entwickler in der Lage, sehr schnell Designs zu erzeugen und zu evaluieren, die PCIe, PCI-X und PCI-Schnittstellen beinhalten.«

Außerdem stehen Kits von Drittunternehmen zur Verfügung sowie Kits, die die kostengünstige Spartan-FPGAs unterstützen. Dass ein Entwickler selbst für einen bereits etablierten Standard eine FPGA-basierende Lösung nutzt, liegt laut Tralka unter anderem daran, dass er damit in den Genuss der Flexibilität der FGPATechnologie kommt. Damit sei er im Vergleich zu einer ASSP-Lösung immer noch in der Lage, sein Produkt von konkurrierenden Ansätzen zu differenzieren. Hinzu käme noch, dass sich der Entwickler dank der PCIe-Komplettlösung, einschließlich Entwicklungs-Plattformen, mehr auf die Implementierung seiner Innovationen fokussieren kann, anstatt Zeit und Geld zu verschwenden, um Schaltungen zu realisieren, die einen allgemein üblichen Standard wie PCI Express unterstützen.

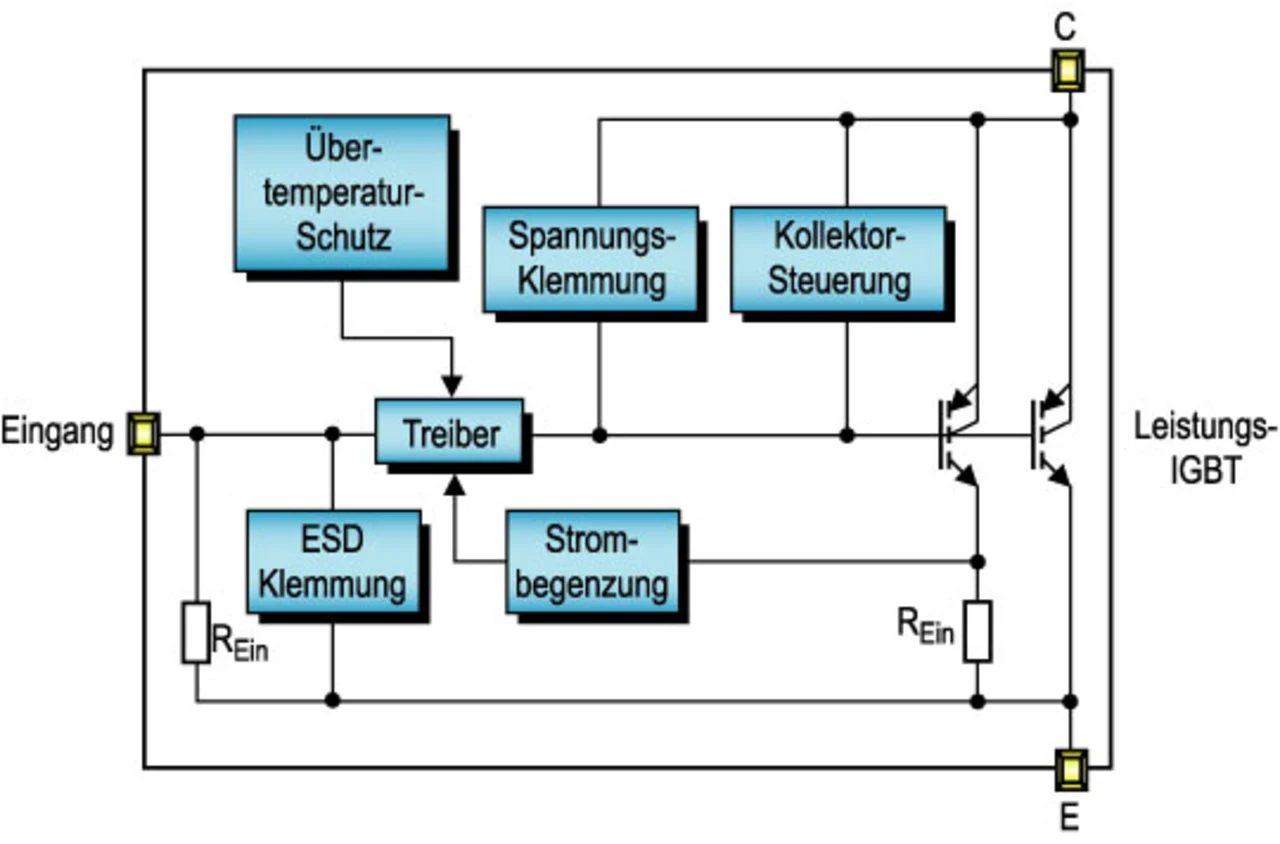

Ein IGBT bringt ideale Voraussetzungen für die Anforderungen mit, die das neue elektronische Zündsystem an die Stromtragfähigkeit stellt, denn er verbindet die einfache Ansteuerung eines MOSFET mit der hohen Stromfestigkeit eines bipolaren Transistors. Verglichen mit einer bipolaren Struktur punktet ein IGBT mit folgenden Vorteilen:

- höhere Stromtragfähigkeit als ein bipolarer Sperrschicht-Transistor mit gleicher Halbleiterfläche,

- die Ansteuerung durch eine Spannung ist einfacher und reduziert die Verluste,

- eingebauter Verpolungsschutz. Die interne P+/N+/N/P-Struktur bildet eine Folge von Dioden und schützt den Baustein somit vor Schäden, wenn die Batterieanschlüsse vertauscht werden.

PCIe passt derzeit nicht zu Actels Strategie

Actel bietet bis lang noch keinen IP-Core für PCIe an. Laut Edmund Gerstl, Senior Region Manager Central Europe bei Actel, passt das aber auch nicht zur Strategie von Actel. Denn Actel unterscheidet sich in einem Punkt ganz deutlich von den anderen FPGA-Herstellern: Actel macht im Rennen um die größten FPGAs mit den höchsten Kapazitäten nicht mit.

Vielmehr sind Themen wie »Mixed-Signal« oder »niedrigste Leistungsaufnahme« die Antriebsfedern in der Entwicklung des Actel-Produktportfolios. Edmund Gerstl weiter: »Da ein PCIe-IP-Core sehr viele Logik-Gates benötigt, passt dies nicht optimal in unser Angebot.« Allerdings bietet das Unternehmen eine PCI-Lösung an, die laut Gerstl von vielen Kunden eingesetzt wird. Der Grund, warum auf Standards basierende IP-Cores in einem FPGA Sinn machen, besteht laut seiner Aussage nach in der Fähigkeit, kundenspezifische Anpassungen zum Standard zu machen oder den Standard zusammen mit weiterer kundenspezifischer Logik zu integrieren. Gerstl: »Actel geht auch den zusätzlichen Schritt der Zertifizierung seiner auf Standards basierten IP, um garantieren zu können, dass er die volle Spezifikation erfüllt.« Iris Stroh

Lattice Semiconductor bietet ebenfalls zwei Ansätze für PCIe:

- eine Lösung für die High-End-FPGAs »LatticeSC«;

- eine Lösung für eine Low-Cost-Implementierung in den »LatticeECP2M«-FPGAs.

Laut Harald Werner, Area Technical Manager Central Europe bei Lattice Semiconductor, ist bei den LatticeSC-Bausteinen der Großteil des PCI-Express-IP-Cores in Hardware fest verdrahtet implementiert. Dementsprechend müsse nur noch ein kleiner Teil des Transport-Layers als programmierbare Logik hinzugefügt werden. Werner: »Es entstehen hier für den Kunden keine zusätzlichen Kosten an Lizenzgebühren.« Lattice bietet für die High-End-FPGAs eine x1- bis x4 PCIe-Lösung an.

Der Ansatz mit einem High-End-FPGA ist für Werner dann sinnvoll, wenn der Kunde die weiteren Features dieser Familie, wie zum Beispiel in Hardware (in sogenannten MACOs – MACO steht für Masked Array for Cost Optimization) implementierte Memory-Controller (DDR2 bis 667 MBit/s, QDR, RLDRAM), GBit-Ethernet, 10G-Ethernet, SPI4.2 Interface etc., nutzen möchte. Diese Schnittstellen sind bereits implementiert und können vom Kunden direkt genutzt werden. Werner: »Da diese als MACO implementiert sind, entstehen Vorteile bei der Verlustleistung. Denn im Vergleich zu einer Implementierung mittels Logik sinkt die Verlustleistung bis um den Faktor 3.« Bei High-End-FPGAs kommt natürlich noch hinzu, dass auch die FPGA-Fabrik schneller als bei Low-Cost-FPGAs ist, was speziell in Telecom-Applikationen vorteilhaft ist.

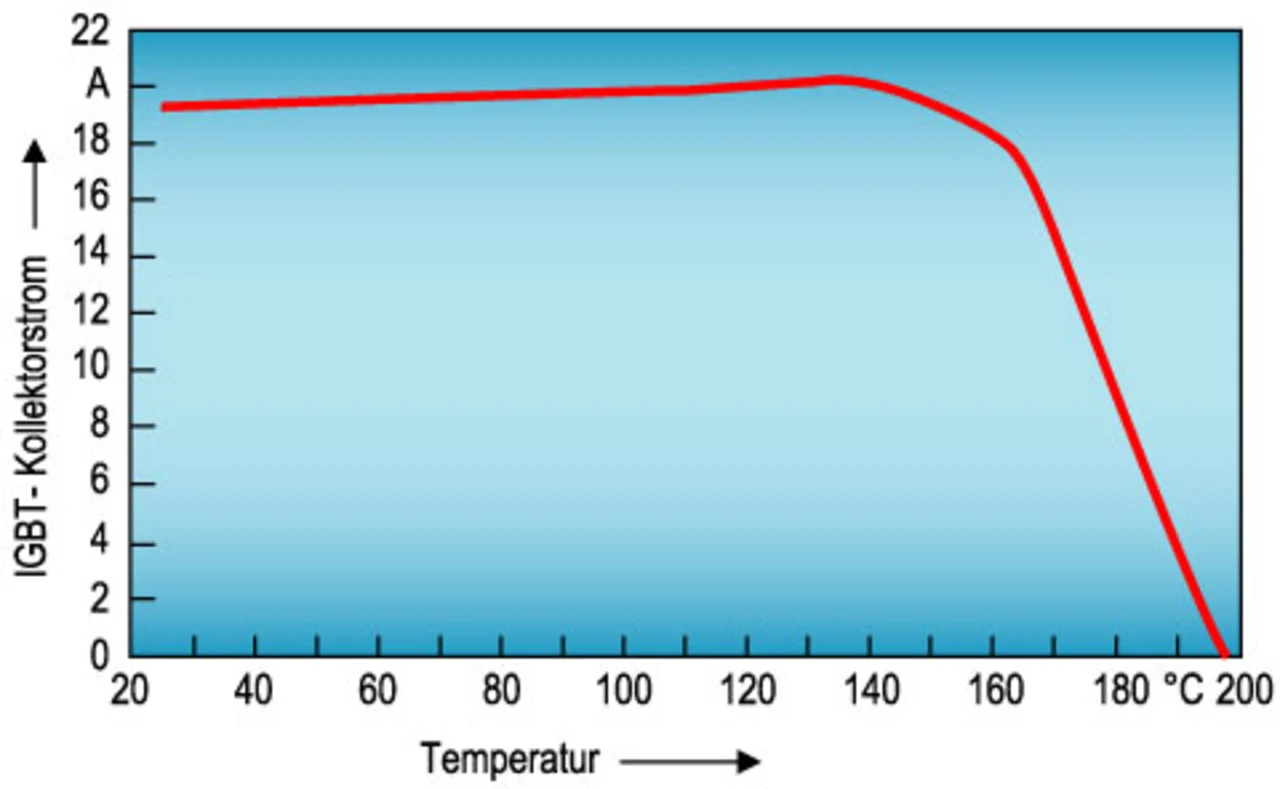

In der vorliegenden Applikation wird sogar ein Merkmal, das sonst zu den Schwächen des IGBT gezählt werden muss, zu einem Vorteil. Bei der hier vorliegenden Struktur handelt es sich, wie erwähnt, um eine bipolare PNP-Stufe, die durch einen N–-MOSFET angesteuert wird. Wenn der Baustein abgeschaltet wird und das Gate-Signal auf einen niedrigen Pegel zurückgeht, kann der Kollektorstrom nicht sofort auf Null fallen, da die Minoritätsträger in der Ausgangsstufe zunächst abfließen müssen. Dieser Effekt bewirkt einen Nachlaufstrom, der sich geringfügig auf die Verlustleistung des Bausteins auswirkt und die Ausschaltzeit des Schalttransistors erhöht. Die Folgen sind ein weniger steiler Rückgang des Stroms beim Abschalten und eine Verringerung der elektromagnetischen Störstrahlung (EMV), insbesondere bei hohen Motordrehzahlen. Diese Aspekte im Verbund mit dem Trend zum Einsatz von Stabzündspulen (Pencil Coils), bei denen es auf minimalen Platzbedarf ankommt, macht die Verwendung intelligenter Leistungs-IGBTs unumgänglich.

- PCI Express als Hard- und Soft-IP

- Steigen die Preise für FPGAs?

- PCI Express als Hard- und Soft-IP

- PCI Express als Hard- und Soft-IP