PCI Express als Hard- und Soft-IP

Fortsetzung des Artikels von Teil 1

Steigen die Preise für FPGAs?

Die Smart-Power-IGBT-Technologie ermöglicht die Integration einer IGBT-Leistungsstufe mit folgenden Kleinsignal-Funktionen:

- NMOS-Anreicherungstransistoren,

- Polysilizium-Widerstände,

- Polysilizium-Dioden,

- Strommess-IGBT,

- Hochspannungs-Widerstände (von ST zum Patent angemeldet).

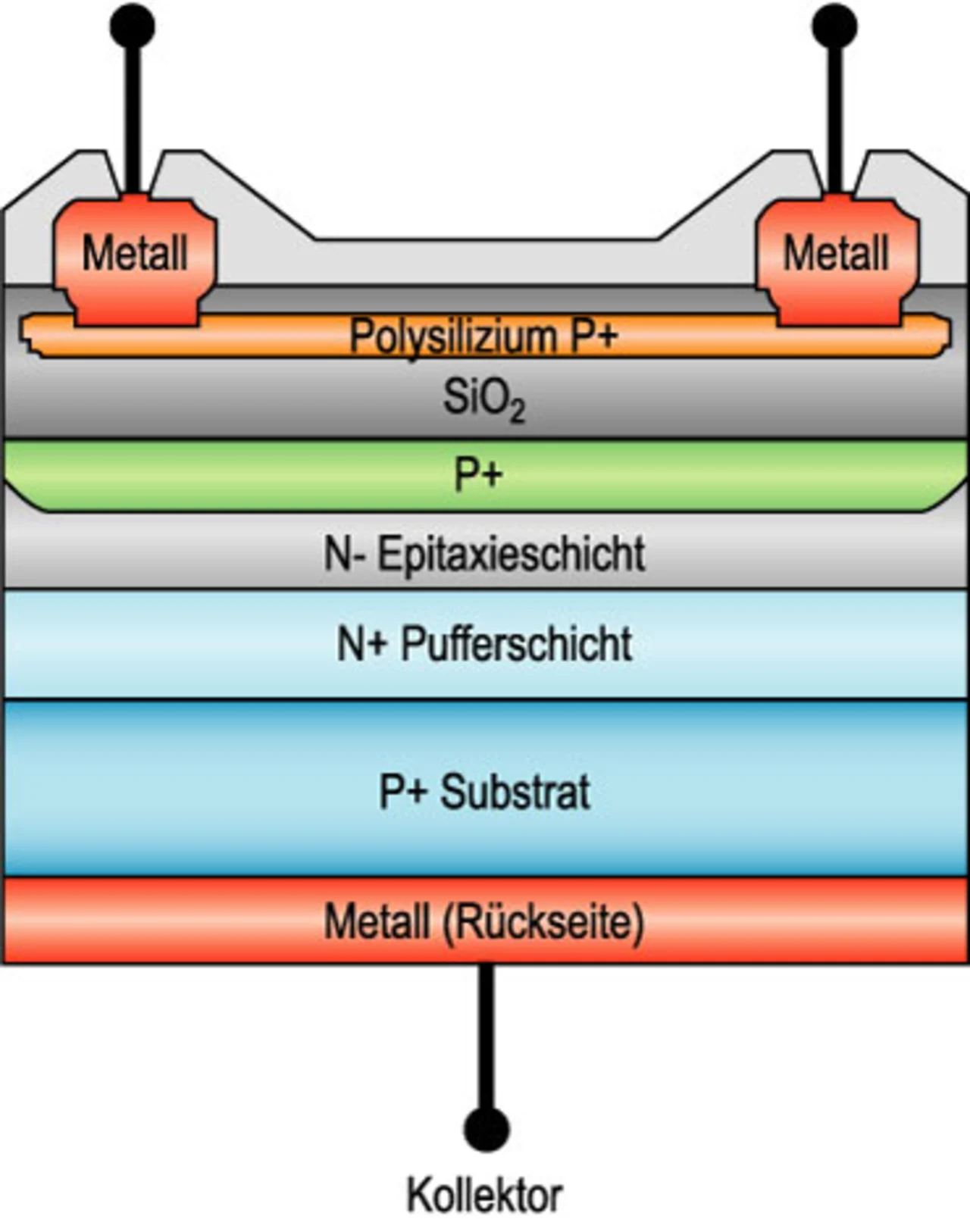

Der Produktionsprozess dieser Smart-Technologie entspricht dem eines herkömmlichen IGBT, und auch die Zahl der Masken für die Fotolithographie ist identisch. Als Leistungsstufe dient ein vertikaler IGBT im Strip-Layout, dessen Technologie für einen sehr geringen Spannungsabfall im eingeschalteten Zustand und für erhöhte Durchbruchfestigkeit (Latch-up Immunity) bürgt. Wie Bild 1 zeigt, ist zwischen das P+-Substrat und die N–-Driftregion eine N+-Pufferschicht eingefügt, um einen Punch-Through-IGBT zu realisieren. In einer solchen Struktur lässt sich die Dicke der N–-Driftregion ohne Beeinträchtigung der Sperrspannung in Durchlassrichtung reduzieren, da sich die Sperreigenschaften durch die N+-Pufferschicht verbessern. Dies führt zu einer Verringerung des Spannungsabfalls im eingeschalteten Zustand.

Jobangebote+ passend zum Thema

Es wird seit einiger Zeit heftig darüber diskutiert, dass die Foundries ihre Wafer-Preise anheben müssen. Denn mit den jetzigen Preisen sei ein Return on Investment nicht möglich. Da mehr oder minder die gesamte FPGA-Industrie aus Unternehmen besteht, die über keine eigenen Produktionsstätten verfügen, ist die Abhängigkeit hier besonders groß.

Wie schätzen also die Hersteller die Situation ein? Und wenn die Foundries ihre Preise erhöhen, schlägt sich das auf die FPGA-Preise nieder? – Fragen, die Xilinx und Lattice Semiconductor unbeantwortet ließen, lediglich Actel und Altera äußerten sich dazu – wenn auch zum Teil sehr vage.

Edmund Gerstl, Senior Region Manager Central Europe bei Actel: »Diesbezüglich gibt es zwei Faktoren zu Gunsten von Actel. Erstens ist unser Portfolio darauf ausgerichtet, den Kunden Bausteine mit dem geringstmöglichen Stromverbrauch zu niedrigen Preisen anzubieten. Wir benutzen dazu nicht die Prozesstechnologie mit den jeweils kleinsten Strukturen. Als Ergebnis ist unser Foundry-Preisniveau stabil und richtet sich nur nach unserer Nutzung. Im Zuge unseres weiteren Wachstums, das genau nach Plan verläuft, werden wir mehr Wafer benötigen und können deshalb künftig mit niedrigeren Preisen rechnen. Zweitens sind wir, gemessen an der insgesamt verfügbaren Kapazität, noch kein bedeutender Konsument von Wafern und spüren daher keine Kapazitätsengpässe. Aus diesem Grund haben wir ausreichend große Wachstumsmöglichkeiten, bevor unsere Foundry-Partner in neues Equipment investieren müssen, mit dem sie unsere Anforderungen erfüllen könnten. Auf der Basis dieser Situation und im Zuge unseres weiteren Wachstums erwarten wir, dass die Preise für unsere Wafer weiter sinken werden.«

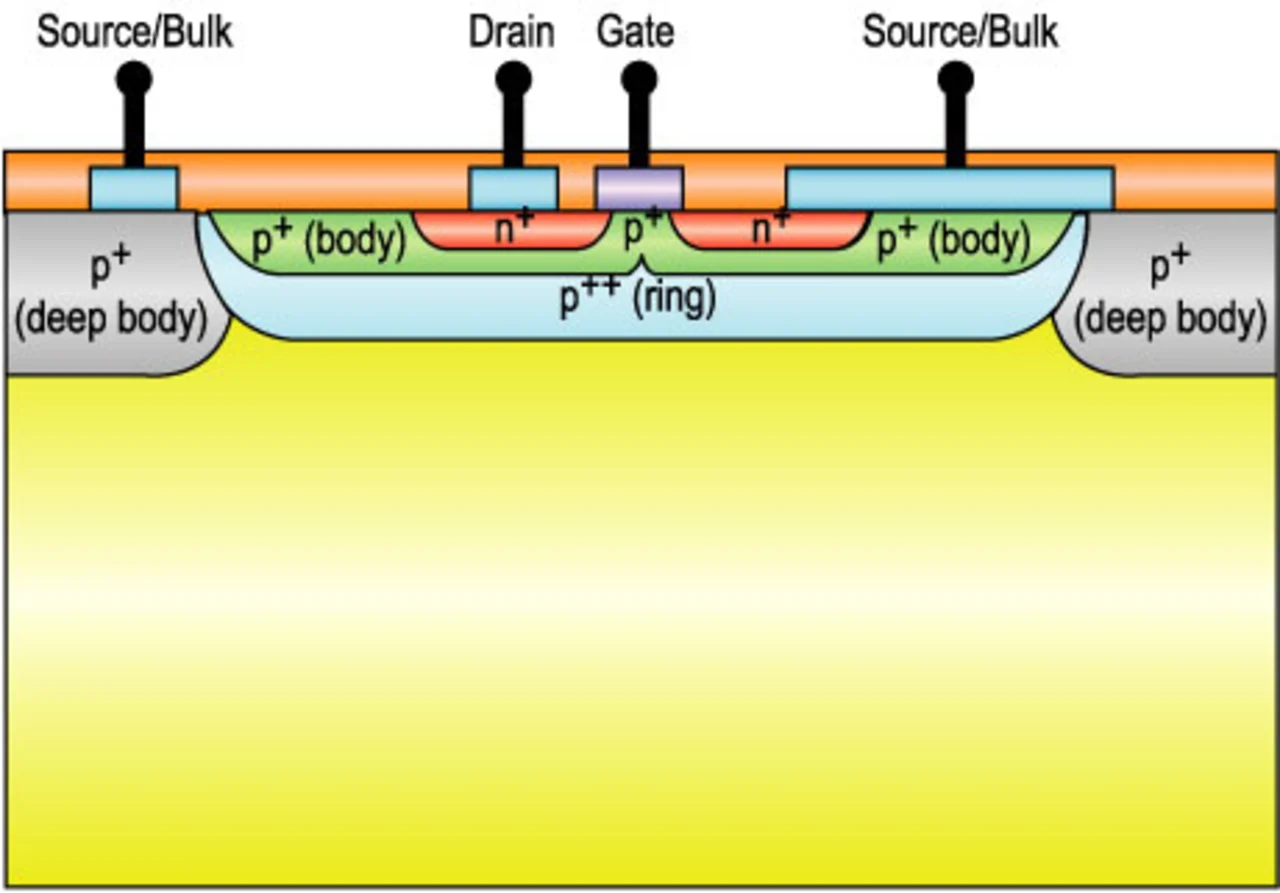

Bei den Kleinsignal-N–-Kanal-MOSFETs handelt es sich um lateral diffundierte Anreicherungs-Transistoren (Bild 2). Gateoxid und Polysilizium sind mit der Leistungsstufe identisch. Drain und Source werden außerdem gemeinsam mit der Source-Implantation des IGBT hergestellt. Die Kanallänge ist auf dem gesamten Chip identisch, und die unterschiedlichen Stromtragfähigkeiten werden durch unterschiedlich große Umfänge realisiert. Bulk- und Source-Elektroden eines Transistors müssen kurzgeschlossen werden, und die Bulk-Zone ist elektrisch mit der Body-Zone des IGBT verbunden. Aus diesem Grund müssen die MOSFETs in Source-Schaltung betrieben werden.

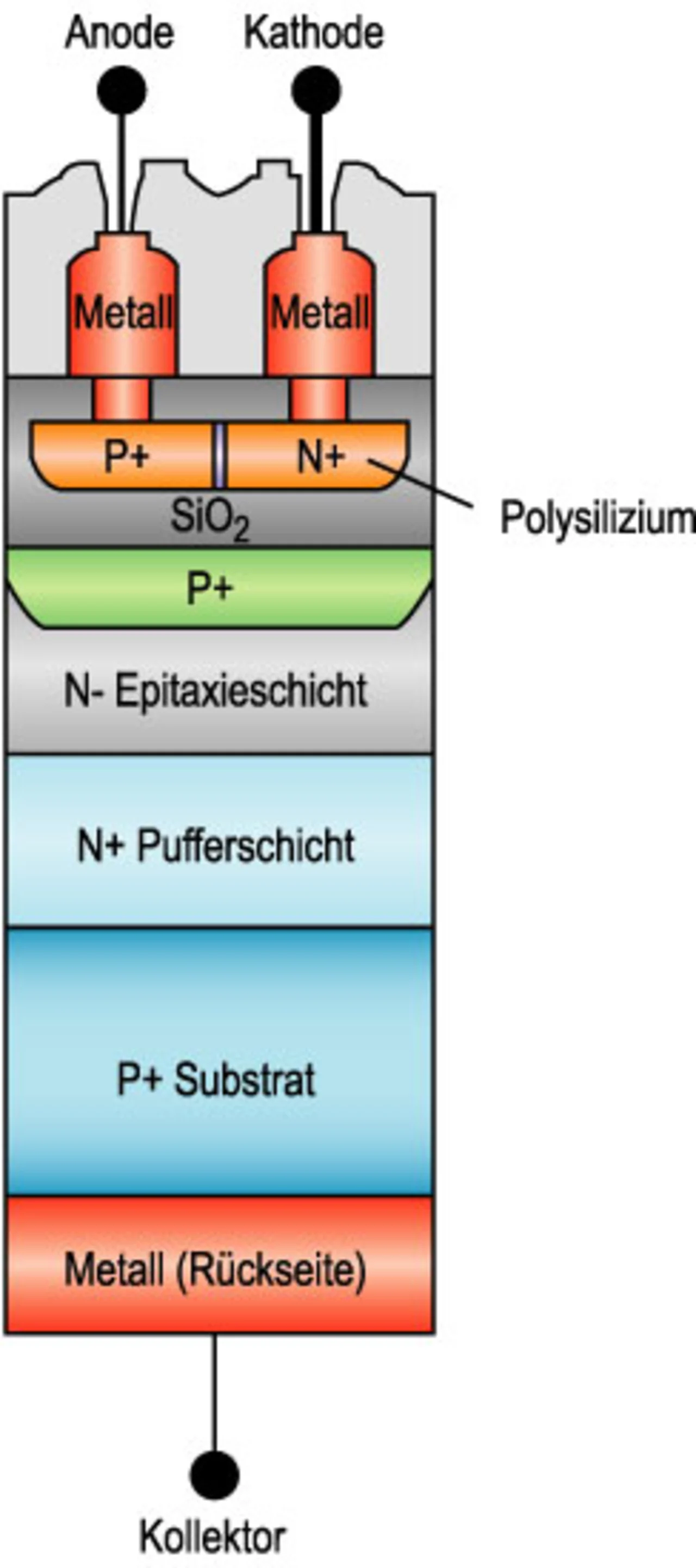

Nun zu den Polysilizium-Elementen: Die Widerstände (Bild 3) werden aus P+-dotierten Polysilizium-Streifen gebildet, deren Eigenschaften von Temperaturänderungen kaum beeinflusst werden. Dies ist ein sehr wichtiges Kriterium, da diese Elemente hauptsächlich zur Implementierung der Spannungsteiler für die eingebauten Schutzfunktionen verwendet werden. Die P+-dotierten Streifen eignen sich außerdem besser als N+-dotierte Zonen zur Herstellung von Kontakten.

Danny Biran, Altera. Sr. Vice President, Product and Corporate Marketing bei Altera: »Generell lässt sich sagen, dass mit komplexeren Halbleitern und fortschrittlicheren Prozesstechnologien die gesamte Wertschöpfungskette in der Halbleiterindustrie nach Wegen suchen sollte, ein vernünftiges Return on Investment zu erzielen. Und das tut sie auch. Aber Preise sind nur ein Element im Gesamtbild. Andere Elemente beinhalten Design-Methodiken, verschiedene Partnerschaftsmodelle zwischen Supplier und Kunden und vieles mehr. Tatsächlich profitiert die PLD-Industrie von einigen dieser Trends. Nachdem Design-Starts mit ASICs weiter zurückgehen, finden PLDs in immer mehr Märkten ihren Einsatz und stellen oft das Herz des gesamten Systems dar. Wir können keine speziellen TSMC-Pläne kommentieren. Aber wir verfügen über eine exzellente Partnerschaft, die mittlerweile schon 15 Jahre währt. Wir diskutieren mit TSMC zusammen kontinuierlich die Industrietrends und die besten Lösungen, um diesen Trends gerecht zu werden.«

Iris Stroh, Markt&Technik

Die Polysilizium-Dioden basieren auf PN–-Sperrschichten aus N+- und P+-dotierten Polysilizium-Streifen und dienen zur Integration verschiedener Strukturen:

- Kollektor-Emitter-Klemmung

Hiermit wird die Kollektor-Emitter-Spannung des Leistungs-Transistors auf einen bestimmten Maximalwert begrenzt. Zum Schutz der Sperrschicht zwischen Substrat und N–-Driftregion muss dieser Grenzwert deutlich unterhalb der Durchbruchsspannung angesetzt werden, die durch die Dicke und Dotierung beider Schichten bestimmt wird. - Schutz vor Elektrostatischer Entladung (ESD, Electrostatic Discharge)

Hiermit wird eine Beschädigung der Oxidschicht durch elektrostatische Entladungen verhindert. - Temperatursensor-Diode

Dank der Temperaturabhängigkeit der Durchlassspannung einer PN–-Sperrschicht (Bild 4) lässt sich die interne Sperrschichttemperatur des Bausteins erfassen.

Der Strommess-IGBT wird durch Aufteilung des Leistungs-Teils in mehrere identische Zellen realisiert. In Verbindung mit einem internen Strommesswiderstand ermöglicht dieses Element das Erfassen eines Stroms, der proportional zum Kollektorstrom ist und zur Regelung der Ansteuerspannung für den IGBT herangezogen werden kann. Überdies wird der maximale Ausgangsstrom der Leistungsstufe auf einen unkritischen Wert begrenzt.

Das letzte und zugleich innovativs-te integrierte Element ist der Hochspannungs-Widerstand (von ST zum Patent angemeldet). Er besteht aus einer JFET-Struktur, die als Hochspannungs-Widerstand dient und eine Rückkopplung vom Kollektor zum Gate des IGBT bewirkt.

Mit diesen Elementen – zusammen mit einem Leistungstransistor integriert – entsteht ein intelligenter Leistungsschalttransistor mit verschiedenen Schutzfunktionen; Schutzfunktionen, die für zahlreiche Anwendungen erforderlich sind und normalerweise mit externen Komponenten realisiert werden.

- PCI Express als Hard- und Soft-IP

- Steigen die Preise für FPGAs?

- PCI Express als Hard- und Soft-IP

- PCI Express als Hard- und Soft-IP