PCI Express als Hard- und Soft-IP

Fortsetzung des Artikels von Teil 3

PCI Express als Hard- und Soft-IP

Der monolithische Smart IGBT von STMicroelectronics ist ein Baustein mit drei Anschlüssen, der sich ganz besonders für elektronische Zündsysteme eignet. In einem solchen Bauelement sind neben der eigentlichen Leistungsstufe die folgenden Funktionen integriert (Bild 6):

- Überstromschutz

Der Strommess-IGBT liefert ein um einen definierten Faktor herabskaliertes Abbild des Haupt-Ausgangsstroms, das zur Überwachung des Ausgangsstroms dient. Mit dieser Funktion lässt sich eine Strombegrenzung als Überlastungsschutz realisieren. - Überhitzungsschutz

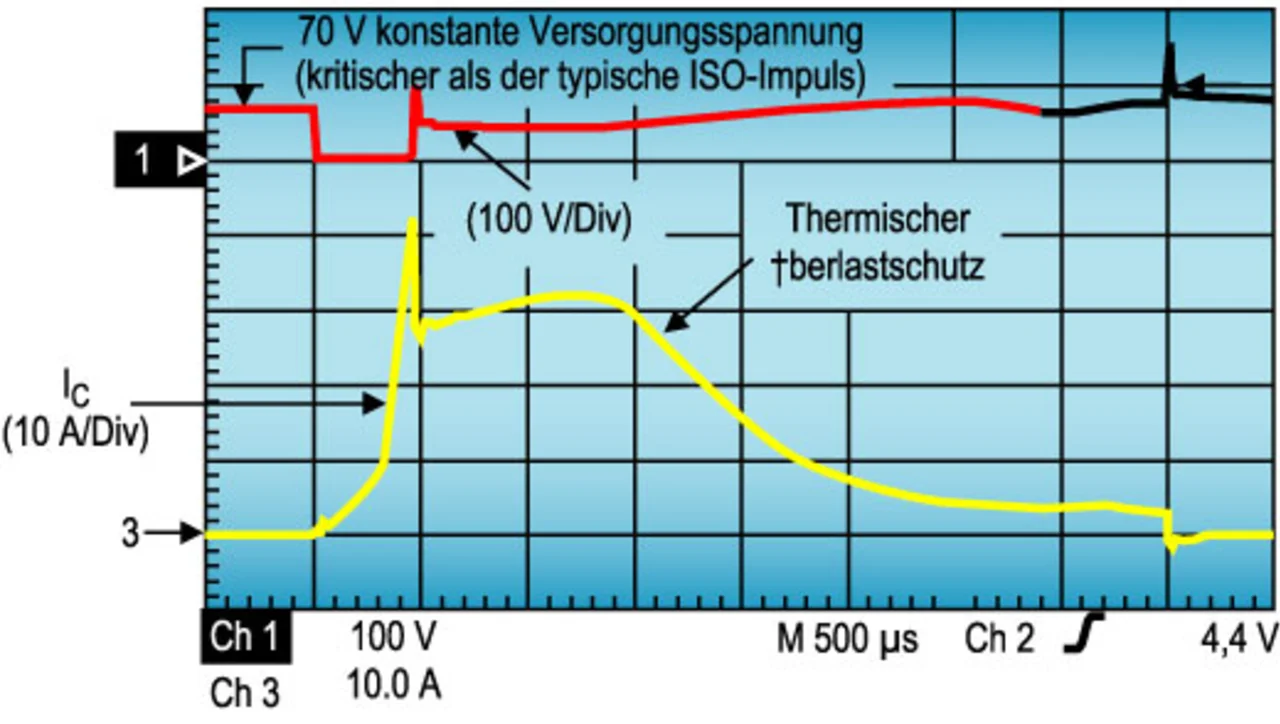

Der Überhitzungsschutz wirkt dynamisch auf das Treibersignal am Gate des Haupt-IGBT ein, um den Laststrom zu reduzieren, wenn die interne Temperatur einen bestimmten Grenzwert erreicht. Diese Funktion wird auch als „Soft Thermal Shutdown“ bezeichnet, da der Kollektorstrom nicht abrupt unterbrochen, sondern je nach der internen Sperrschichttemperatur lediglich reduziert wird (Bild 7). - Kollektor-Überspannungs-Schutz

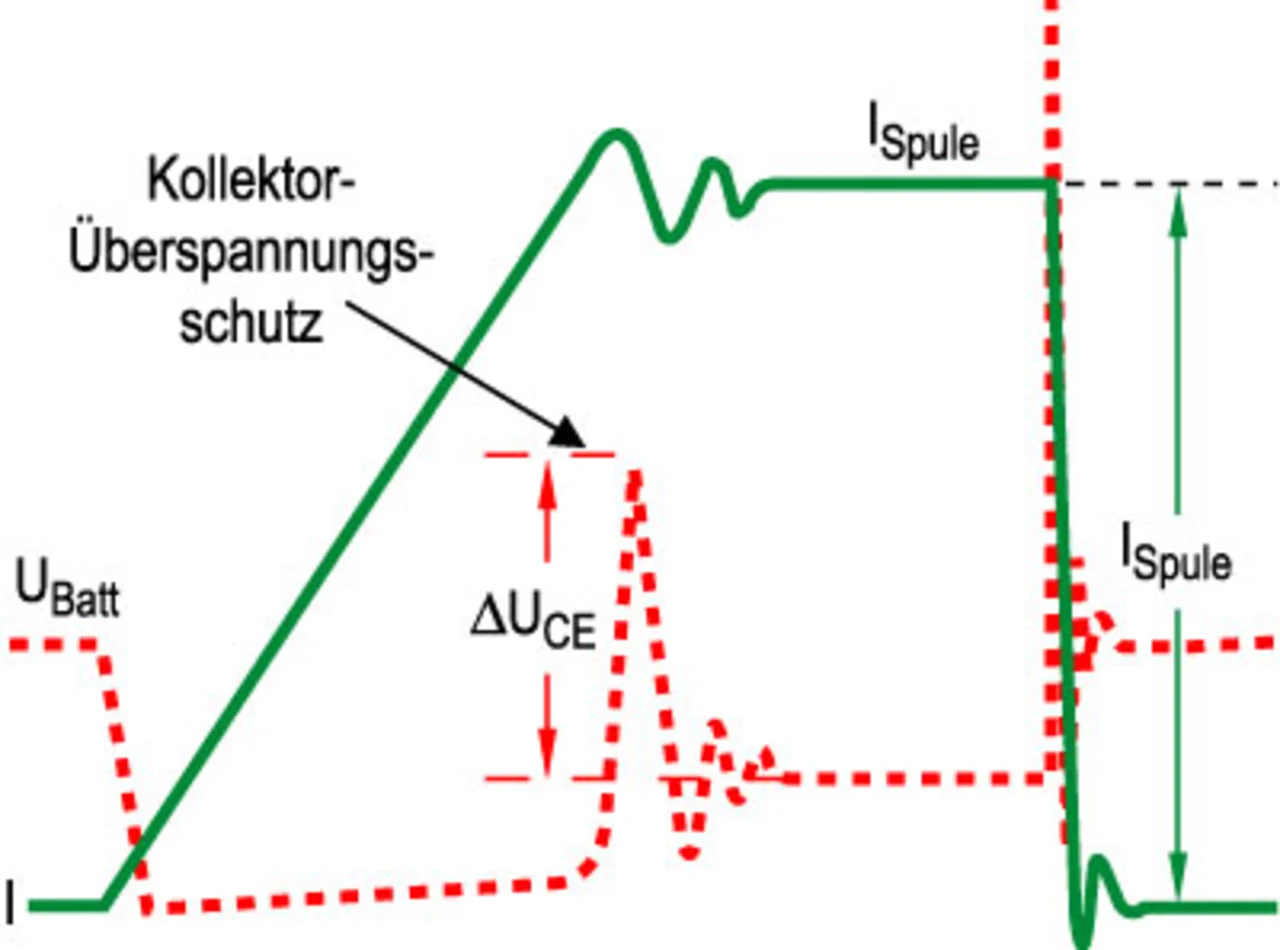

Um die unerwünschte Erzeugung von Zündfunken insbesondere bei einem Ansprechen der Strombegrenzung und des Überhitzungsschutzes zu verhindern, sorgen bestimmte eingebaute Schaltungen für eine Verbesserung der Sprungantwort. Durch Glätten der Kollektor-Oszillationen – mit Ausnahme der Abschaltphase – ist ein ordnungsgemäßer Betrieb des angesteuerten Zylinders gewährleistet (Bild 8).

Jobangebote+ passend zum Thema

Die Low-Cost-Implementierung in den ECP2M-FPGAs geschieht zum Teil mit Hilfe von Soft-IP. Der Physical Layer ist in Hardware implementiert, der Daten- und Transport-Layer in programmierbarer Logik. Für die Implementierung eines x1-Cores sind rund 5.000 LUTs (Look-up-Table) notwendig, der x4-Core verbraucht zirka 10.000 LUTs. Hierzu merkt Werner an: »Dies bedeutet, dass selbst beim ECP2M-20, dem kleinsten Baustein der ECP2M-Familie, noch genügend Logik vorhanden ist, um weitere Interfaces bzw. weitere Funktionen wie zum Beispiel Filter, Memory-Interfaces etc. zu implementieren.« So lassen sich beispielsweise problemlos noch DDR/2 Memory-Interfaces mit einer Übertragungsrate von bis zu 533MBit/s realisieren.

Der Vorteil einer FPGA-basierenden PCIe-Lösung gegenüber ASSPs liegt für Werner darin, dass der Entwickler das Interface so anpassen kann, dass sie seinen Anforderungen entsprechen, ohne dass zusätzliche Bausteine notwendig sind. »Normalerweise sind bei ASSPs noch kleinere FPGAs erforderlich, um die Schnittstelle an die jeweiligen Bedürfnisse anzupassen, auch wenn der PCI-e ein eingefahrener Standard ist«, erklärt Werner weiter. Und die Kosten sind durchaus konkurrenzfähig. So liegt der Preis für eine Low- Cost-Lösung mit dem kleinsten Baustein der ECP2M-Familie bei hohen Stückzahlen im 11-Dollar- Bereich, »was sehr konkurrenzfähig gegenüber den ASSPs sowie anderen programmierbaren Lösungen ist«, so Werner weiter.

Ein weiterer Vorteil der Low-Cost-Lösung von Lattice besteht darin, dass der Anwender den Programmierstrom mit einem 128-Bit-AES verschlüsseln kann. Werner meint dazu: »Diese Möglichkeit schützt das Know-how des Entwicklers und verhindert eine ungewollte Überproduktion des Endprodukts. Denn der Auftragsfertiger kann nur so viele Boards bestücken, wie ihm der Auftraggeber FPGAs mit dem richtigen Schlüssel zur Verfügung stellt.«

Da auch Lattice eine Komplettlösung anbietet, stehen dem Entwickler neben den Bausteinen und den IP-Cores zum Beispiel auch PCI-Express-Schulungen offen, die Lattice über seinen Schulungspartner E-Vision Systems anbietet (zwei Tage für 890 Dollar). Darüber hinaus steht Unterstützung beim High-Speed-Board-Layout über den Lattice-Partner TietoEnator zur Verfügung. »Um unsere Kunden auf breiter Basis zu informieren, wie sie die IP-Cores in unsere Bausteine implementieren können und was sie sonst noch bei PCIe beachten sollten, halten wir regelmäßig Seminare mit unseren Partnern E-Vison, TietoEnator und LeCroy ab. Bei diesen kostenlosen Seminaren zeigen wir den kompletten Design Flow – von der Konfiguration bis zur Implementierung.«

| Dipl.-Ing. Giovanni Luca Torrisi trat 1995 bei STMicroelectronics ein. Als IC-Designer arbeitete er im Bereich Power Electronic speziell an AC/AC-Wandlern und elektronischen Zündungen. Auf diesen Gebieten hält er mehrere Patente. 2002 wechselte er zum Technical Marketing Team und leitet jetzt eine Gruppe, die japanische und US-amerikanische Händler betreut. |

| Dipl.-Ing.Doriana Montella studierte Elektronik an der Universtät Catania auf Sizilien. Nach dem Diplom im Jahre 1999 begann sie bei STMicroelectronics als Product Engineer in der PMOS & IBGT Product Group. Zu ihren Aufgaben zählte das Testen der PMOS-FETs und IGBTs sowie die Überführung der Prozesstechnologie in die Serienfertigung. Seit 2002 arbeitet sie im technischen Marketing der Automotive Marketing Group. |

- PCI Express als Hard- und Soft-IP

- Steigen die Preise für FPGAs?

- PCI Express als Hard- und Soft-IP

- PCI Express als Hard- und Soft-IP