Hardware-Debugging

Low-Power-Designs unter der Lupe

Fortsetzung des Artikels von Teil 4

Low-Power-Designs unter der Lupe

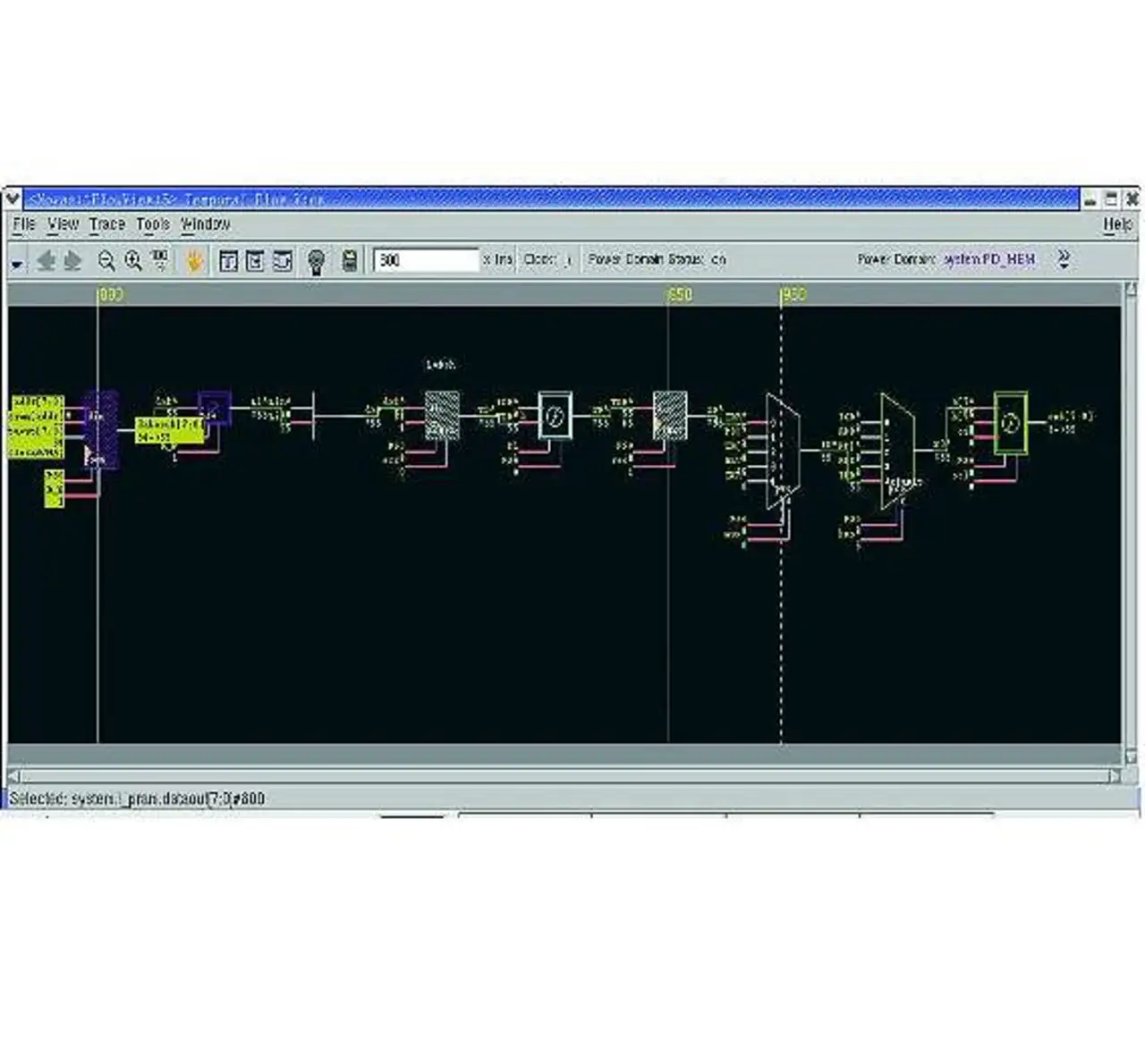

■■ Eine Möglichkeit zur Anzeige des gesamten Signalpfads, auch wenn die Grenzen von Spannungsinseln überschritten werden, damit Retention-, Isolations- oder Pegelumsetzersignale einfach als solche identifiziert werden können. Dabei lässt sich die Darstellung der Pfade um passende Informationen zu den Spannungsinseln und der Power-relevanten Logik ergänzen, um ein weitergehendes Debuggen zu ermöglichen (Bild 4).

■■ Eine Annotation von Power-Modi in den RTL-, Waveform-, Schematic- und UPF/CPF-Power-Anzeigen, sodass der Anwender die dynamischen Power-Modi und -Stati in jeder Darstellungsart untersuchen kann. Diese Funktion unterstützt den Ingenieur bei der Entscheidung, was er als Nächstes debuggen soll.

■■ Eine automatische Lokalisierung des Ursprungs eines fehlerhaften Wertes entweder im RTL- oder im CPF/UPF-Code. Damit können Anwender Signale über die Grenzen hinweg in den RTL- und CPF/UPF-Code zurückverfolgen.

Die Debug-Lösung muss zudem erweiterbar sein. Dies ist erforderlich, um neue Debug-Funktionen (z.B. automatische Lokalisierung von Treibern/Lasten über die Grenzen von CPF/UPF- und RTLCode hinweg oder Annotation von Power-Modi zu jeder beliebigen Simulationszeit) in die Debug-Umgebung integrieren und Standarddarstellungsformen um spezielle Anzeigemöglichkeiten für Power-Aspekte ergänzen zu können. Natürlich sind zusätzliche Funktionen denkbar und wünschenswert, wie Funktionen zur Anzeige von Powerrelevanten Schaltkreisen (etwa Retention-Register einschließlich der Save-/Restore-Signale) und zur automatischen Zurückverfolgung von Power-Steuerungssignalen in einer »Temporal Flow«-Ansicht.

Jobangebote+ passend zum Thema

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe