Hardware-Debugging

Low-Power-Designs unter der Lupe

Fortsetzung des Artikels von Teil 2

Low-Power-Designs unter der Lupe

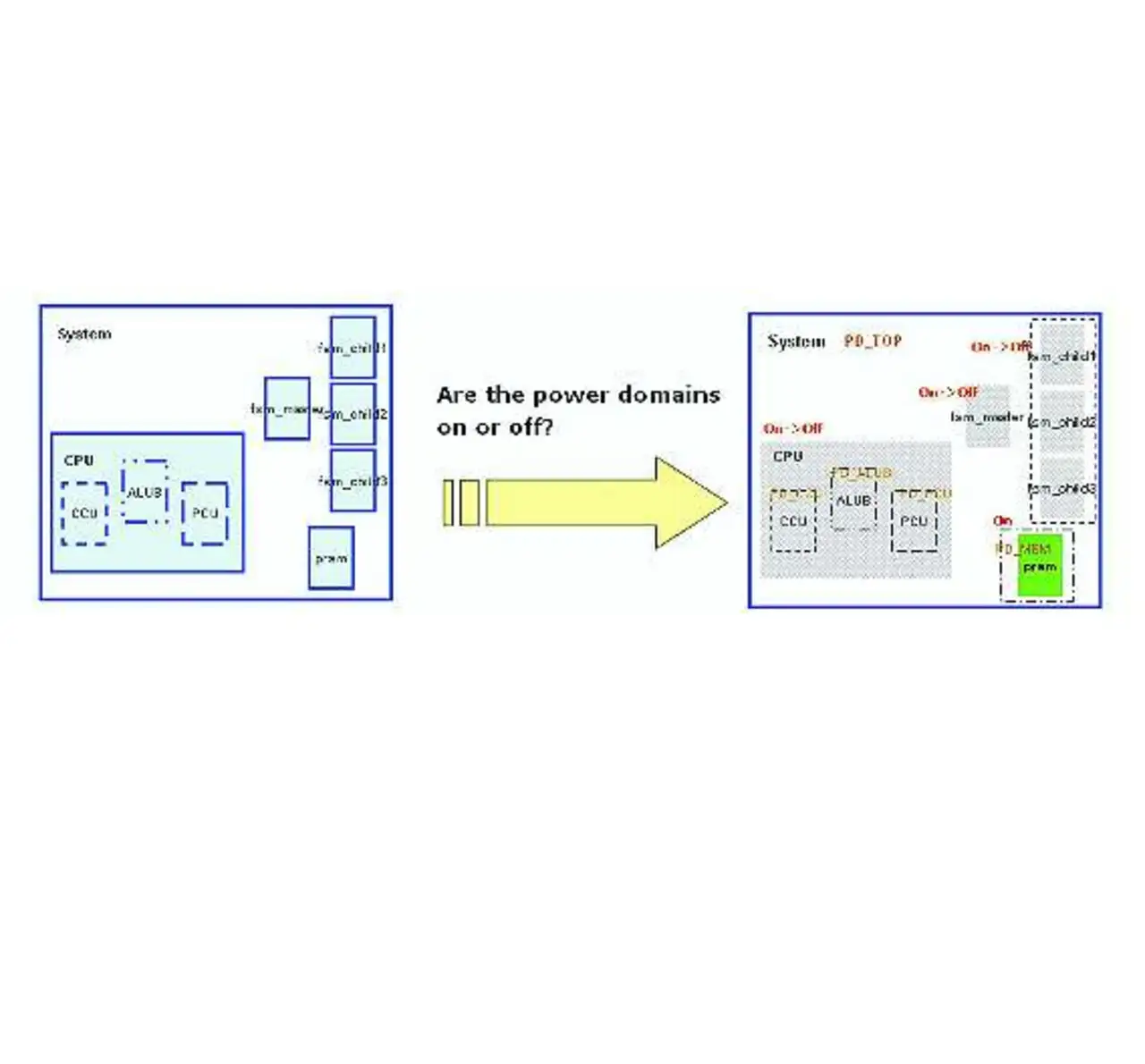

Als nächstes muss der Ingenieur herausfinden, wie sich die unterschiedlichen Modi der Spannungsinsel verhalten sollen. So ist im betrachteten Beispiel die Spannungszufuhr im Block »pram« eingeschaltet, während die anderen Blöcke ausgeschaltet sind (Bild 2). Da der Block »pram« eingeschaltet ist, während der treibende Block (CPU) ausgeschaltet ist, will der Entwickler eventuell eruieren, ob ein Isolationsgatter zwischen den Spannungsinseln eingefügt wurde, um den an den Block »pram« übergebenen Signalwert bei einem Abschalten des CPU-Blocks für die nachfolgenden Schaltungsteile im Pfad zu erhalten. Für RTL-Ingenieure ist dieser Prozess – der entsprechend mit allen Blöcken und Subblöcken mit ihren zugehörigen Spannungsinseln und Power-Modi durchlaufen werden muss – bisher eine echte Herausforderung, die viel Zeit kostet.

Die Fehlerursache finden

Wenn Fehler in einem Design gefunden und behoben werden müssen, bei dem es auf die Power-Merkmale ankommt, liegt die größte Herausforderung darin, die Ursache des Fehlers zu finden. Schließlich können sowohl die RTL-Funktionen als auch die in der Power-Spezifikation beschriebenen Power-Elemente der Grund dafür sein. Wenn etwa der Wert X in einem Signalverlauf während einer Simulation auftritt, die Power-Aspekte berücksichtigt, könnte dieser Signalwert »Stromversorgung aus« bedeuten, aber genauso gut auf ein Problem hinweisen, hervorgerufen durch einen strukturellen Fehler, wie eine vergessene Isolationszelle oder einen Steuersequenzfehler (beispielsweise eine fehlerhafte Speicher- oder Wiederherstellungssequenz). Die Anzeige des Wertes X in einer Waveform-Darstellung liefert folglich keine Informationen über den Ursprung oder die Ursache eines Fehlers. Um den Auslöser ausfindig machen zu können, muss der Ingenieur den Signalwert X daher sowohl im RTL-Quellcode als auch in den Power-Spezifikationsdateien zurückverfolgen. Der Einsatz von Power-Standardbeschreibungssprachen zu einem frühen Zeitpunkt des Designprozesses – und insbesondere im Verifikationsprozess – bietet unbestreitbare Vorteile. Allerdings erschwert er das Debuggen des Designs, sodass eine Debug-Lösung benötigt wird, die Power-Aspekte berücksichtigt und das Verständnis der geplanten Power-Merkmale erleichtert beziehungsweise die dafür erforderliche Zeit verkürzt. Zudem muss sie den Prozess der Zurückverfolgung, die Visualisierung und die Identifikation der Ursache von Power-Fehlern automatisieren. Damit sichergestellt ist, dass der RTL-Ingenieur den Code, der die Power-Merkmale beschreibt, in allen Details versteht, sollte es ihm diese Lösung mindestens ermöglichen, die Spannungsinseln eines Blocks und die damit assoziierten Power-Modi zu ermitteln.

Jobangebote+ passend zum Thema

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe

- Low-Power-Designs unter der Lupe